Any revealing of identification, appeal to evaluator and /or equations written eg, 42+8 = 50, will be treated as malpractice. Important Note: 1. On completing your answers, compulsorily draw diagonal cross lines on the remaining blank pages.

## Third Semester B.E. Degree Examination, Dec.2023/Jan.2024 **Analog Electronics**

Time 13 hrs

Max. Marks: 80

Note: Answer any FIVE full questions, choosing ONE full question from each module.

## Module-1

Derive an expression for A<sub>v</sub>, Z<sub>i</sub> and Z<sub>0</sub> for CE-fixed bias using r<sub>e</sub>-equivalent model.

(08 Marks)

Define h-parameters and derive h-parameters model of CE-BJT.

(08Marks)

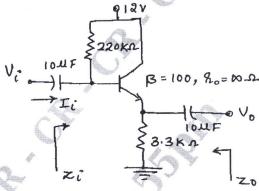

For the emitter-follower network of Fig.Q2(a). Determine: i) re ii) Z<sub>i</sub> iii)  $Z_0$ iv) A<sub>V</sub>. (08 Marks)

Fig.Q2(a)

With a neat circuit explain the high frequency transistor small-signal AC equivalent circuit. (08 Marks)

Module-2

- With circuit diagram of JFET small signal model, determine  $g_m$  and  $r_d$ . (08 Marks) 3

- For the JFET common-source amplifier using fixed-bias configuration. Derive expressions for  $Z_i$ ,  $Z_0$  and Av using AC equivalent circuit. (08 Marks)

OR

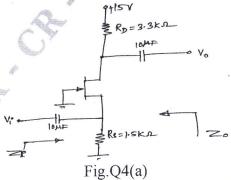

For the JFET common-gate configuration shown below, calculate Z<sub>i</sub>, Z<sub>0</sub> and Av. (08 Marks)

With neat diagram, explain construction of n-channel JFET, and also draw its (08 Marks) characteristics.

## Module-3

5 a. Prove that

Input capacitance is  $C_{Mi} = (1 - A_v)C_f$  and

Output capacitance is  $C_{MO} = \left(1 - \frac{1}{A_v}\right)C_f$  using miller effect.

(08 Marks)

b. Describe the factors that affect the low frequency response of a BJT-CE amplifier. (08 Marks)

OR

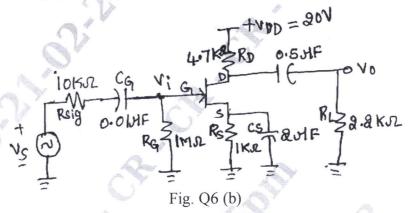

- 6 a. Explain high frequency response of FET amplifier and derive expression for cut off frequencies, defined by input and output circuits (f<sub>Hi</sub> and f<sub>Ho</sub>). (08 Marks)

- b. Determine the lower cut off frequency for the network shown in Fig. Q6 (b), using following parameters  $g_m = 2$  ms,  $r_d = \infty \Omega$ ,  $I_{DSS} = 8$  mA,  $V_P = -4V$ ,  $V_{DD} = 20$  V. (08 Marks)

Module-4

- 7 a. Mention the types of feedback connections. Draw their block diagrams indicating input and output signal. (08 Marks)

- b. With a neat circuit diagram, explain the working principle of FET phase-shift oscillator, with relevant equations. (08 Marks)

OR

- 8 a. What are the effects of negative feedback in an amplifier? Show how bandwidth of an amplifier increases with negative feedback. (06 Marks)

- b. With a neat circuit and waveforms, explain the working operation of UJT relaxation oscillator. (05 Marks)

- c. Determine the voltage gain, input and output impedance with feedback for voltage series feedback having A = -100,  $R_i = 10 \text{ K}\Omega$  and  $R_0 = 20 \text{ k}\Omega$  for feedback factor  $\beta = -0.1$ .

(05 Marks)

## Module-5 CMRIT LIBRARY BANGALORE - 560 037

9 a. Explain series – fed class – A power amplifier. Show that its maximum conversion efficiency is 25%. (08 Marks)

b. Explain with circuit diagram the operation of Class-B push-Pull amplifier using complementary—symmetry transistor pair. Also mention advantages and disadvantages of the circuit.

(08 Marks)

OR

- 10 a. An ideal class –B push-pull power amplifier with input and output transformers has  $V_{CC}=20V,\ N_2=2N_1$  and  $R_L=20\Omega.$  The transistors has  $h_{fe}=20$ . Let the input be sinusoidal. For the maximum output signal at  $V_{CE(P)}=V_{CC}$ , determine :

- i) The output signal power

- ii) The collector dissipation in each transistor CMRIT LIBRARY

- iii) Conversion efficiency.

BANGALORE 560 0

b. The following distortion readings are available for a power amplifier,  $D_2=0.2,\,D_3=0.02,\,D_4=0.06,\,$  with  $I_1=3.3A$  and  $R_C=4\Omega.$

- i) Calculate the total harmonic distortion

- ii) Determine the fundamental power component

- iii) Calculate the total power.

(08 Marks)

(08 Marks)