# Third Semester B.E. Degree Examination, Dec.2023/Jan.2024 **Digital System Design** MAR

Time: 3 hrs.

Max. Marks: 100

Note: Answer any FIVE full questions, choosing ONE full question from each module.

## Module-1

Define combinational circuits, POS and SOP with an example. (06 Marks) 1

Draw the truth table for three inputs with output high when MSB and LSB the input is high. Also write the simplified switching equation for the output and realize the logic circuit for (06 Marks) the simplified expression using basic gates.

c. Simplify the logic expression  $Y(A, B, C, D, E) = \Sigma m(5, 7, 13, 15, 21, 24, 25, 26, 27) + d(23, 25, 26, 27) + d(23, 26, 27$

29, 31). Also write the logic circuit for the simplified expression using NAND gate.

(08 Marks)

- Convert the following expression into its canonical form. 2

- $Y = (A + \overline{B}C)$

$Y = AB\overline{C} + AD$

(06 Marks)

Simplify by using K-map  $Y = \pi M(0, 4, 5, 7, 8, 9, 11, 12, 13, 15)$  and obtain the logical expression in form of POS.

Simplify the following Boolean function using QM method  $F(A, B, C, D) = \Sigma(0, 2, 3, 7, 8, 0)$ 10, 12, 13).

(08 Marks)

# Module-2

- Design a combinational circuit to find the 9's complement of a single digit BCD number (06 Marks) realize the logic circuit using gates.

- What is a multiplexer? Design a 4:1 MUX with active low enable and also write its symbol (08 Marks) with truth table.

- Implement the multiple function  $f_1 = \Sigma m(1, 4, 5, 7)$  and  $f_2 = \pi m(2, 3, 6)$ . Using IC74LS138 (06 Marks) and external gates. Assume both f1 and f2 will have three inputs.

### OR

- What is the need for look ahead carry generator and also draw the logic diagram of look (08 Marks) ahead carry generator with necessary logical expression.

- Draw the truth table of 2 bit magnitude comparator and write the logic diagram for the same (06 Marks) with minimum number of gates.

- A combinational circuit is defined by the function  $f_1 = \Sigma m(3, 5, 7)$  and  $f_2 = \Sigma m(4, 5, 7)$ implement the circuit with PLA having three inputs, three product terms and two outputs. (06 Marks)

Module-3

- Explain the working at SR Latch switch debouncer and also its need. (06 Marks)

- Draw the logic diagram of gated D latch using NAND gates and explain its working with (08 Marks) truth table.

- Draw the output waveform for the following Latch for input waveform shown in Fig Q5(c)

|   | Fi | g Q5(c) |    |  | (06 N | Marl           | ks) |

|---|----|---------|----|--|-------|----------------|-----|

| R |    |         | _/ |  |       | and the second |     |

|   |    |         |    |  |       |                |     |

| S |    |         | 7  |  |       | 11.5           |     |

- What are the limitation of SR flip flop and explain how it can be eliminated in OK flip-flop, (08 Marks) explain with necessary logic diagram.

- Draw the logic diagram of 4 bit shift register with four D flip flops and four 4 × 1 multiplexer with selection inputs SI and SO the register should operate as follows:

|   | $S_1$ | $S_0$               | Operation  |  |

|---|-------|---------------------|------------|--|

|   | 0     | 0                   | Hold       |  |

| 1 | 0     | 1                   | Compliment |  |

|   | 1     | 0                   | Clear to 0 |  |

| 1 | 1     | 1 1 Load parallel d |            |  |

(12 Marks)

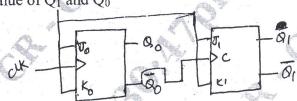

For the ripple counter shown in Fig Q7(a) draw the timing diagram for eight clock pulses (07 Marks) and also indicate the value of Q1 and Q0

Fig Q7(a)

- Draw the 3 bit synchronous binary up counter and explain its working with timing diagram (07 Marks) use JK flip-flop. (06 Marks)

- Explain the Moore and Melay model with necessary block diagram.

Design a synchronous MOD 6 counter using clocked D flip-flops.

(10 Marks)

Design a synchronous counter using JK flip-flip to count the sequence 0, 1, 2, 4, 5, 6, 0, 1, 2. (10 Marks) Draw state diagram and state table.

Module-5

- Design a sequence detector that produces an output 1 whenever the non overlapping 9 (10 Marks) sequence 101101 is detected.

- Explain iterative circuits use in comparator with logical diagram.

(10 Marks)

OR

BANGALORE - 560 037

Design a logic circuit to detect the sequence 1101 using Moore model use D flip-flop. 10

(10 Marks)

Draw the flow chart for performing the binary division operation and explain how division is performed using division algorithm given dividend = 1010 Division = 11. (10 Marks)