# Department of ISE Internal Assessment Test 1 – Dec. 2023 Evaluation scheme

| Sub:  | Digital Desig                                                                                                                                                                                                                                                                                          | n and Con                                                                                        | nputer Org                                      | anization       |      | Sub<br>Code:   | BCS302            | Branch: | ISE | 1       |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|-------------------------------------------------|-----------------|------|----------------|-------------------|---------|-----|---------|

| Date: | 18.12.2023                                                                                                                                                                                                                                                                                             | Duration:                                                                                        | 90 min's                                        | Max<br>Marks:   | 50   | Sem/Sec        | 03/ A,B,C         |         |     | OBE     |

|       |                                                                                                                                                                                                                                                                                                        | Answ                                                                                             | er any FIV                                      | E FULL QUI      | ESTI | ONS            |                   | MARK    | СО  | RB<br>T |

| 1(a)  | Demonstrate th                                                                                                                                                                                                                                                                                         | e validity of                                                                                    | the followin                                    | g identities by | mean | s of truth tab | les               | S<br>4  | CO1 |         |

|       | (i)x + yz = (x - Tr) $(ii) x(y + z) = x$                                                                                                                                                                                                                                                               | + y )( x + z )<br>uth Table (2                                                                   | 2)                                              | <i>g</i> ,      |      |                |                   |         |     |         |

|       | 1(b) Solve the following Boolean expressions to a minimum number of literals. Also draw logic diagrams of the circuits that implement the original and simplified expressions  (i)(x + y) (x + y')  Simplification (2)  Logic Diagram (1)  (ii)xyz + x'y + xyz'  Simplification (2)  Logic Diagram (1) |                                                                                                  |                                                 |                 |      |                | 6                 | CO1     | L3  |         |

| 2     |                                                                                                                                                                                                                                                                                                        |                                                                                                  |                                                 |                 |      |                | 10                | CO1     | L2  |         |

| 3(a)  | Simplify the f<br>A'B'C'D + A<br><b>K-n</b>                                                                                                                                                                                                                                                            | ollowing B<br>AB'D + A'E<br>nap (4)                                                              | oolean expr                                     | essions, using  |      |                | aps:              | 5       | CO1 | L3      |

|       | Solve the folloand then expre<br>F(A,B,C,D) =<br>d(A,B,C,D) =<br><b>K-n</b><br>Sim                                                                                                                                                                                                                     | owing Bool<br>ess the simple $\Sigma(0, 6,8,13)$<br>$\Sigma(2, 4, 10)$<br>map (3)<br>aplified SO | ean function<br>olified funct<br>3,14)<br>P (1) | -               |      |                | are conditions d, | 5       | CO1 | L3      |

| 4(a)  | Simplified POS (1)  (a) Model the multiple-level NOR circuit for the following expression: CD(B + C)A + (BC' + DE')  Logic Diagram with basic gates (2)  Logic Diagram with only NOR universal gate(3)                                                                                                 |                                                                                                  |                                                 |                 |      |                | 5                 | CO1     | L3  |         |

| 4(b)  | 4(b) Present the multiple-level NAND circuit for the following expression: w(x + y + z) + xyz  Logic Diagram with basic gates (2)  Logic Diagram with only NAND universal gate(3)                                                                                                                      |                                                                                                  |                                                 |                 |      |                |                   | 5       | CO1 | L3      |

| 5     | Design a 3-bit<br><b>Trut</b> l                                                                                                                                                                                                                                                                        |                                                                                                  | combinatio                                      |                 | ng 2 | bit subtracto  | ors               | 10      | CO2 | L3      |

|      | K-Map for Difference and Borrow (2) Simplified expression for Difference and Borrow (2) Logic Diagram using Half subtractor(3)                  |   |     |    |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------|---|-----|----|

| 6(a) | Discuss the combinational circuit that decodes 3 input variables?  Truth Table of 3:8 decoder (2)  K-Map for 3:8 decoder (2)  Logic Diagram (1) | 5 | CO2 | L2 |

| 6(b) | Discuss the combinational circuit that encodes 4 input variables?  Truth Table of 4:2 encoder (2)  K-Map for 4:2 encoder (2)  Logic Diagram (1) | 5 | CO2 | L2 |

CCI CI HOD

## <u>Department of ISE</u> <u>Internal Assessment Test 1 – Dec. 2023</u> IAT-1 solution

## 1(a) Demonstrate the validity of the following identities by means of truth tables (i)x + yz = (x + y)(x + z)

| xyz   | x + yz | (x+y) | (x+z) | (x+y)(x+z) |

|-------|--------|-------|-------|------------|

| 000   | 0      | 0     | 0     | 0          |

| 001   | 0      | 0     | 1     | 0          |

| 010   | 0      | 1     | 0     | 0          |

| 0 1 1 | 1      | 1     | 1     | 1          |

| 100   | 1      | 1     | 1     | 1          |

| 101   | 1      | 1     | 1     | 1          |

| 110   | 1      | 1     | 1     | 1          |

| 1 1 1 | 1      | 1     | 1     | 1          |

$$(ii) x(y + z) = xy + xz$$

| xyz   | x(y+z) | xy | xz | xy + xz |

|-------|--------|----|----|---------|

| 000   | 0      | 0  | 0  | 0       |

| 001   | 0      | 0  | 0  | 0       |

| 010   | 0      | 0  | 0  | 0       |

| 0 1 1 | 0      | 0  | 0  | 0       |

| 100   | 0      | 0  | 0  | 0       |

| 101   | 1      | 0  | 1  | 1       |

| 1 1 0 | 1      | 1  | 0  | 1       |

| 111   | 1      | 1  | 1  | 1       |

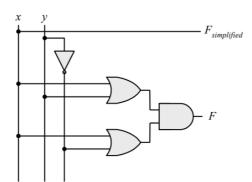

## 1(b) Solve the following Boolean expressions to a minimum number of literals. Also draw logic diagrams of the circuits that implement the original and simplified expressions (i)(x + y) (x + y)

$$= x + yy'$$

=  $x(x + y') + y(x + y')$

$$= xx + xy' + xy + yy'$$

$= \mathbf{x}$

Dr.Ciyamala Kushbu S, AP/ISE

2 Explain the Boolean theorems and postulates in detail

| S.No | •                   | AND property                                                                                     | OR Property                                                                                                           |

|------|---------------------|--------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|

| 1    | Identity Law        | $ A.1 = A $ $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                              | A+0 = A                                                                                                               |

| 2    | Zero And<br>One Law | $A.0 = 0$ $\begin{array}{c cccc} A & 0 & A \cdot 0 \\ \hline 1 & 0 & 0 \\ 0 & 0 & 0 \end{array}$ | A+1 = 1                                                                                                               |

| 3    | Inverse Law         | $     \begin{array}{c cccc}                                 $                                    | $A+A' = 1$ $ \begin{array}{c cccc} A & A' & A + A' \\ \hline 1 & 0 & 1 \\ 0 & 1 & 1 \end{array} $                     |

| 4    | Idempotent Law      | $     \begin{array}{c cccc}                                 $                                    | $   \begin{array}{c cccc}     A + A & A \\ \hline     A & A & A + A \\     1 & 1 & 1 \\     0 & 0 & 0   \end{array} $ |

| 5  | Commutative<br>Law       | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                 | A+B = B+A                                                                  |

|----|--------------------------|-------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

| 6  | Associative Law          | $(A.B).C = A.(B.C)$ $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                             | $(A+B)+C = A+(B+C)$ $\begin{array}{ c c c c c c c c c c c c c c c c c c c$ |

| 7  | Absorption Law           | A(A+B) = A                                                                                            | A + A.B = A                                                                |

| 8  | Distribution Law         | $ A \cdot (B+C) = (A \cdot B) + (A \cdot C) $ $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$ | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                      |

| 9  | De<br>Morgan's Law       | $(A.B)' = A' + B'$ $\begin{array}{ c c c c c c c c c c c c c c c c c c c$                             | $(A+B)' = A'.B'$ $\begin{array}{ c c c c c c c c c c c c c c c c c c c$    |

| 10 | Double<br>Complement Law | $ \begin{array}{c cc} A & A' \\ \hline 1 & 0 \\ 0 & 1 \end{array} $                                   | (A')' = A $(A')'$ $1$ $0$                                                  |

3(a) Simplify the following Boolean expressions, using four-variable maps: A'B'C'D + AB'D + A'BC' + ABCD + AB'C

(c)

Solve the following Boolean function F, together with the don't-care conditions d, and then express the simplified function in SOP and POS form.

$$F(A,B,C,D) = \Sigma(0, 6,8,13,14)$$

$d(A,B,C,D) = \Sigma(2, 4, 10)$

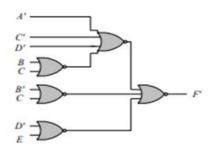

Model the multiple-level NOR circuit for the following expression: CD(B + C)A + (BC' + DE')**4(a)**

### Multi-level NOR:

$$\begin{split} F &= ACD(B+C) + (BC'+DE') \\ F' &= [ACD(B+C) + (BC'+DE')]' \\ F' &= [(A'+C'+D')'(B+C) + (B'+C)' + (D'+E)']' \\ F' &= [((A'+C'+D') + (B+C)')' + (B'+C)' + (D'+E)']' \\ F' &= [(A'+C'+D' + (B+C)')' + (B'+C)' + (D'+E)']' \end{split}$$

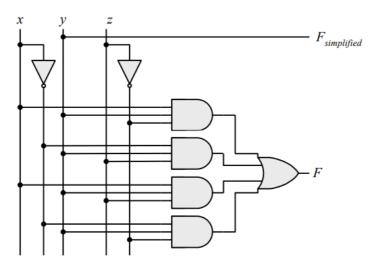

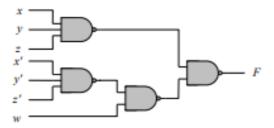

## 4(b) Present the multiple-level NAND circuit for the following expression: w(x + y + z) + xyz

$$F = w(x + y + z) + xyz$$

$F' = [w(x + y + z)]'[xyz]' = [w(x'y'z')']'(xyz)'$

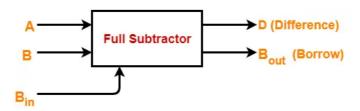

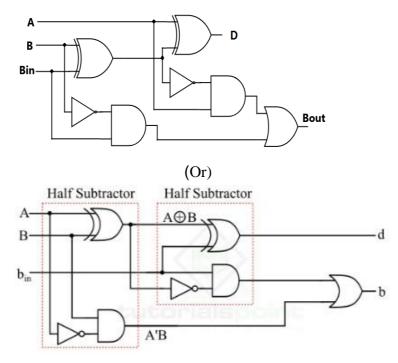

## 5 Design a 3-bit subtractor combinational circuit using 2 bit subtractors

A 3-bit subtractor or full subtractor is a combinational circuit that performs subtraction involving three bits, namely A (minuend), B (subtrahend), and Bin (borrow-in) . It accepts three inputs: A (minuend), B (subtrahend) and a Bin (borrow bit) and it produces two outputs: D (difference) and Bout (borrow out). The logic symbol and truth table are shown below.

## **Logic Symbol of Full subtractor**

**Truth Table of Full subtractor**

| A | В | B <sub>in</sub> | D | Bout |

|---|---|-----------------|---|------|

| 0 | 0 | 0               | 0 | 0    |

| 0 | 0 | 1               | 1 | 1    |

| 0 | 1 | 0               | 1 | 1    |

| 0 | 1 | 1               | 0 | 1    |

| 1 | 0 | 0               | 1 | 0    |

| 1 | 0 | 1               | 0 | 0    |

| 1 | 1 | 0               | 0 | 0    |

| 1 | 1 | 1               | 1 | 1    |

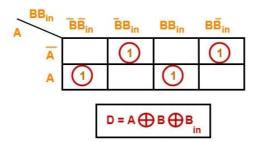

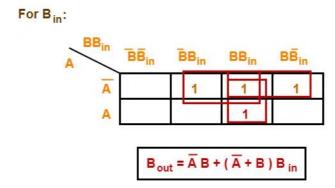

From the above truth table we can find the boolean expression using K-map

For D:

Dr.Ciyamala Kushbu S, AP/ISE

From the equation we can draw the Full-subtractor circuit as shown

Circuit Diagram for Full subtractor using Half-subtractors

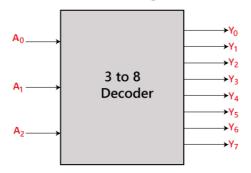

## 6(a) Discuss the combinational circuit that decodes 3 input variables?

**Decoder:**

The combinational circuit that change the binary information into  $2^N$  output lines is known as Decoders. The binary information is passed in the form of N input lines. The output lines define the  $2^N$ -bit code for the binary information. At a time, only one input line is activated for simplicity. The produced  $2^N$ -bit output code is equivalent to the binary information.

### 3:8 Decoder:

The 3 to 8 line decoder is also known as Binary to Octal Decoder. In a 3 to 8 line decoder, there is a total of eight outputs, i.e., Y0, Y1, Y2, Y3, Y4, Y5, Y6, and Y7 and three outputs, i.e., A0, A1, and A2. This circuit has an enable input 'E'. Just like 2 to 4 line decoder, when enable 'E' is set to 1, one of these four outputs will be 1. The block diagram and the truth table of the 3 to 8 line encoder are given below.

## **Block Diagram:**

## **Truth Table:**

| Enable | INPUTS         |                |                |                       |                       |                       | Out            | puts                  |                |                |                |

|--------|----------------|----------------|----------------|-----------------------|-----------------------|-----------------------|----------------|-----------------------|----------------|----------------|----------------|

| E      | A <sub>2</sub> | A <sub>1</sub> | A <sub>0</sub> | <b>Y</b> <sub>7</sub> | <b>Y</b> <sub>6</sub> | <b>Y</b> <sub>5</sub> | Y <sub>4</sub> | <b>Y</b> <sub>3</sub> | Y <sub>2</sub> | Y <sub>1</sub> | Y <sub>0</sub> |

| 0      | х              | х              | х              | 0                     | 0                     | 0                     | 0              | 0                     | 0              | 0              | 0              |

| 1      | 0              | 0              | 0              | 0                     | 0                     | 0                     | 0              | 0                     | 0              | 0              | 1              |

| 1      | 0              | 0              | 1              | 0                     | 0                     | 0                     | 0              | 0                     | 0              | 1              | 0              |

| 1      | 0              | 1              | 0              | 0                     | 0                     | 0                     | 0              | 0                     | 1              | 0              | 0              |

| 1      | 0              | 1              | 1              | 0                     | 0                     | 0                     | 0              | 1                     | 0              | 0              | 0              |

| 1      | 1              | 0              | 0              | 0                     | 0                     | 0                     | 1              | 0                     | 0              | 0              | 0              |

| 1      | 1              | 0              | 1              | 0                     | 0                     | 1                     | 0              | 0                     | 0              | 0              | 0              |

| 1      | 1              | 1              | 0              | 0                     | 1                     | 0                     | 0              | 0                     | 0              | 0              | 0              |

| 1      | 1              | 1              | 1              | 1                     | 0                     | 0                     | 0              | 0                     | 0              | 0              | 0              |

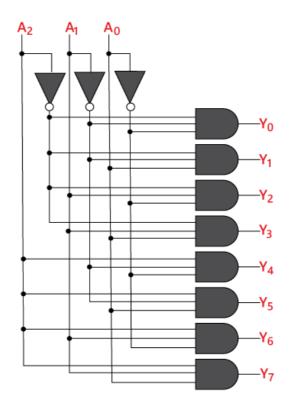

The logical expression of the term  $Y_0$ ,  $Y_1$ ,  $Y_2$ ,  $Y_3$ ,  $Y_4$ ,  $Y_5$ ,  $Y_6$ , and  $Y_7$  is as follows: (solve using **k** –map)

$$Y_0=A_0'.A_1'.A_2'$$

$Y_1=A_0.A_1'.A_2'$

$$Y_2=A_0'.A_1.A_2'$$

$$Y_3 = A_0.A_1.A_2'$$

$$Y_4 = A_0'.A_1'.A_2$$

$$Y_5=A_0.A_1'.A_2$$

$Y_6=A_0'.A_1.A_2$

$$Y_7 = A_0.A_1.A_2$$

Logical circuit of the above expressions is given below:

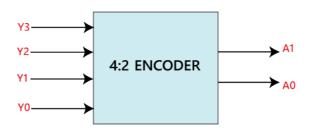

## 6(b) Discuss the combinational circuit that encodes 4 input variables?

#### **Encoders:**

The combinational circuits that change the binary information into N output lines are known as **Encoders**. The binary information is passed in the form of  $2^N$  input lines. The output lines define the N-bit code for the binary information. In simple words, the **Encoder** performs the reverse operation of the **Decoder**. At a time, only one input line is activated for simplicity. The produced N-bit output code is equivalent to the binary information.

### 4 to 2 line Encoder:

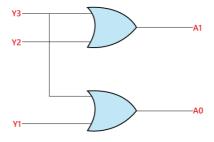

In 4 to 2 line encoder, there are total of four inputs, i.e.,  $Y_0$ ,  $Y_1$ ,  $Y_2$ , and  $Y_3$ , and two outputs, i.e.,  $A_0$  and  $A_1$ . In 4-input lines, one input-line is set to true at a time to get the respective binary code in the output side. Below are the block diagram and the truth table of the 4 to 2 line encoder.

## **Block Diagram:**

**Truth Table:**

|                       | IN             | OUT            | PUTS           |                |                |

|-----------------------|----------------|----------------|----------------|----------------|----------------|

| <b>Y</b> <sub>3</sub> | Y <sub>2</sub> | Υ <sub>1</sub> | Υ <sub>0</sub> | A <sub>1</sub> | A <sub>0</sub> |

| 1                     | 0              | 0              | 0              | 0              | 0              |

| 0                     | 1              | 0              | 0              | 0              | 1              |

| 0                     | 0              | 1              | 0              | 1              | 0              |

| 0                     | 0              | 0              | 1              | 1              | 1              |

The logical expression of the term A0 and A1 is as follows: (solve using k -map)

$$A_1 = Y_3 + Y_2$$

$$A_0 = Y_3 + Y_1$$

Logical circuit of the above expressions is given below: