Internal Assessment Test 3 – JULY 2024

|       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Assessment Te                                                                                                                                                                                                                               | st 3 –                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1                                                                                                                                                      |            |           |     |     |  |  |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-----------|-----|-----|--|--|

| Sub:  | MICROCON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | TROLLERS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                             |                                                                                       | Sub<br>Code:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | BCS402                                                                                                                                                 | Brai       | anch: CSE |     |     |  |  |

| Date: | 06/08/24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Duration:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 90 mins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Max Marks:                                                                                                                                                                                                                                  | 50                                                                                    | Sem /<br>Sec:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | IV Se                                                                                                                                                  | m A/I      | 3/C       |     | OBE |  |  |

|       | Answer any FIVE FULL Questions   MARKS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                             |                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | S                                                                                                                                                      | СО         | RBT       |     |     |  |  |

|       | Briefly explain processor.  IRQ and FIQ except. The ARM execution stage designing a decycles to complete An IRQ or FIQ procedure (provous 1. The processor interrupt being to 2. The previous 3. The pc is save 4. Interrupt/s and disabled in the type being raise 5. The processor slightly depend interrupts with exception is raise exception is raise                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | A processor of the pipeli terministic is ete the execu exception carded the interior changes traised.  mode's cpsred in the lrotare disabled—cpsr. This is d. or branches to ing upon the an example, sed, and the sed.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | y occur who will continue before had need to be the process of the process of the new interpretation of the new interpreta | en a specific in the executing the andling the intender since some cessor hardware to masked):  In the spsr of the errupt request request request request representation in the vector of the entry in the vector of the example shows what | terrupt- ne in e to go nest n new node. IRQ a interr tor tal aised. what              | ot mask is clurrent instruc- an important structions responsed through a second which interrupt request request to be. The process when an easy when easy when an easy when easy w | eared in the ction in the ant factor in equire more standard reflects the uest mode. Ceptions are of the same edure varies ustrate both hen an IRQ FIQ |            | [6]       | CO4 | L2  |  |  |

|       | What is interrupt Interrupt-driven val of time from instruction of a selection of a selection with the selection of a selection of a selection with the selection of a selection with the selection of a | embedded son an external specific interpolation on e system desirupt latency. It is is a nested interpolation of the same of task can into the entry servicine hod involves sof the same of task can into the entry task can i | ystems have interrupt requipt service a combinating to handle the interrupt ponse times.  main methoderrupt handle gan existing prioritization or lower prierrupt your handle the priority our handle the priority our handle the priority and the p | to fight a battle uest signal beir routine (ISR). on of hardware multiple simulates are not hand disto minimize er, which allowed interrupt on. You program fority than the inhandler. You the                                              | e withing rais and solution and solution interrulation in the interrulation received. | interrupt lated to the first software. Systems interrupt a timely manual latency. Interrupt conpt you are hereful to the conput of the conput  | stem architects sources and anner, then the The first is to occur troller to andling, so on                                                            | 3          | [4]       | CO4 | L1  |  |  |

| 2 a)  | Describe the fe RedBoot is a fi license with no (for instance, A Debugger (GD)  RedBoot suppo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | rmware tool or royalties or a RM, MIPS, B), as well as                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | developed by up front fees SH, and so can bootloade on features:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | y Red Hat. It is<br>. RedBoot is de<br>on). It provides<br>er. The RedBoo                                                                                                                                                                   | proviesigne<br>both of<br>t softw                                                     | d to execute<br>debug capab<br>ware core is                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | on different C<br>ility through C<br>based on a HA                                                                                                     | SNU<br>.L. | [6]       | CO4 | L2  |  |  |

|      | di d                                                                                                                        |     |     |    |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|----|

|      | col is used to communicate with the GNU Debugger (GDB). For Ethernet, TCP is used                                                                               |     |     |    |

|      | to communicate with GDB. RedBoot supports a range of network standards, such as                                                                                 |     |     |    |

|      | bootp, telnet, and tftp.                                                                                                                                        |     |     |    |

|      |                                                                                                                                                                 |     |     |    |

|      | Flash ROM memory management—provides a set of filing system routines that can                                                                                   |     |     |    |

|      | download, update, and erase images in flash ROM. In addition, the images can either                                                                             |     |     |    |

|      | be compressed or uncompressed.                                                                                                                                  |     |     |    |

|      | ■ Full operating system support—supports the loading and booting of Embedded Linux, Red Hat eCos, and many other popular operating systems. For Embedded Linux, |     |     |    |

|      | RedBoot supports the ability to define parameters that are passed directly to the kernel                                                                        |     |     |    |

|      | upon booting.                                                                                                                                                   |     |     |    |

| 2.b) | Illustrate the steps in the execution flow of sandstone code structure.                                                                                         | [4] | CO4 | L3 |

|      | Sandstone consists of a single assembly file. The file structure is broken down into a                                                                          |     |     |    |

|      | number of steps, where each step corresponds to a stage in the execution flow of Sandstone                                                                      |     |     |    |

|      |                                                                                                                                                                 |     |     |    |

|      | Step 1: Take the Reset Exception                                                                                                                                |     |     |    |

|      | Execution begins with a Reset exception. Only the reset vector entry is required in the default vector table.                                                   |     |     |    |

|      | Step 2: Start Initializing the Hardware                                                                                                                         |     |     |    |

|      | The primary phase in initializing hardware is setting up system registers. These registers                                                                      |     |     |    |

|      | have to be set up before accessing the hardware.                                                                                                                |     |     |    |

|      | Step 3: Remap Memory                                                                                                                                            |     |     |    |

|      | One of the major activities of hardware initialization is to set up the memory environment.                                                                     |     |     |    |

|      | Sandstone is designed to initialize SRAM and remap memory. This process occurs fairly                                                                           |     |     |    |

|      | early on in the initialization of the system.                                                                                                                   |     |     |    |

|      | Step 4: Initialize Communication Hardware                                                                                                                       |     |     |    |

|      | Communication initialization involves configuring a serial port and outputting a standard                                                                       |     |     |    |

|      | banner. The banner is used to show that the firmware is fully functional and memory has                                                                         |     |     |    |

|      | been successfully remapped.                                                                                                                                     |     |     |    |

|      | Step 5: Bootloader—Copy Payload and Relinquish Control                                                                                                          |     |     |    |

|      | The final stage involves copying a payload and relinquishing control of the pc over to the                                                                      |     |     |    |

|      | copied payload.                                                                                                                                                 |     |     |    |

| 3 a) | With a neat diagram explain the levels in memory hierarchy and the cache memory.                                                                                | [6] | CO5 | L2 |

| ] "" | with a near diagram explain the levels in memory metaterly and the eache memory.                                                                                | [٥] | 003 | L2 |

|      |                                                                                                                                                                 |     |     |    |

|      | Processor Register file Chip                                                                                                                                    |     |     |    |

|      | Tightly coupled wemory Level 1 cache Write buffer                                                                                                               |     |     |    |

|      | Main                                                                                                                                                            |     |     |    |

|      | Board DRAM                                                                                                                                                      |     |     |    |

|      | Flash and other board-level nonvolatile memory                                                                                                                  |     |     |    |

|      | Read path                                                                                                                                                       |     |     |    |

|      | Device Secondary Disk, tage, and network storage                                                                                                                |     |     |    |

|      | storage Write path                                                                                                                                              |     |     |    |

|      | Figure 12.1 Memory hierarchy.                                                                                                                                   |     |     |    |

|      |                                                                                                                                                                 |     |     |    |

|      |                                                                                                                                                                 |     |     |    |

|      | Level 1-Processor Core                                                                                                                                          |     |     |    |

|      | The innermost level of the hierarchy is at the processor core.                                                                                                  |     |     |    |

|      |                                                                                                                                                                 |     |     |    |

|      | • This memory is so tightly coupled to the processor that in many ways it is difficult to                                                                       |     |     |    |

|      | think of it as separate from the processor.                                                                                                                     |     |     |    |

|      |                                                                                                                                                                 |     |     |    |

|   | •                                                                                                                       | This memory is known as a register file. These registers are integral to the processor core and provide the fastest possible memory access in the system.                                |     |     |    |

|---|-------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|----|

|   | •                                                                                                                       | memory components are connected to the processor core through dedicated on-chip interfaces.                                                                                              |     |     |    |

|   | •                                                                                                                       | It is at this level we find tightly coupled memory (TCM) and level 1 cache.                                                                                                              |     |     |    |

| - | Level                                                                                                                   |                                                                                                                                                                                          |     |     |    |

|   | •                                                                                                                       | The primary level is the main memory. It includes volatile components like SRAM and DRAM, and nonvolatile components like flash memory.                                                  |     |     |    |

|   | •                                                                                                                       | The purpose of main memory is to hold programs while they are running on a system.                                                                                                       |     |     |    |

|   | •                                                                                                                       |                                                                                                                                                                                          |     |     |    |

| - | Layer                                                                                                                   | 3-secondary memory                                                                                                                                                                       |     |     |    |

| ; | storage                                                                                                                 | ext level is secondary storage—large, slow, relatively inexpensive mass e devices such as disk drives or removable memory. Also included in vel is data derived from peripheral devices. |     |     |    |

|   |                                                                                                                         | ribe the terms to measure the cache efficiency.                                                                                                                                          | [4] | CO5 | L4 |

| ŀ | There are two terms used to characterize the cache efficiency of a program: the cache hit rate and the cache miss rate. |                                                                                                                                                                                          |     |     |    |

|   | The hit rate is the number of cache hits divided by the total number of memory requests over a given time interval.     |                                                                                                                                                                                          |     |     |    |

| ĺ | The va                                                                                                                  | alue is expressed as a percentage:                                                                                                                                                       |     |     |    |

|   |                                                                                                                         | $hit \ rate = \left(\frac{cache \ hits}{memory \ requests}\right) \times 100$                                                                                                            |     |     |    |

| , |                                                                                                                         | iss rate is similar in form: the total cache misses divided by the total number of ry requests expressed as a percentage over a time interval. Note that the miss rate also              |     |     |    |

- i) Direct mapped Caches

- ii) Set Associative Caches

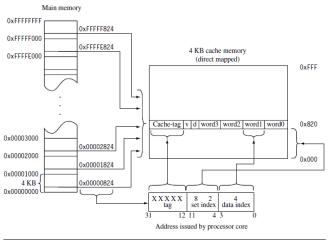

## i. Direct mapped Caches:

- In a direct-mapped cache each addressed location in main memory maps to a single location in cache memory.

- Since main memory is much larger than cache memory, there are many addresses in main memory that map to the same single location in cache memory.

- Figure 12.5 shows where portions of main memory are temporarily stored in cache memory.

- The figure represents the simplest form of cache, known as a direct-mapped cache.

- The figure shows this relationship for the class of addresses ending in 0x824.

Figure 12.5 How main memory maps to a direct-mapped cache

## Direct Mapping-Eviction & Thrashing

If valid data exists in this cache line but represents another address block in main memory, the entire cache line is evicted and replaced by the cache line containing the requested address. This process of removing an existing cache line as part of servicing a cache miss is known as eviction—returning the contents of a cache line to main memory from the cache to make room for new data that needs to be loaded in cache.

Direct-mapped caches are subject to high levels of thrashing—a software battle for the same location in cache memory.

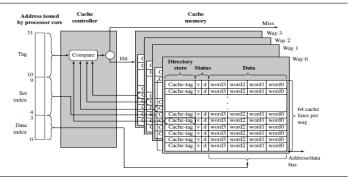

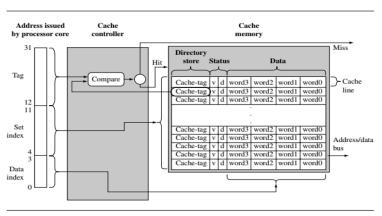

## Set Associative Caches

Some caches include an additional design feature to reduce the frequency of thrashing. This structural design feature is a change that divides the cache memory into smaller equal units, called ways.

the set index now addresses more than one cache line—it points to one cache line in each way. Instead of one way of 256 lines, the cache has four ways of 64 lines.

The four cache lines with the same set index are said to be in the same set, which is the origin of the name "set index."

The set of cache lines pointed to by the set index are set associative.

Two sequential blocks from main memory can be stored as cache lines in the same way or two different ways.

L2 CO<sub>5</sub>

The important thing to note is that the data or code blocks from a specific location in main memory can be stored in any cache line that is a member of a set.

The placement of values within a set is exclusive to prevent the same code or data block from simultaneously occupying two cache lines in a set.

Figure 12.7 A 4 KB, four-way set associative cache. The cache has 256 total cache lines, which are separated into four ways, each containing 64 cache lines. The cache line contains four ways.

5. a) Discuss the cache replacement and write policies that determine the operation of cache with a proper example.

[10]

CO5

L2

Cache Policy-Write Policy—Writethrough:

When the processor core writes to memory, the cache controller has two alternatives for its write policy.

The controller can write to both the cache and main memory, updating the values in both locations; this approach is known as writethrough.

Alternatively, the cache controller can write to cache memory and not update main memory, this is known as writeback or copyback.

When the cache controller uses a writethrough policy, it writes to both cache and main memory when there is a cache hit on write, ensuring that the cache and main memory stay coherent at all times.

Under this policy, the cache controller performs a write to main memory for each write to cache memory.

Because of the write to main memory, a writethrough policy is slower than a writeback policy.

Cache Policy-Write Policy-Writeback:

When a cache controller uses a writeback policy, it writes to valid cache data memory and not to main memory.

Consequently, valid cache lines and main memory may contain different data.

The cache line holds the most recent data, and main memory contains older data, which has not been updated.

When a cache controller in writeback writes a value to cache memory, it sets the dirty bit true. If the core accesses the cache line at a later time, it knows by the state of the dirty bit that the cache line contains data not in main memory.

If the cache controller evicts a dirty cache line, it is automatically written out to main memory. The controller does this to prevent the loss of vital information held in cache memory and not in main memory.

Cache Line Replacement Policies:

On a cache miss, the cache controller must select a cache line from the available set in cache memory to store the new information from main memory.

The cache line selected for replacement is known as a victim.

If the victim contains valid, dirty data, the controller must write the dirty data from the cache memory to main memory before it copies new data into the victim cache line.

The process of selecting and replacing a victim cache line is known as eviction.

The strategy implemented in a cache controller to select the next victim is called its replacement policy.

The replacement policy selects a cache line from the available associative member set.

ARM cached cores support two replacement policies, either pseudorandom or round-robin.

■ Round-robin or cyclic replacement simply selects the next cache line in a set to replace.

The selection algorithm uses a sequential, incrementing victim counter that increments each time the cache controller allocates a cache line.

When the victim counter reaches a maximum value, it is reset to a defined base value.

Pseudorandom replacement randomly selects the next cache line in a set to replace.

The selection algorithm uses a nonsequential incrementing victim counter.

In a pseudorandom replacement algorithm the controller increments the victim counter by randomly.