# CBCS SCHEME

Fifth Semester B.E. Degree Examination, June/July 2024 **Verilog HDL**

Max. Marks: 100

Note: Answer any FIVE full questions, choosing ONE full question from each module.

## Module-1

- (04 Marks) List the importance of HDL. 1

- Explain design flow for designing VLSI IC circuits with a neat flow chart. (10 Marks)

- Discuss the different levels of abstraction used in verilog modelling and write example in (06 Marks) each case.

### OR

- Describe the top down design approach with 4-bit ripple counter example. (12 Marks)

- What is the need of stimulus block in simulation? Discuss different techniques of applying (08 Marks) stimulus.

## Module-2

- List all the data types of verilog HDL. Explain any 4 with example. (10 Marks)

- Write a verilog description of SR latch and write a stimulus code, use \$monitor to display (06 Marks) the simulation time, inputs and outputs.

- Describe different methods of connecting ports to external signals. (04 Marks)

#### OR

- Write verilog statements to declare the following variables. a.

- i) Declare a 16-bit vector called addr

- ii) Declare a memory RAM with 1K bytes

- iii) Declare a constant port id = 5

- iv) Declare time variable T<sub>1</sub>. (04 Marks) (08 Marks)

- b. Discuss any 4 system tasks with example.

- c. Bring out differences between:

- ii) \$monitor iii) Sized and unsized data. (08 Marks) i) \$display

#### Module-3

- Design a 4-bit ripple carry adder using 1-bit full adder. (08 Marks) 5

- What is the output of the following expressions, given:

- a = 4' b1010 b = 4' b1011 c = 4' b110x

- a = = = 6ii)  $y = \wedge b$

- iii) y = a & b

- iv) y = b >>> 1

- v)  $y = \{2a[1], b, 11, c[3]\}$

- (06 Marks) vi)  $y = a \mid b$ .

- c. Write a verilog program to implement  $4 \times 1$  MUX using :

- i) Conditional operator

- ii) Data flow Boolean expressions. (06 Marks)

OR

- a. Derive Boolean expressions for 4-bit carry look ahead adder and also write the design (10 Marks) module.

- b. Design a 2 × 1 MUX by writing logic circuit using bufifo and bufifi for the following delay specification.

|          | Min | typ | Max |

|----------|-----|-----|-----|

| Rise     | 3   | 4   | 5   |

| Fall     | 6   | 7   | 9   |

| Turn off | 5   | 6   | 7   |

(04 Marks)

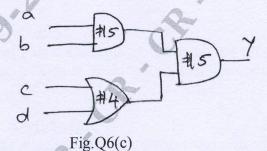

Write verilog module, test bench and waveform for the circuit shown in Fig.Q6(c). Assume

$$t = 0$$

,  $a = 0$ ,  $b = 0$ ,  $c = 0$ ,  $d = 0$

$t = 5$ ,  $a = 1$ ,  $b = 1$ ,  $c = 1$ ,  $d = 1$

$$t = 15$$

,  $a = 0$ ,  $c = 0$ .

(06 Marks)

Module-4

- Differentiate always initial blocking and on blocking statement. (08 Marks) 7

- Write a verilog program to call a function called calc parity which computes the parity of a (06 Marks) 32 – bit data [31:0] Data and display the parity.

- c. Explain the following control statements

- ii) for loop. i) case

(06 Marks)

OR

- Bring out differences between tasks and functions of verilog. (06 Marks)

- Write a verilog program for 1 × 4 demux considering 0, 1, x, z values for select inputs. (08 Marks)

- Explain the different event based timing control with example.

(06 Marks)

- Module-5

- Define the term logic synthesis. With a neat block diagram. Explain computer aided logic (08 Marks) synthesis process.

- Discuss conditional execution with an example.

(08 Marks)

Bring out difference between \$strobe and \$display BANGALORE - 560 037 (04 Marks)

- What will the following statements translate to when run on a logic synthesis tool? 10

- i) assign  $y = (a \& b) \mid (c \& d)$  where a, b, c, d are 2-bit vectors

- ii) if(s) out = i1;

else out = i0; (06 Marks)

Explain force and release procedural assignments with example.

(08 Marks)

Discuss any 4 system tasks related to files.

(06 Marks)

\* \* \* \*