| USN |  |  |  |  |  |

|-----|--|--|--|--|--|

|     |  |  |  |  |  |

## CMR INSTITUTE OF TECHNOLOGY

| Internal Assesment Test – I      |                                                                                   |                |              |                 |         |          |       |        |      |             |    |  |  |

|----------------------------------|-----------------------------------------------------------------------------------|----------------|--------------|-----------------|---------|----------|-------|--------|------|-------------|----|--|--|

| Sub: VLSI DESIGN & TESTING Code: |                                                                                   |                |              |                 |         |          |       |        |      | 21EC63      |    |  |  |

| Date:                            | Pate: 04.06.2024 Duration: 90 mins Max Marks: 50 Sem VI Branch                    |                |              |                 |         |          |       |        |      | ECE-A,B,C,D |    |  |  |

| Answer Any Five Questions        |                                                                                   |                |              |                 |         |          |       |        |      |             |    |  |  |

| Owastians                        |                                                                                   |                |              |                 |         |          |       |        |      |             | BE |  |  |

|                                  | Questions                                                                         |                |              |                 |         |          |       |        |      |             |    |  |  |

| 1.                               | Explain the oper                                                                  | ration of an n | -channel e   | nhancement r    | node N  | MOSFE    | T wit | n neat | [10] | CO1         | L1 |  |  |

| diagrams.                        |                                                                                   |                |              |                 |         |          |       |        |      |             |    |  |  |

|                                  | Derive the expre                                                                  | ession for dra | in to source | e current for a | ın n-cl | nannel N | MOSF  | ET in  |      | CO1         | L2 |  |  |

| 2. all three regions.            |                                                                                   |                |              |                 |         |          |       |        | [10] | COI         | LZ |  |  |

| 3.                               | Describe in detail about any five non-ideal L-V characteristics of MOS transistor |                |              |                 |         |          |       |        |      | CO1         | L2 |  |  |

| USN |  |

|-----|--|

|-----|--|

## **CMR INSTITUTE OF TECHNOLOGY**

|                                                                                   | Internal Assessment Test – I           |                |            |               |        |            |        |           |       |             |    |  |  |  |

|-----------------------------------------------------------------------------------|----------------------------------------|----------------|------------|---------------|--------|------------|--------|-----------|-------|-------------|----|--|--|--|

| Sub: VLSI DESIGN & TESTING Code:                                                  |                                        |                |            |               |        |            |        |           | 21EC  | 21EC63      |    |  |  |  |

| Date:                                                                             | 04.06.2024                             | Duration:      | 90<br>mins | Max<br>Marks: | 50     | Sem        | VI     | Branch    | ECE-  | ECE-A,B,C,D |    |  |  |  |

|                                                                                   | Answer Any Five Questions              |                |            |               |        |            |        |           |       |             |    |  |  |  |

| Questions                                                                         |                                        |                |            |               |        |            |        |           |       |             | BE |  |  |  |

|                                                                                   |                                        |                | Marks      | СО            | RBT    |            |        |           |       |             |    |  |  |  |

| Explain the operation of an n-channel enhancement mode MOSFET with neat diagrams. |                                        |                |            |               |        |            |        |           |       | CO1         | L1 |  |  |  |

| Derive the expression for drain to source current for an n-channel MOSFET         |                                        |                |            |               |        |            |        |           | F1.01 | CO1         | L2 |  |  |  |

| 2.                                                                                | 2.   in all three regions.   [10]   22 |                |            |               |        |            |        |           |       |             |    |  |  |  |

| 3.                                                                                | Describe in det                        | tail about any | five non-i | deal I-V ch   | aracte | ristics of | MOS tr | ansistor. | [10]  | CO1         | L2 |  |  |  |

| USN |  |  |  |  |  |

|-----|--|--|--|--|--|

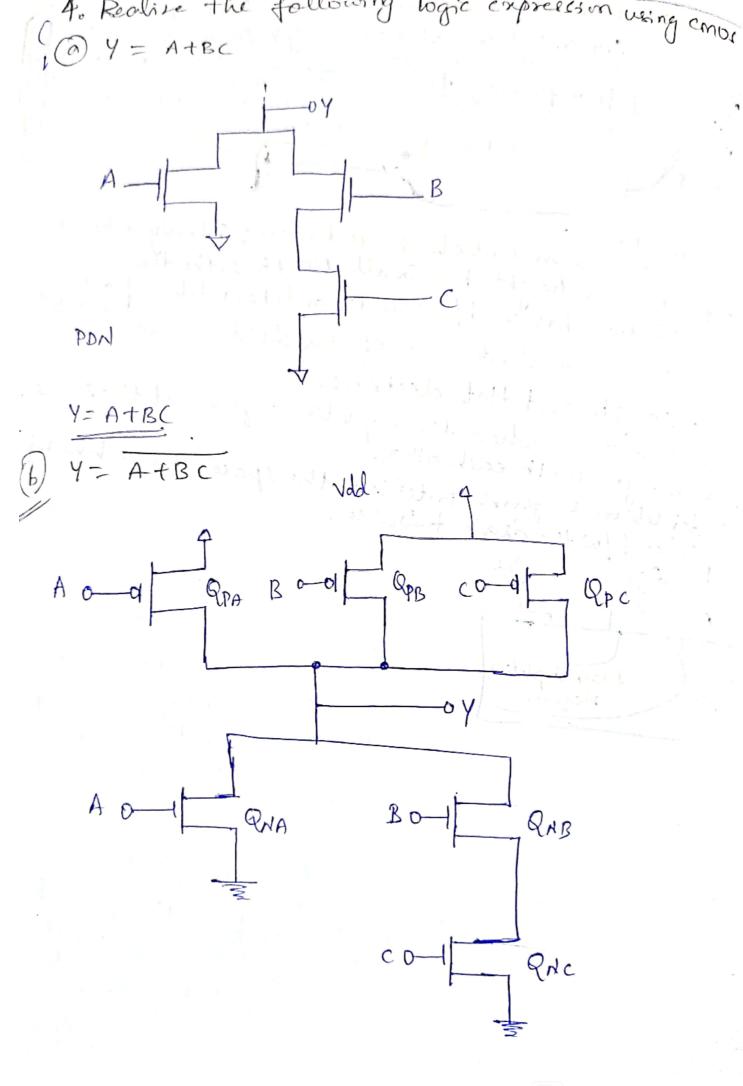

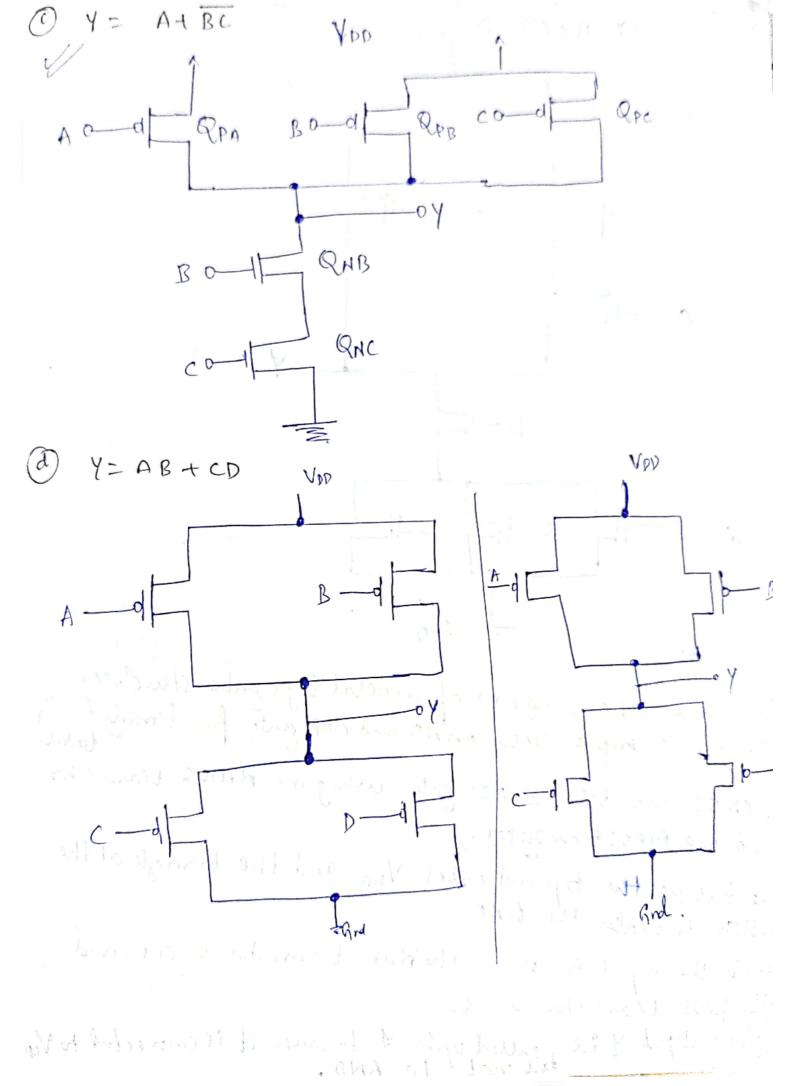

| 4. | Realize the following logic expression using CMOS:  a) $Y = A + \overline{BC}$ b) $Y = \overline{(A + B + C).D}$                    | [10] | CO1 | L2 |

|----|-------------------------------------------------------------------------------------------------------------------------------------|------|-----|----|

| 5. | Design a 4:1 multiplexer using transmission gate.                                                                                   | [10] | CO1 | L2 |

| 6. | Illustrate with neat sketch, explain the DC transfer characteristics of CMOS inverter (Include the condition for all five regions). | [10] | CO1 | L2 |

CI CCI HOD

| TICAL |  |  |  |  |  |

|-------|--|--|--|--|--|

| USN   |  |  |  |  |  |

|       |  |  |  |  |  |

| 4. | Realize the following logic expression using CMOS:<br>a) $Y = A + \overline{BC}$<br>b) $Y = \overline{(A + B + C).D}$               | [10] | CO1 | L2 |

|----|-------------------------------------------------------------------------------------------------------------------------------------|------|-----|----|

| 5. | Design a 4:1 multiplexer using transmission gate.                                                                                   | [10] | CO1 | L2 |

| 6. | Illustrate with neat sketch, explain the DC transfer characteristics of CMOS inverter (Include the condition for all five regions). | [10] | CO1 | L2 |

CI CCI HOD

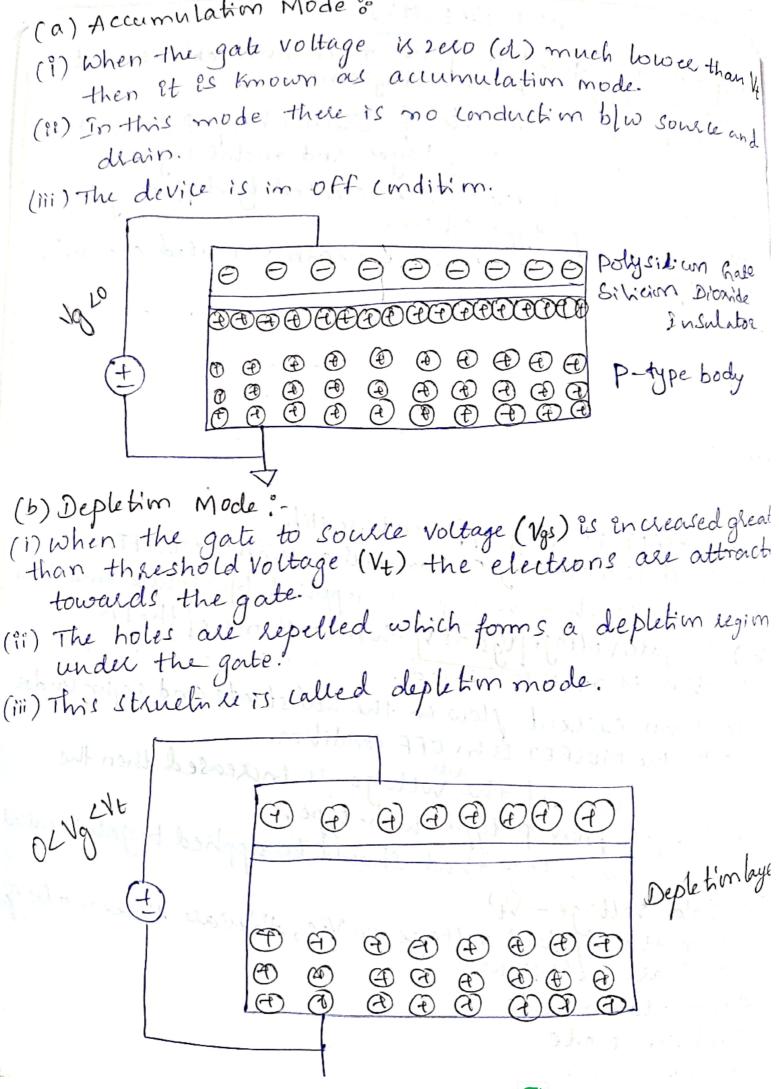

1. Explain the operation of an n-channel enhancement mode MOSFET with neat diagrams. a. The thansistors consists of Candwich of P-substrate material, insulating layer and metal layer. b. The source and drain are created by diffusing two nt regions on p-type silicon. c. The region blu source and dearn is called channel.

Source hate metallization Dearn: 5:02 dielectric lay No service | Not be to b P-Type substrate d. The mosfet is vay efficient Switch. e. The Switch is normally open in enchancement MosfET. f. When no positive voltage is applied blusoner and draw (Vds) to gate voltage Vgs = OV then least me of the PN junction is reverse biased. 9 There is no cultent flow in the substrate and region under the gate, the MOSFET is in OFF Condition. h. At this condition, if the voltage is increased then the gate changes from p-type to n-type. i. The minimum voltage that should be applied to gate is called I Based on the applied voltage on Vgs, thereare threemodes of specations are as follows: Threshold Voltage - Vt) (a) A comulation Mode (b) Depletion Mode (c) Invusim Mode. Scanned with OKEN Scanner

(c) Invusim Mode: (?) When the gate to some voltage is raised above 14, the electrons are attracted towards the substrate. (in) And the holes are repelled towards the beginn under the (111) Under this condition the surface of p-type is inverted to m-type which provides unduction. ED ED ED ED ED ED EDECE @00000000 Inversion layel program

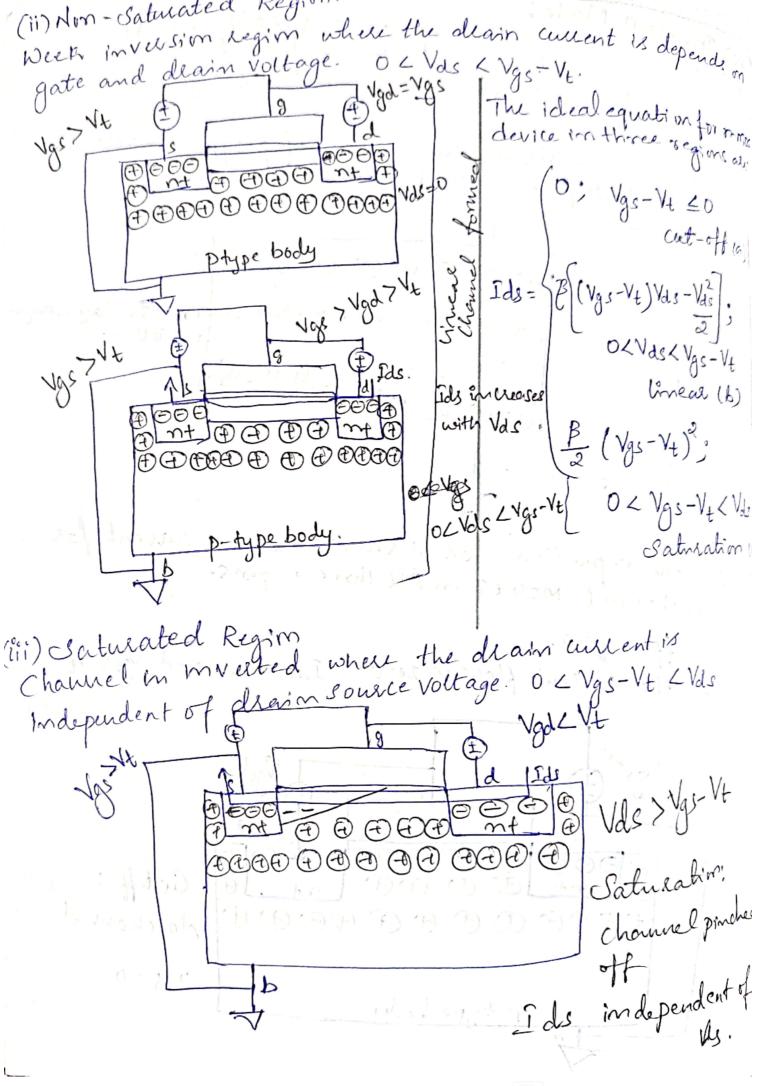

Dep betten Region 2. Derive the expression for Drain to some werent for an n-channel MOSFET in all three regions. (8) Cut - off region. where the current flow is zero: Ids = Ov and Vgs = 1/4 Ids = 0. P-type body

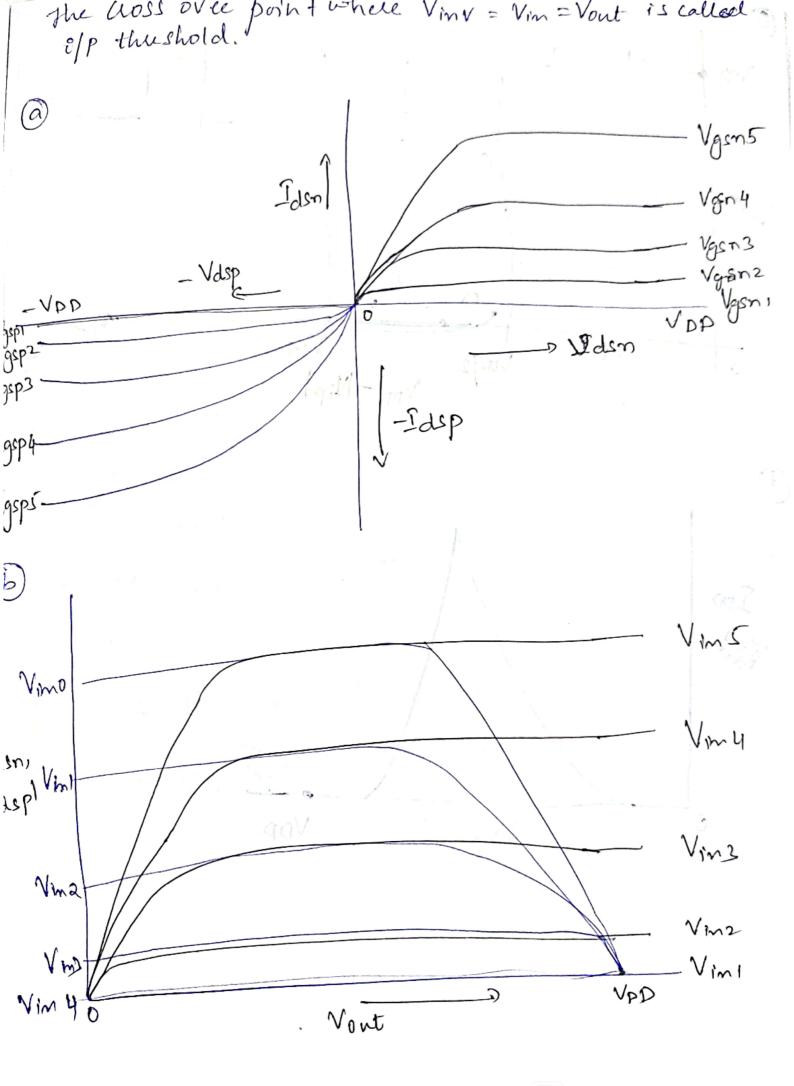

clock input is called a registers. & A register is often deawn as a flip-flop with multi-bit D and Q buses. Shite neat diagrams explain the De transfer characters

shis of cmos invertee.

Various hegions of operation to he the n-analy

transistors. Vin - is the threshold voltage of the n-channel device. Vtp - is the threshold voltage of the p-channel device. Note that April negative. The equations are given both in terms of Vgs/Vds Vin Nont. and As the source of wmos transistor is glounded, Vgsn = Vin and Valsn = Vout. As the some of PMOS transistor is tied to VDD, Vgspi=V=Vint VDD and Vdspi= Vout - VDD.

Alcos invelter.

Jago Vont

Slag Vout

Slag Vout and > miv > eleav Cust Wiser Work - D 195V - 00V 2 20V

divided into five legions. The state of each transistor in each regim. In region A, the WMOS teansistor is OFF so the pmos transistor perlls the output to VDD. In region B, the NMOS transistor starts to trun on, pulling the output down. In region c, both transistors are in Saturation. Notice that ideal transistors are only in region c for VIM = VIDD/2 and the shope of the transfer were is - 0 in this region, corresponding to infinite gain. In region D, the pmos transistor is partially on. In legion E, it is completely off, leaving the Nmoston isted to pull the output blown to GAD. Also notice that the invertee's when the 1/pis within the thresh zero, neglecting leakage, when the 1/pis within the thresh voltage of 1/2 rail and sails roltage of VDD (a) AND heirls

Noltage of VDD (a) AND heirls

This feature is important for low-power operation.

Pegin | P-device | n-device | 0/P

Region | Condition | P-device | cutoff | Vont=VDD

A | 0 \le Vin \( \text{Vin} \( \text{Vin} \) \( \text{Vin} \) O & Vim L Vtn Uneal Saturated Vout > Vpp/2 saturated Saturated Vont drops stay Vtn & Vin & VDD/2 Saturated lineal Vout LVDD/2 Vin =VDD 12 VDD 2 KVin EVDD-IVEDI cutoff | linear | Vont = 0 E Vin > VDD - | Vtp |

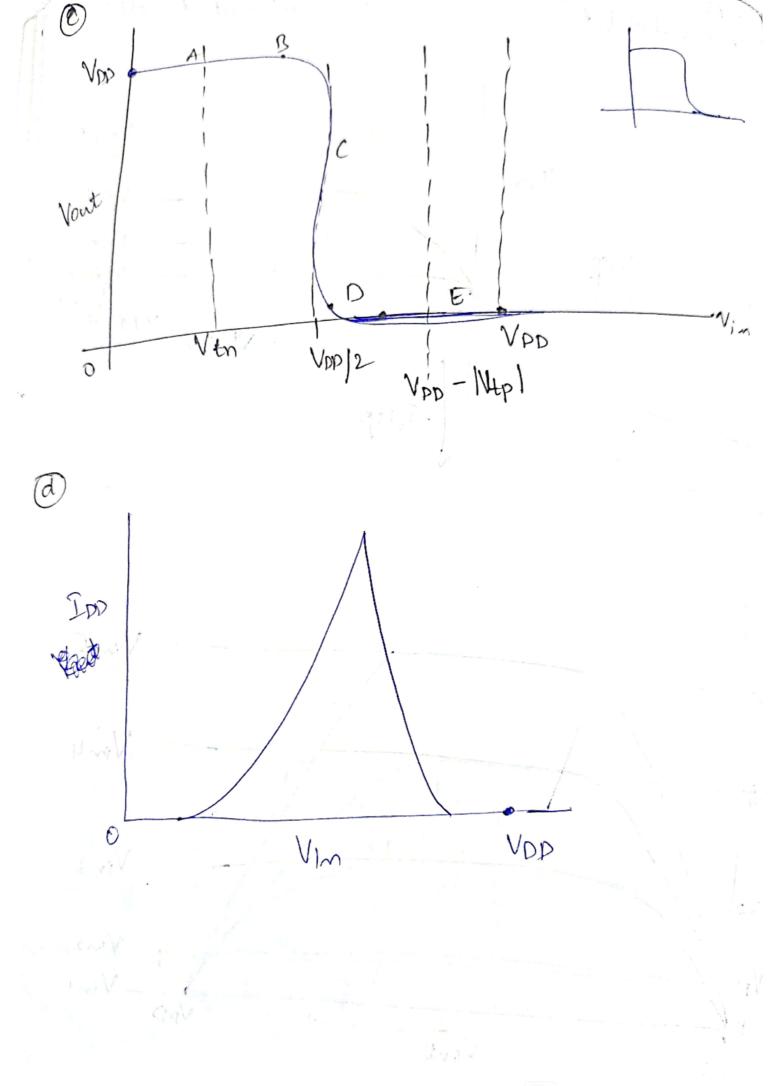

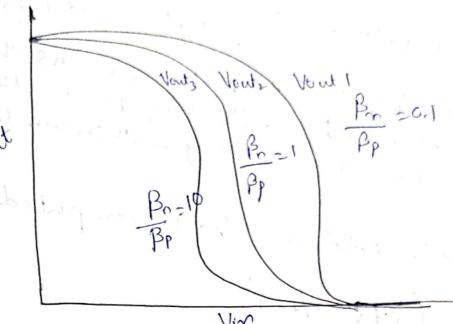

q. Explain the effects of Bn / Bp latio varitime in the diagram.

We know that  $\beta_p = \beta_n$ , the inverter threshold voltage Vinv is VDD/2.

Inverter with different beta ratios

$r = \frac{\beta_p}{\beta_n}$  are called skewed in verter [sutherland

If R> 1, the invuter is HI- Skewed.

If RL 1, the inverter is LO-skewed.

If R=1, the invertee has normal Skew (DE) is unskewed.

A HI - skew inverter has a stronger PMOS transistor.

Therefore, Pf the PPIS VPP 12, the OPP will be greated than VPP 12.

In other words, the ? Ip threshold must be higher th

Similarly, a LO-skew inveller has a weaker prince transmitor and thus a lower dwitching threshold As the better ratio is changed, the switching threshow However, the ofp voltage transition remains sharp. Rate are usually skewed by adjusting the widths of transistors while maintaining minimum length to speed. The inverter threshold can also be computed analytics Idn = Br (Vinv-Ven)2 Idp = Bp (Vim - VDD - Vtp)2. By setting the aments to be equal fopposite. Vinn = VDD + Vtp + Vtn Ja transispors are fully velocity saturated. Idn = Wn Cox Vsat-n (Vinv-Vtn) Idp = Wp Cox Vsat-p (Vinv-VDD-V40). Redefining 2 = Wp Neat-p

Wandsat-n ele thateld must be higher than