| USN |  |  |  |  |  |

|-----|--|--|--|--|--|

|     |  |  |  |  |  |

## CMR INSTITUTE OF TECHNOLOGY

|                                                                                                                        |                                                                  |  | Interna | al Assesment | Test - | - II |  |      |          |             |     |  |

|------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|--|---------|--------------|--------|------|--|------|----------|-------------|-----|--|

| Sub: VLSI DESIGN & TESTING Code                                                                                        |                                                                  |  |         |              |        |      |  |      | : 21EC63 |             |     |  |

| Date:                                                                                                                  | e: 09.07.2024 Duration: 90 mins Max<br>Marks: 50 Sem VI Branch H |  |         |              |        |      |  |      | ECH      | ECE-A,B,C,D |     |  |

|                                                                                                                        | Answer Any Five Questions                                        |  |         |              |        |      |  |      |          |             |     |  |

| Ouestions                                                                                                              |                                                                  |  |         |              |        |      |  |      | Marks    | OBE         |     |  |

| Questions                                                                                                              |                                                                  |  |         |              |        |      |  |      |          | CO          | RBT |  |

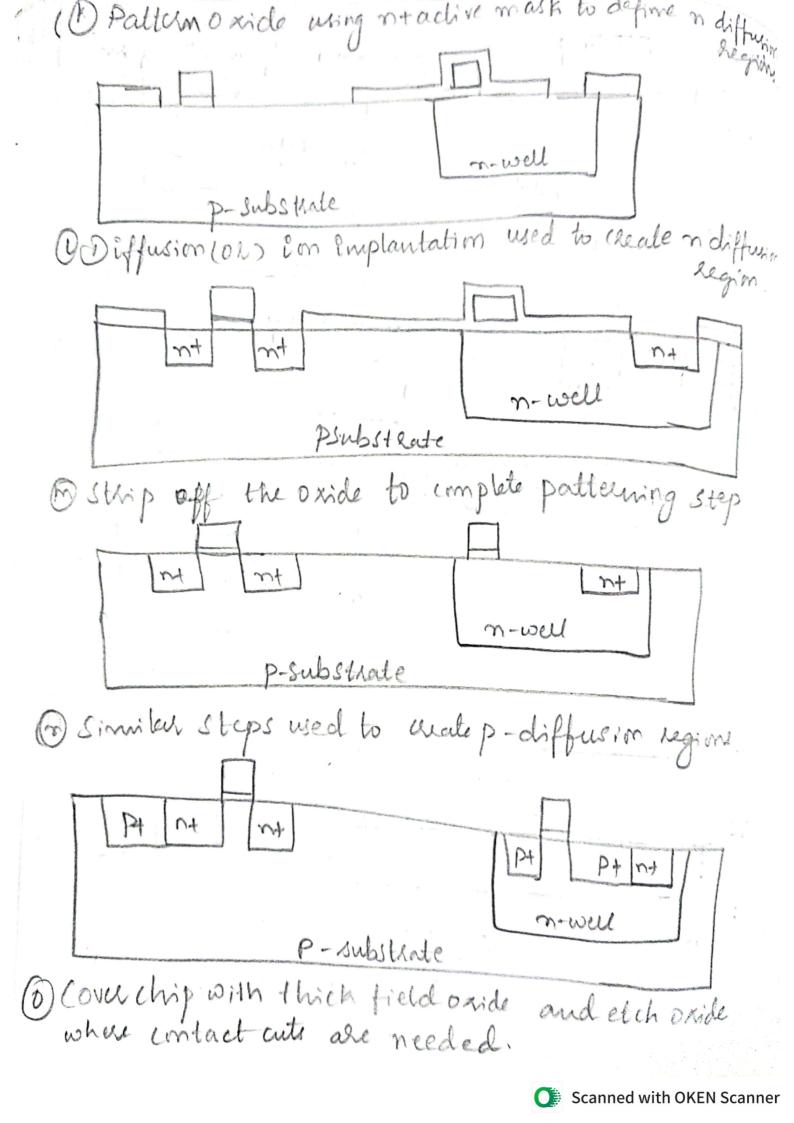

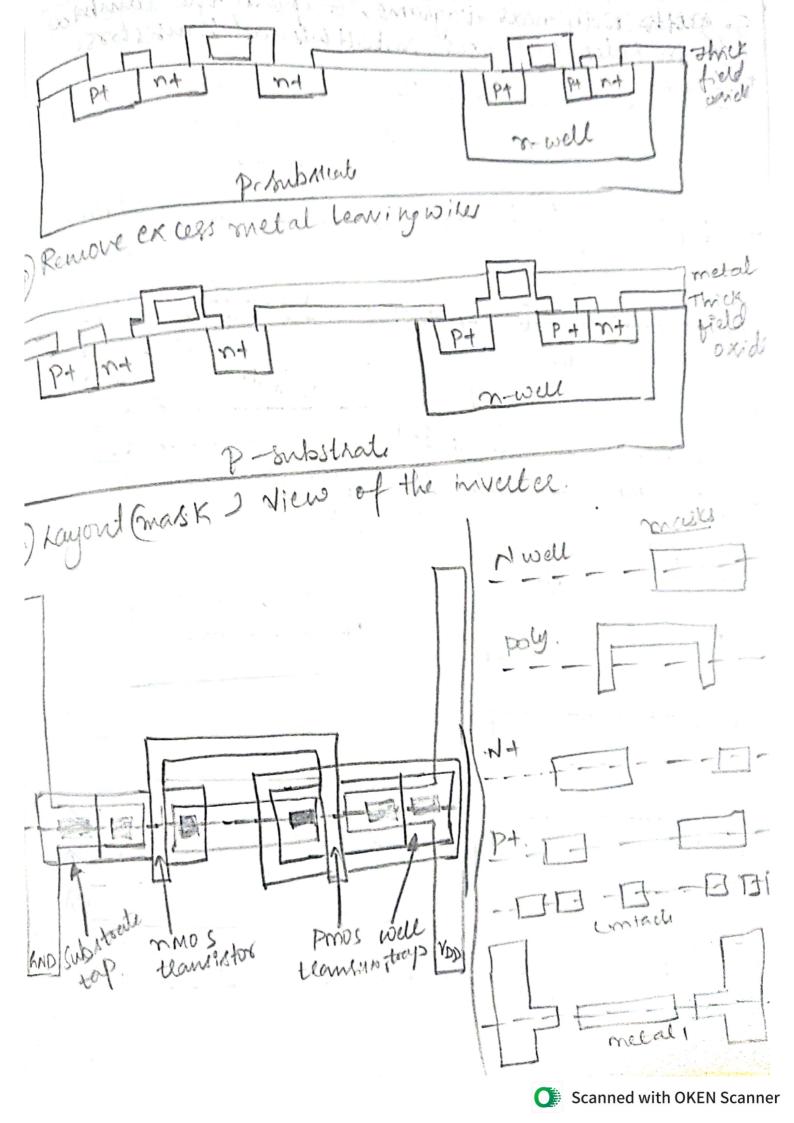

| 1. With neat diagrams explain n-well CMOS fabrication process.                                                         |                                                                  |  |         |              |        |      |  |      | [10]     | CO2         | L1  |  |

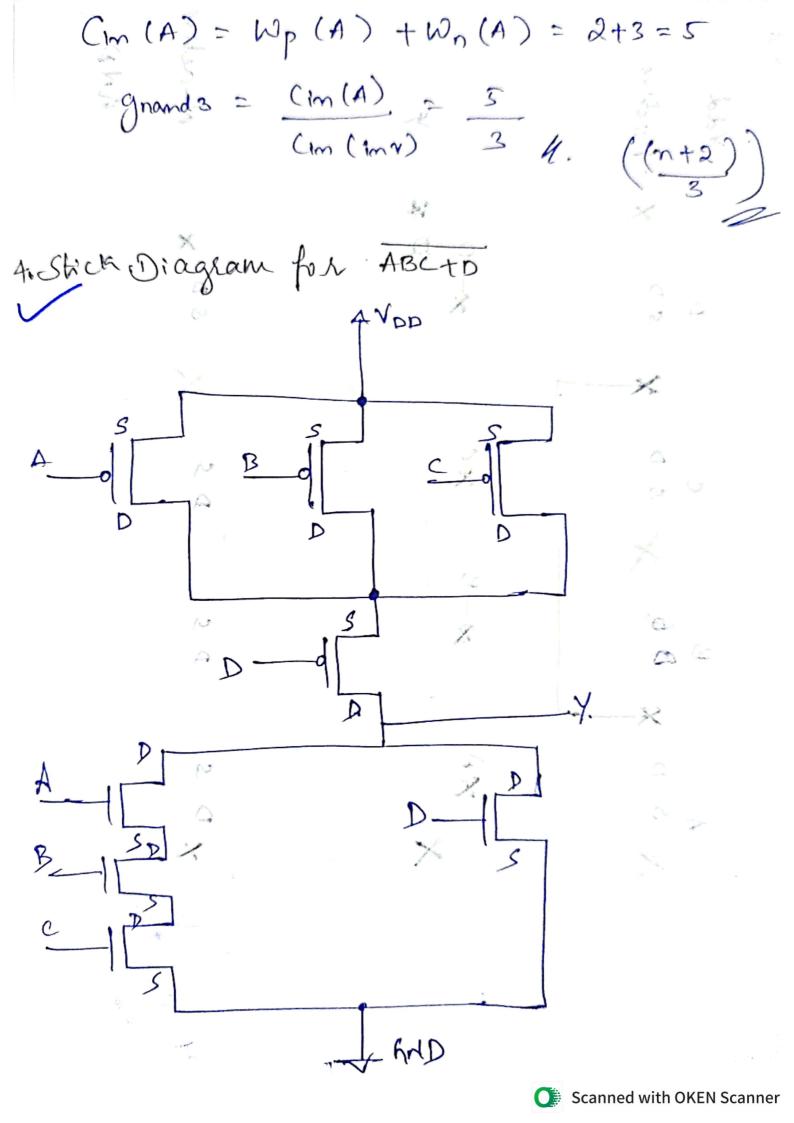

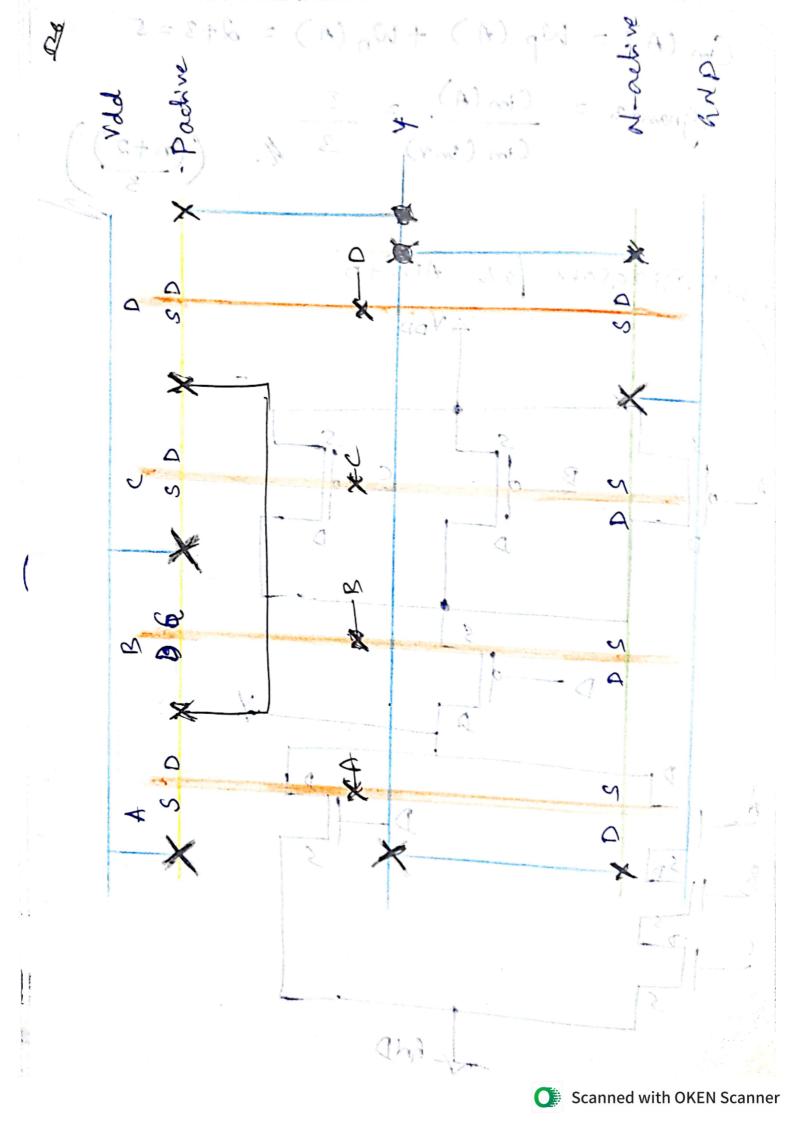

| 2. Draw the stick and layout diagram for the function $Y = \overline{ABC + D}$ .                                       |                                                                  |  |         |              |        |      |  | [10] | CO2      | L2          |     |  |

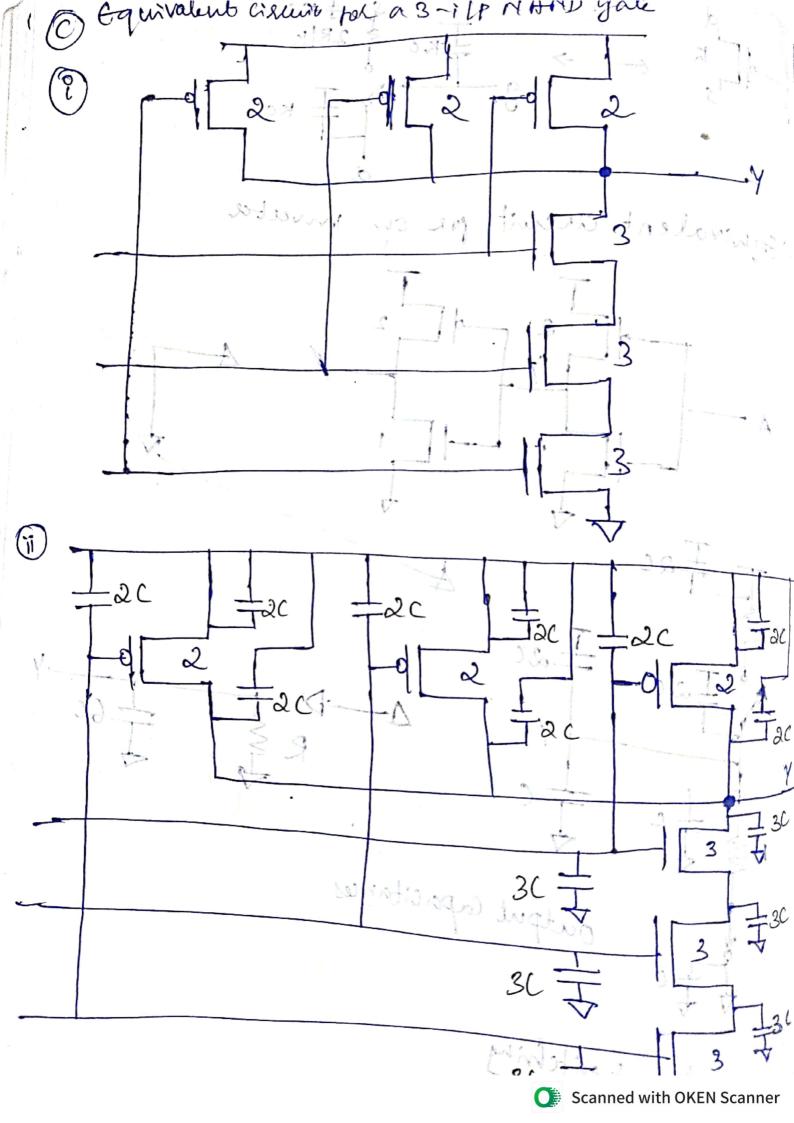

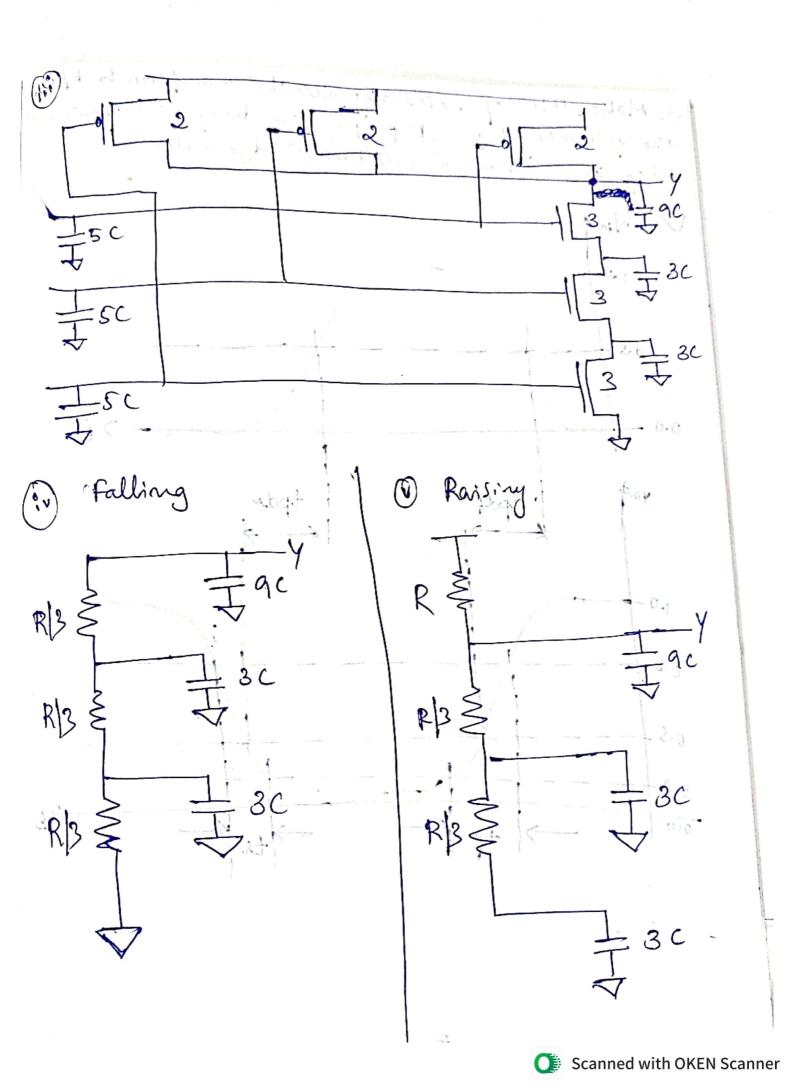

| 3. Construct necessary equivalent circuits using RC delay model to compute the propagation delay of 3-input NAND Gate. |                                                                  |  |         |              |        |      |  | [10] | CO2      | L2          |     |  |

| USN |  |  |  |  |

|-----|--|--|--|--|

|-----|--|--|--|--|

## CMR INSTITUTE OF TECHNOLOGY

|                                                                                                                        | Internal Assessment Test – II |             |            |               |    |     |      |        |             |        |     |  |  |

|------------------------------------------------------------------------------------------------------------------------|-------------------------------|-------------|------------|---------------|----|-----|------|--------|-------------|--------|-----|--|--|

| Sub:                                                                                                                   | VLSI DESIG                    | SN & TESTIN | ١G         |               |    |     |      | Code:  | <b>21EC</b> | 21EC63 |     |  |  |

| Date:                                                                                                                  | 09.07.2024                    | Duration:   | 90<br>mins | Max<br>Marks: | 50 | Sem | VI   | Branch | ECE-A,B,C,D |        |     |  |  |

|                                                                                                                        | Answer Any Five Questions     |             |            |               |    |     |      |        |             |        |     |  |  |

| Questions                                                                                                              |                               |             |            |               |    |     |      |        | Marks       | OBE    |     |  |  |

|                                                                                                                        |                               |             |            |               |    |     |      |        |             | CO     | RBT |  |  |

| 1. With neat diagrams explain n-well CMOS fabrication process.                                                         |                               |             |            |               |    |     |      | [10]   | CO2         | L1     |     |  |  |

| 2. Draw the stick and layout diagram for the function $Y = \overline{ABC + D}$ .                                       |                               |             |            |               |    |     | [10] | CO2    | L2          |        |     |  |  |

| 3. Construct necessary equivalent circuits using RC delay model to compute the propagation delay of 3-input NAND Gate. |                               |             |            |               |    |     | [10] | CO2    | L2          |        |     |  |  |

| USN |  |  |  |  |  |

|-----|--|--|--|--|--|

|-----|--|--|--|--|--|

|    | Make use of necessary circuit diagrams to compute logical effort of the following gates. (i) 2-input NOR gate and (ii) 3-input NAND Gate. | [10] | CO2 | L2 |

|----|-------------------------------------------------------------------------------------------------------------------------------------------|------|-----|----|

| 5. | With necessary circuit diagram, explain the operation of three transistor DRAM cell.                                                      | [10] | CO3 | L2 |

| 6. | Explain full CMOS SRAM cell with necessary circuit topology.                                                                              | [10] | CO3 | L2 |

CI

CCI

HOD

| USN |     |  |  |  |  |  |

|-----|-----|--|--|--|--|--|

|     | USN |  |  |  |  |  |

| 4. | Make use of necessary circuit diagrams to compute logical effort of the following gates. (i) 2-input NOR gate and (ii) 3-input NAND Gate. | [10] | CO2 | L2 |  |

|----|-------------------------------------------------------------------------------------------------------------------------------------------|------|-----|----|--|

| 5. | With necessary circuit diagram, explain the operation of three transistor DRAM cell.                                                      | [10] | CO3 | L2 |  |

| 6. | Explain full CMOS SRAM cell with necessary circuit topology.                                                                              | [10] | CO3 | L2 |  |

CCI

HOD

7. Explain neat draglan Explain n-well cmos Tabrication process. @ Blank wafer covered with a layer of SED2 using oxidation. 5:02 (DSpin on the photohesist. Exposed to UV light using the model mark: (photo lithography) -, photoresist 2 substrate

Scanned with OKEN Scanner

the enposed photoresist using organic Ostrip. off solvents. Si O2 proubstrate. @ Etch the uncovered oxide using HF (Hydro flowic Photoresist 5:02 P- Substrate. OFTCH the remaining photoesist using a minture of och p substrate ( Dn-well is formed using either diffusion or for implantation n well Sidz ( Strip off the remaining oxide using HF. Subsequent steps use the same photolithography process.

💽 👔 Scanned with OKEN Scanner

mwell P substrate Deposit thin layer of oride. Use CVD to form poly and dupe Deposity to increase conductivity polysilicon Then gate nwell Pattern polyusing the previously discussed photo lithography process Thin get Opride n-well P-substeate Dlover with Oxide to define on diffusion regions. -well p substiale

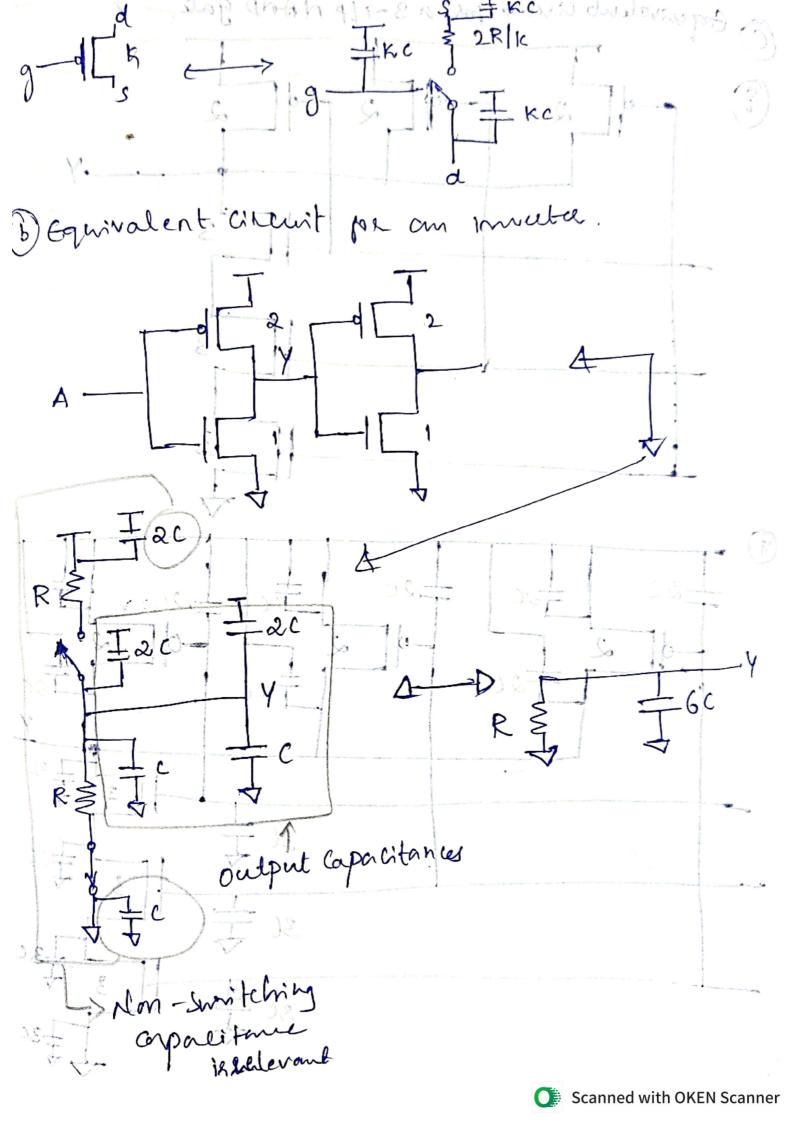

2. Constanct necessary equivalent circuite using Ryc delay model to compute the propagation delay S-imput NARD gate. the chip. Rec circuit models to mos and pmos transistory width to with contacted diffusion on both douge and deam? of so by The PMDS transistor has approximately twice the resistance of the NMOS transistor because holes have lower mobility than electrons. The PMO'S capacitors are shown with Npp asister terminal because the n-willow usully fied high The equivalent likenits for logic gates are assemble from the individual transmitore. The unit invertees are composed from on NMOS transistor of unit size and a PMOS transistorof twice unit width to achieve equal rise and fall a) Equinalent Circuits pord bransisher. g-ICK c > g IKE Fre KC Fre S Fre

6T SRAM bit word SRAM qualita is divided into two phases. The phases will be called \$, and \$2, but may actually be (generated from clk and its complement clkb (Assume that in phase 2, the SRAM is prechaged In phase 1, the SRAM is head on whitten. ( Read operation -> SRAM' cell being read. -> The bittines are both initially floating high. -> Without loss of generality, assume Q is imitially O and thus Q-b is initially 1. -> Q-b and bit-b both should remain 1

, when the word line is haised, bit should be pulled down through driver and a ccess transistors DI and AI. At the dame time bit is being pulled down, node Q Lends to Rise. Q is held low by DI, but raised by current flowing in It the disiver DI must be stoonger than the access The transistors must be ratioed such that node Quina--ins below the Quoitching threshold of the P2/122 invalue. This constraint is called lead stability, > Observe that & momentarily sises, but aber not glitch badly enough to thip the cell. bet-b 1.D bet word

🔘 🕺 Scanned with OKEN Scanner

-> SRAAM cell being whitten. -> SRAAM cell being whitten. -> Again, 5 Q is initially D and that to whitead intoical. - Bet 22 precharged high and left floating. -) bit b is pulled but by a white driver. -) The read stability enstraint that bit well be unable to force a high through Al. - Hence, the cell must be written by forcing Q-b » P2 Opposes this operation of thus, P2 must be weaker than A2 aso that Q-b I can be pulled low enough. - This constraint is called whitabelity. Once quefalle low, DI turns OFF and Piturns ON, pulling a high as desired.