# VTU Question Paper Solution

| IN                                        | The second secon |                                                                                                                                                                                                             | BEC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2405                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| And a | A constar B F /B Tech Degree Examination, June/J                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | uly                                                                                                                                                                                                         | 2024                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Ĉ                                         | AR 'S Microcontrollers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | -                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| ANGAL                                     | ORE THE Max                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                           | Note: 1. Answer any FIVE full questions, choosing ONE full question from each<br>2. M : Marks , L: Bloom's level , C: Course outcomes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | modi                                                                                                                                                                                                        | ile.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                           | Module 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Μ                                                                                                                                                                                                           | L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | С                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 2.                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 6                                                                                                                                                                                                           | L2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | CO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

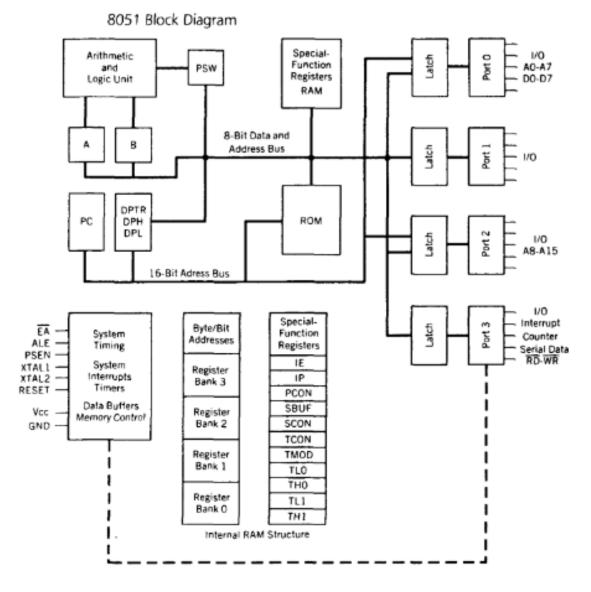

| b.                                        | With a neat Architecture diagram, explain the Architecture of 8051<br>Microcontroller.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 10                                                                                                                                                                                                          | L2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | CO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| c.                                        | Explain : (i) RST (ii) INT Pins of 8051                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4                                                                                                                                                                                                           | L1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | CO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                           | OR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 6                                                                                                                                                                                                           | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | CO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| a.                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | -                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

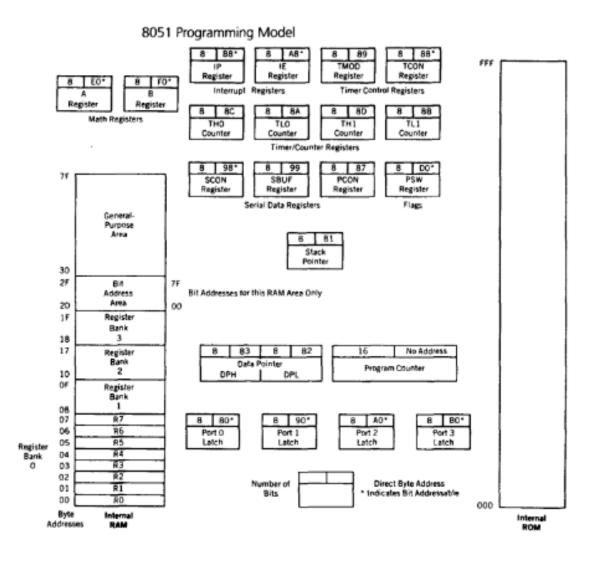

| b.                                        | With a neat diagram, explain the Internal Memory Structure and Programming Model of 8051 Microcontroller.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 10                                                                                                                                                                                                          | L2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | CO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| C                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4                                                                                                                                                                                                           | L2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | CO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                           | 1 V IOLINS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | -                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| a.                                        | Define Addressing Mode. Explain different addressing modes with example.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 10                                                                                                                                                                                                          | L2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | CO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| b.                                        | Write an ALP to add two 16-bit numbers loaded in $R_1R_0$ and $R_3R_2$ . Store the result in $R_6R_3$ and $R_4$ from MSB to LSB.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 10                                                                                                                                                                                                          | L3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | CO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                           | a.<br>b.<br>c.<br>a.<br>b.<br>c.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Microcontrollers         Ime: 3 hrs.       Max         Note: 1. Answer any FIVE full questions, choosing ONE full question from each 2. M : Marks , L: Bloom's level , C: Course outcomes.         Module 1 | Microcontrollers         Ime: 3 hrs.       Max. Max. Max. Note: 1. Answer any FIVE full questions, choosing ONE full question from each module 2. M : Marks , L: Bloom's level , C: Course outcomes.         Module - 1       M         a.       Bring out the difference between Microprocessor and Microcontroller.       6         b.       With a neat Architecture diagram, explain the Architecture of 8051       10         Microcontroller.       6         c.       Explain : (i) RST       (ii) INT Pins of 8051       4         OR         a.       Differentiate between CISC and RISC.       6         b.       With a neat diagram, explain the Internal Memory Structure and 10       10         Programming Model of 8051 Microcontroller.       4         Module - 2         a.       Define Addressing Mode. Explain different addressing modes with 10         example.       9         b.       Write an ALP to add two 16-bit numbers loaded in R <sub>1</sub> R <sub>0</sub> and R <sub>3</sub> R <sub>2</sub> . Store       10 | Microcontrollers         Max. Marks:         Note: 1. Answer any FIVE full questions, choosing ONE full question from each module.         2. M : Marks, L: Bloom's level, C: Course outcomes.         Module - 1       M         a.       Bring out the difference between Microprocessor and Microcontroller.         b.       With a neat Architecture diagram, explain the Architecture of 8051         10       L2         Microcontroller.       6         c.       Explain : (i) RST         (ii) INT Pins of 8051       4         L1       0R         a.       Differentiate between CISC and RISC.         b.       With a neat diagram, explain the Internal Memory Structure and 10         L2       Differentiate between CISC and RISC.         b.       With a neat diagram, explain the Internal Memory Structure and 10         L2       Module - 2         a.       Define Addressing Mode. Explain different addressing modes with 10       L2         Module - 2       1         a.       Define Addressing Mode. Explain different addressing modes with 10       L2 |

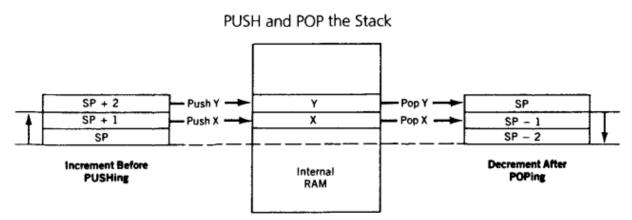

| Q.4 | a.         | Define Stack. Explain the operation of Stack using Stack Pointer, PUSH                                        | 10 | L2 | CO2 |

|-----|------------|---------------------------------------------------------------------------------------------------------------|----|----|-----|

| Q.4 | <i>a</i> . | and POP Instructions.                                                                                         |    |    |     |

|     | b.         | Write an ALP to find largest of N numbers.                                                                    | 10 | L3 | CO2 |

|     |            | Module – 3                                                                                                    |    |    |     |

| Q.5 | a.         | Explain : (i) TMOD (ii) TCON register of 8051.                                                                | 10 | L2 | CO3 |

| Q.5 |            | Assume $XTAL = 22$ MHz. Write an ALP to generate a square of frequency                                        | 10 | L2 | CO3 |

|     | b.         | Assume XTAL = 22 MHZ. White an ALL to generate a square of 2-quart of 1 kHz on Pin P1.2.                      |    |    |     |

|     |            | OR                                                                                                            |    |    |     |

| Q.6 | a.         | Explain : (i) SCON register (ii) Importance of TI Flag                                                        | 10 | L2 | CO3 |

|     | b.         | Write a C program to transfer "YES" serially at 9600 baud rate, 8 bit data, 1 stop bit, do this continuously. | 10 | L3 | CO3 |

|     |            | Module – 4                                                                                                    |    |    |     |

| Q.7 | a.         | Define Interrupt. List the steps involved in Executing an Interrupt.                                          | 10 | L2 | CO4 |

| 2.1 | b.         | Explain Interrupt Vector table of 8051 Microcontroller.                                                       | 5  | L2 | CO4 |

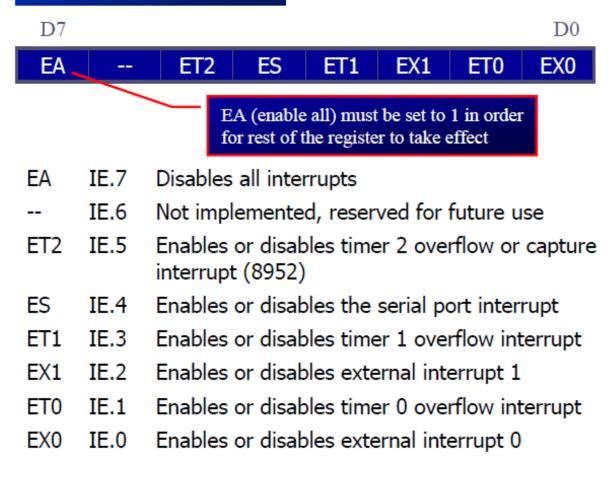

|     | c.         | Explain Interrupt enable register.                                                                            | 5  | L2 | CO4 |

|     | 10.        | OR                                                                                                            |    |    |     |

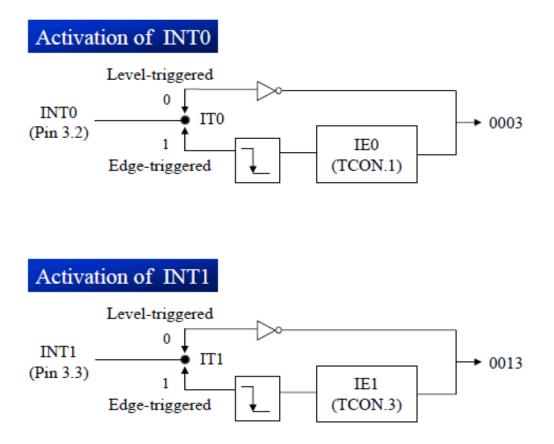

| 0.0 | 10         | Explain Interrupt Control used in 8051.                                                                       | 10 | L2 | CO4 |

| Q.8 | a.         | Explain the steps involved in programming serial communication Interrupt.                                     | 5  | L2 | C04 |

|     | b.         | Explain the steps involved in programming certain comments                                                    | -  | 1  |     |

#### 1 of 2

- A

#### BEC405A

|      | c. | Explain how multiple Interrupts are handled in 8051.                                               | 5  | L2 | CO4 |

|------|----|----------------------------------------------------------------------------------------------------|----|----|-----|