| USN |  |  |  |  |  |  |  |  |  |  |

|-----|--|--|--|--|--|--|--|--|--|--|

|-----|--|--|--|--|--|--|--|--|--|--|

#### Internal Assessment Test 1 – November 2024

| Sub:  | Digital Desig                                                                                                             | gn and Con                                                                          |                                                                           | anization                                                                        |                                        | Sub Code:                                                        | BCS302                                                       | Branc            | h: CSE     |     |    |

|-------|---------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|---------------------------------------------------------------------------|----------------------------------------------------------------------------------|----------------------------------------|------------------------------------------------------------------|--------------------------------------------------------------|------------------|------------|-----|----|

| Date: | 06/11/2024 Duration: 90 mins Max Marks: 50 Sem / Sec: 3 <sup>rd</sup> semester/                                           |                                                                                     |                                                                           |                                                                                  |                                        | ster/A,B                                                         | ,C                                                           | 0                | BE         |     |    |

|       | Answer any FIVE FULL Questions                                                                                            |                                                                                     |                                                                           |                                                                                  |                                        |                                                                  | MARKS                                                        | <u>CO</u>        | <u>RBT</u> |     |    |

| 1 a)  | What is posit                                                                                                             | ive logic a                                                                         | nd negativ                                                                | e logic?                                                                         |                                        |                                                                  |                                                              |                  | [2]        |     |    |

|       | A digital syst<br>I/P in four-bit<br>as "0001" and<br>of the month<br>number in the<br>(i) Write truth<br>(iii) Realize u | t form. The<br>l so on. Th<br>containing<br>e I/P beyor<br>table, SO<br>using basic | e month of<br>e output o<br>31 days, o<br>d 1011' as<br>P and PO<br>gates | January is re<br>f the system<br>or otherwise,<br>don't care co<br>S form (ii) S | epres<br>shou<br>it is<br>ondi<br>impl | sented as '(<br>ild corresp<br>'0'.Consid<br>tion:<br>ify for SO | 0000', Febru<br>ond to the in<br>er the exces<br>P using K-n | ary<br>nput<br>s | [8]        | CO1 | L3 |

|       | 2 a) Define1.Implicant2.Prime Implicant[3+2]4. Redundant prime implicant.                                                 |                                                                                     |                                                                           |                                                                                  |                                        | C01                                                              | L2                                                           |                  |            |     |    |

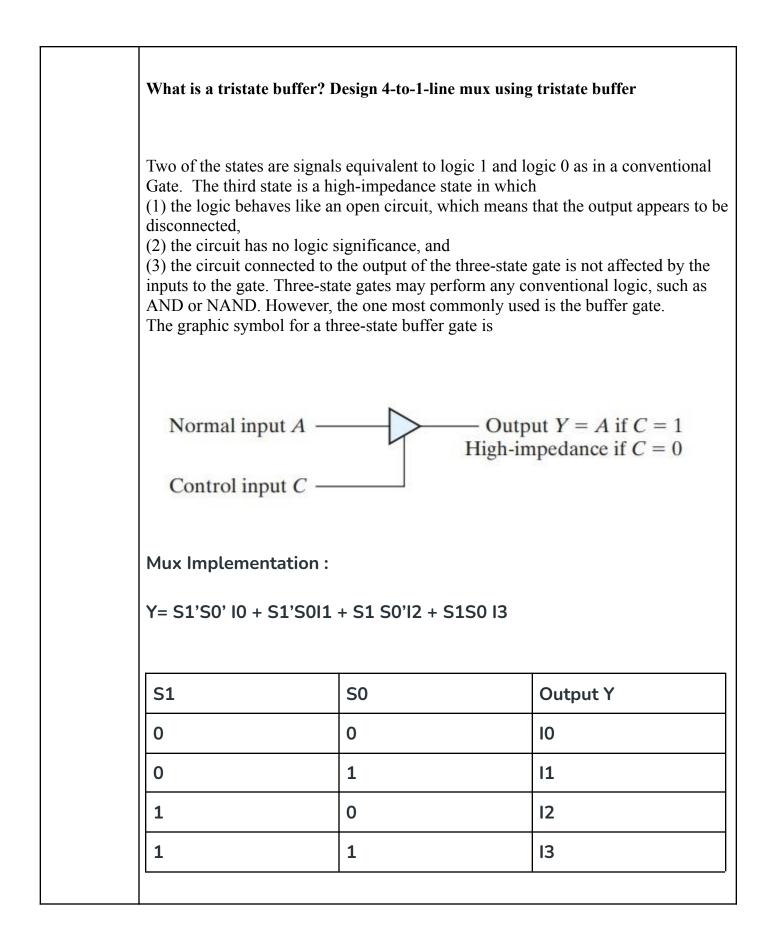

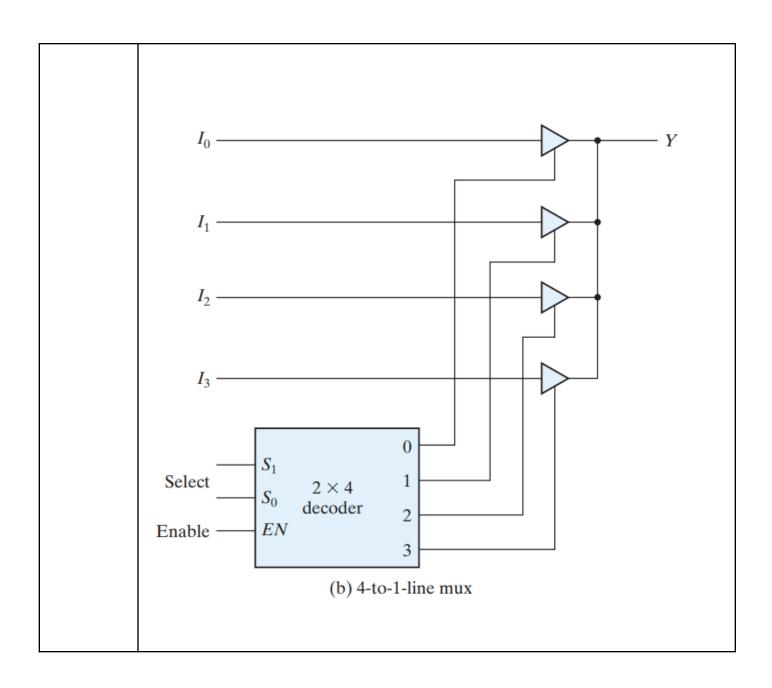

| b)    | What is a tris                                                                                                            | tate buffer                                                                         | ? Design 4                                                                | 4-to-1-line m                                                                    | iux i                                  | ising trista                                                     | te buffer.                                                   |                  | [2+3]      | CO2 |    |

# Internal Assessment Test 1 – November 2024

USN

| Sub:  | Digital Design and Computer Organization                                                                                     |                                                                      | -                                                                     | Sub Code:                                                       | BCS302                 | Branc                                    | : CS                                        | E           |              |           |    |            |

|-------|------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|-----------------------------------------------------------------------|-----------------------------------------------------------------|------------------------|------------------------------------------|---------------------------------------------|-------------|--------------|-----------|----|------------|

|       |                                                                                                                              |                                                                      |                                                                       |                                                                 |                        |                                          |                                             |             |              |           |    |            |

| Date: | Date:     06/11/2024     Duration:     90 mins     Max Marks:     50     Sem / Sec:     3 <sup>rd</sup> semester/A           |                                                                      |                                                                       |                                                                 |                        |                                          |                                             | ster/A,B,0  |              |           | OE |            |

| _     |                                                                                                                              |                                                                      | Answer any FI                                                         | VE FULL Questions                                               |                        |                                          |                                             |             | <u>MARKS</u> | <u>C(</u> | 2  | <u>RBT</u> |

| 1 a)  | What is positi                                                                                                               | ve logic an                                                          | d negative                                                            | logic?                                                          |                        |                                          |                                             |             | [2]          |           |    |            |

| b)    | A digital syste<br>in four-bit for<br>"0001" and so<br>month contain<br>the I/P beyond<br>(i) Write truth<br>(iii) Realize u | m. The mo<br>on. The ou<br>ning 31 day<br>d 1011' as d<br>table, SOF | nth of Janu<br>utput of the<br>s, or other<br>lon't care c<br>and POS | ary is represe<br>system shou<br>wise, it is '0'.0<br>ondition: | ented<br>ld co<br>Cons | as '0000',<br>prrespond t<br>ider the ex | February as<br>o the input o<br>cess number | f the<br>in | [8]          | C         | 01 | L3         |

|       | Define 1.Imp<br>4. Redundant<br>Identify Prim<br>$f(A,B,C,D)=\sum$<br>What is a trist                                        | prime imp<br>e implicant<br>2m(1,3,4,5,                              | licant.<br>t and essen<br>10,1112,13                                  | tial prime im<br>5,14,15)                                       | plica                  | nt                                       |                                             |             | [3+2]        | co        |    | L2         |

|           | What is the drawback of n-bit ripple carry adder? Design and explain 4 bit carry look ahead adder.                                     | [5]       |     |     |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------|-----------|-----|-----|

| b)        | Write a Verilog HDL code to simulate the working of Half adder and Full<br>adder in data flow and structural model                     | [2.5+2.5] | CO2 | L3  |

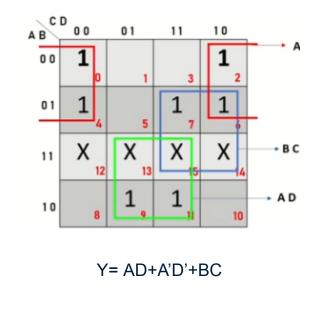

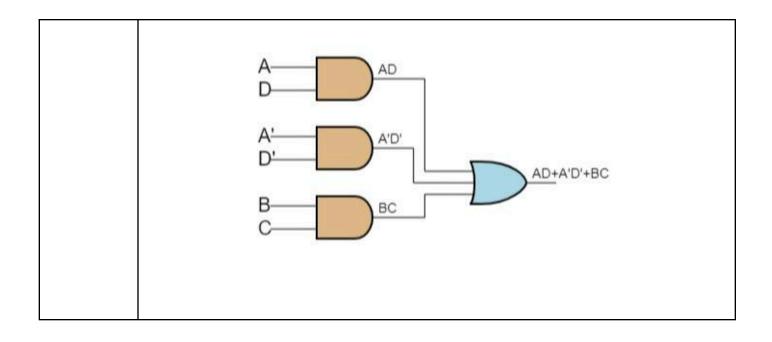

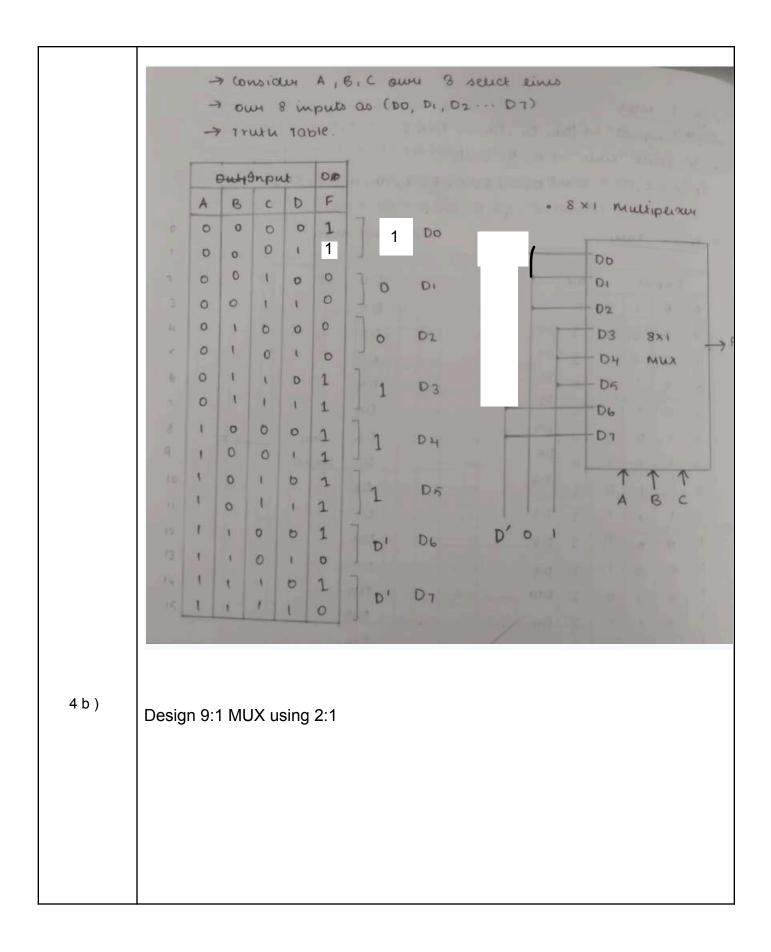

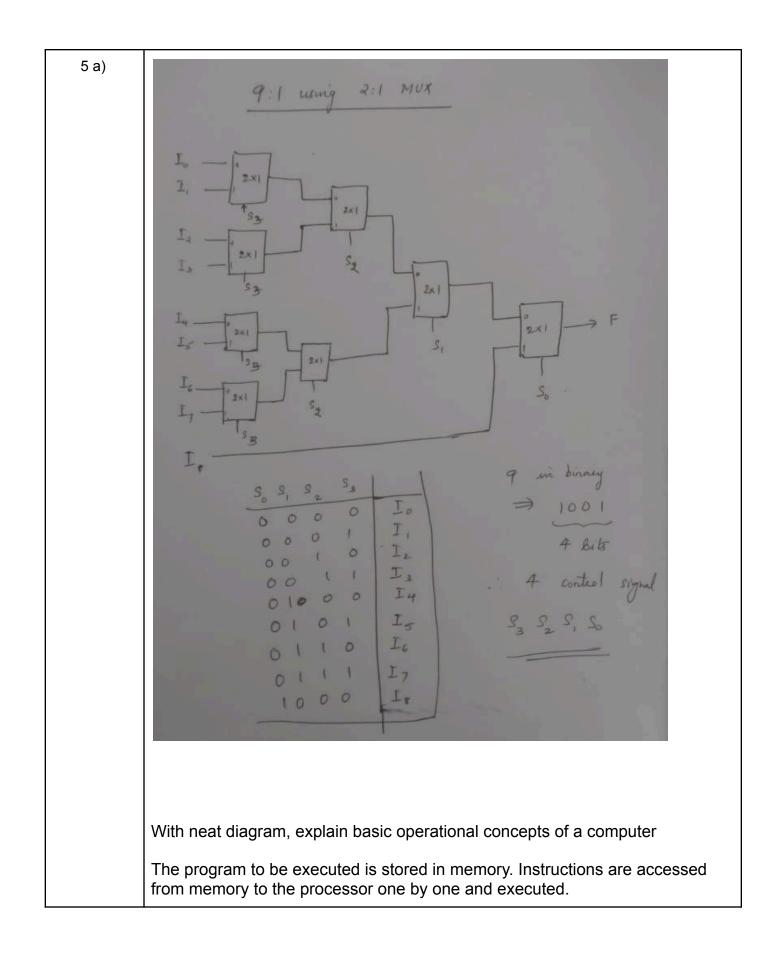

|           | Implement Y (A, B, C, D) = $\sum m (0, 1, 6, 7, 8, 9, 10, 11, 12, 14)$ using 8-to-1 multiplexer.<br>Design 9:1 MUX using 2:1           | [5+5]     | CO2 | L2  |

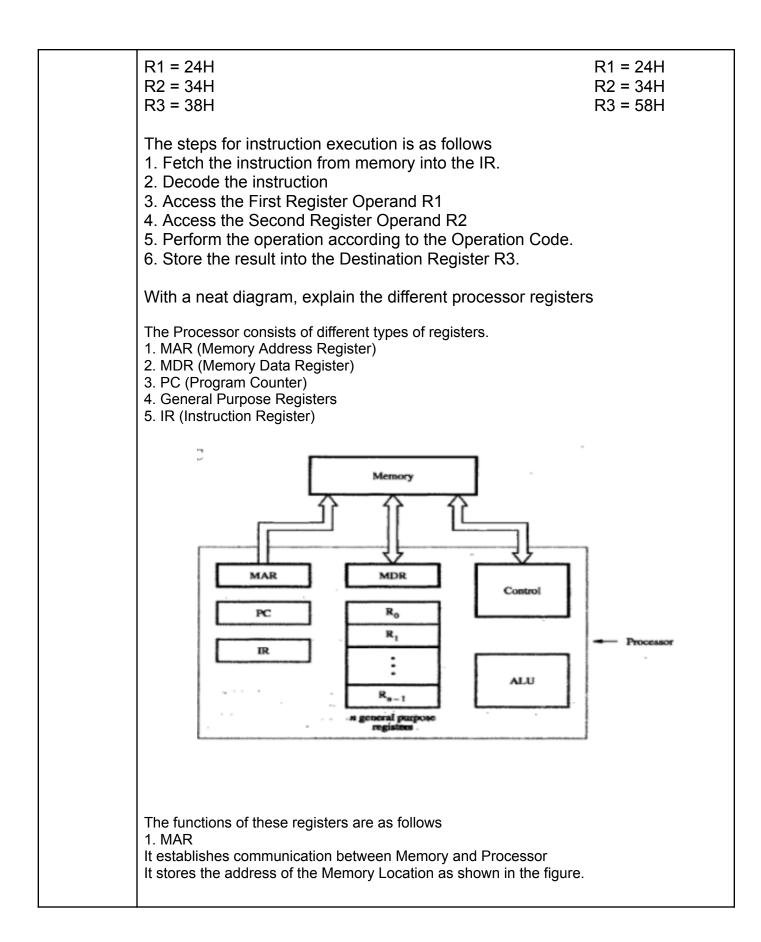

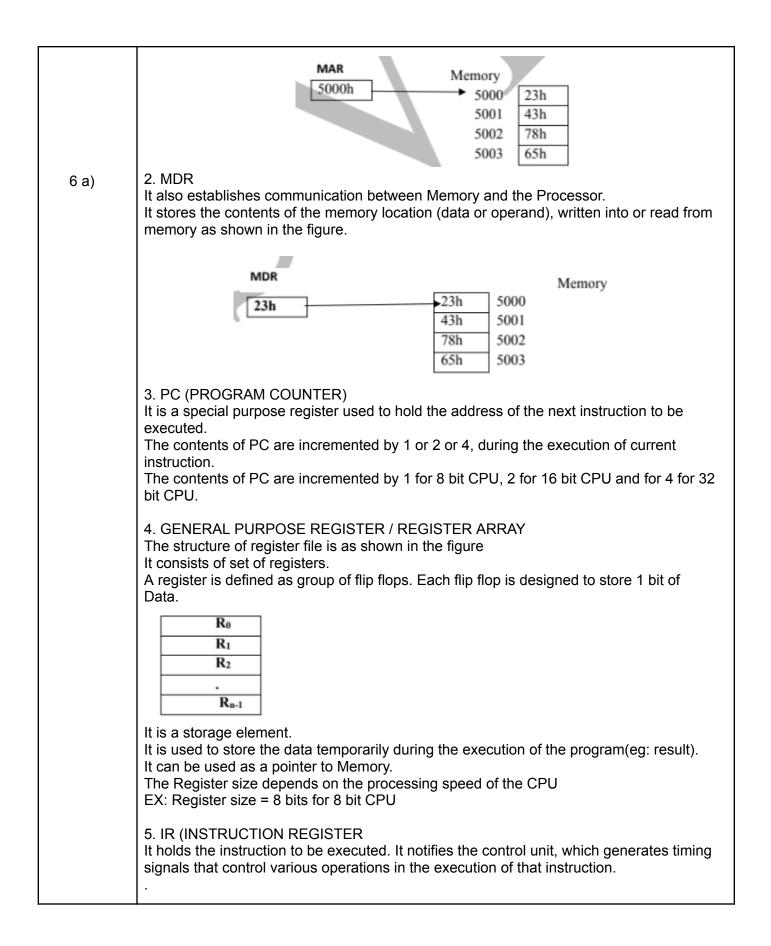

| 5a)<br>b) | With neat diagram, explain basic operational concepts of a computer<br>With a neat diagram, explain the different processor registers. | [6+4]     | CO3 | L2  |

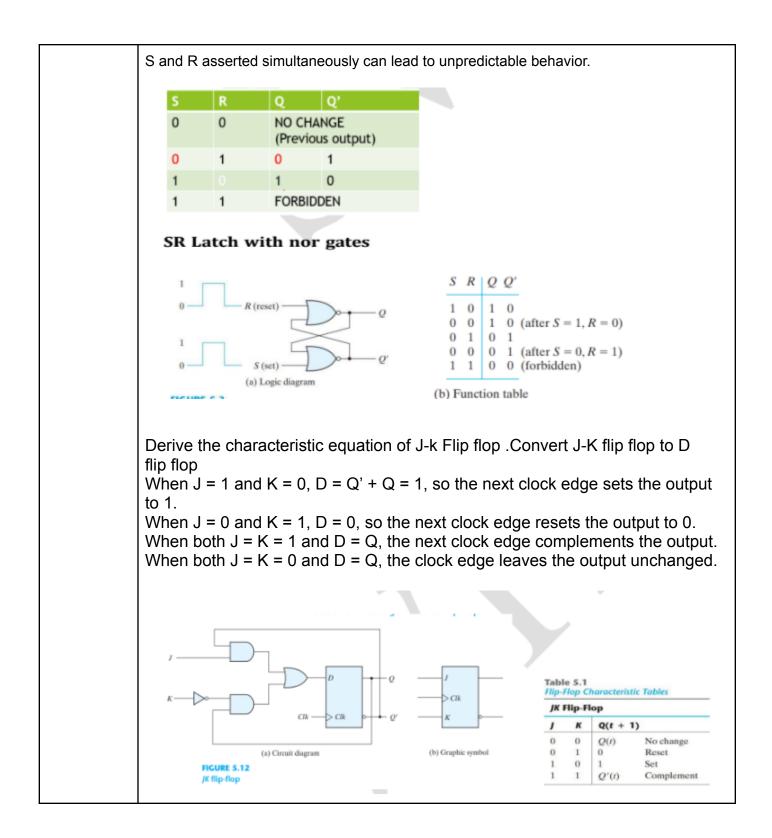

| 6.a)      | What is the difference between latch and flip flop? Design NOR S-R latch.                                                              | [1+2]     | CO2 | ,L3 |

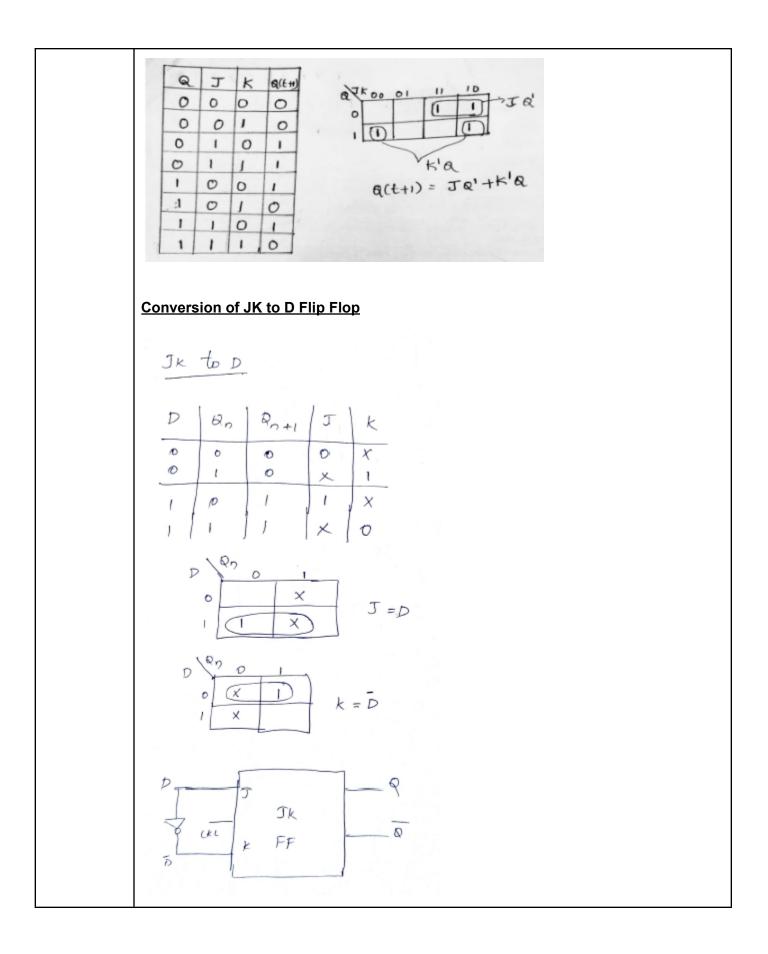

| - )       | Derive the characteristic equation of J-k Flip flop .Convert J-K flip flop to D flip flop                                              | [4+3]     |     |     |

| 1 | ٦ | T |

|---|---|---|

| C | ~ | I |

CCI

HOD

|           | What is the drawback of n-bit ripple carry adder? Design and explain 4 bit carry look ahead adder.                                     | [5]       |     |     |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------|-----------|-----|-----|

|           | Write a Verilog HDL code to simulate the working of Half adder and Full<br>adder in data flow and structural model                     | [2.5+2.5] | CO2 | L3  |

|           | Implement Y (A, B, C, D) = $\sum m (0, 1, 6, 7, 8, 9, 10, 11, 12, 14)$ using 8-to-1 multiplexer.<br>Design 9:1 MUX using 2:1           | [5+5]     | CO2 | L2  |

| 5a)<br>b) | With neat diagram, explain basic operational concepts of a computer<br>With a neat diagram, explain the different processor registers. | [6+4]     | CO3 | L2  |

| ,         | What is the difference between latch and flip flop? Design NOR S-R latch.                                                              | [1+2]     | CO2 | ,L3 |

| - )       | Derive the characteristic equation of J-k Flip flop .Convert J-K flip flop to D flip flop                                              | [4+3]     |     |     |

CI

## Internal Assessment Test 1

### Solution

| Sub:  | Digital Design and Computer Organization |           |         |            | Sub Code: | BCS302        | Branch: | CSE     |  |

|-------|------------------------------------------|-----------|---------|------------|-----------|---------------|---------|---------|--|

| Date: | 06/11/2024                               | Duration: | 90 mins | Max Marks: | 50        | Sem /<br>Sec: |         | 3 A,B,C |  |

| What is positive log                                                                                                                      | ic and negative logic?                                                                                                            |                                                                                                                        |

|-------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

| Positive logic and neg<br>relate to the voltages                                                                                          |                                                                                                                                   | s that define how logical values                                                                                       |

| Positive logic<br>A high voltage level re<br>Negative logic                                                                               | epresents a logic 1, and a low                                                                                                    | voltage level represents a logic 0.                                                                                    |

|                                                                                                                                           | epresents a logic 1, and a high                                                                                                   | voltage level represents a logic 0.                                                                                    |

| given as I/P in fou<br>'0000', February a                                                                                                 | as "0001" and so on. The o                                                                                                        | n the month of the year is<br>January is represented as<br>output of the system should<br>aining 31 days, or otherwise |

| care condition:<br>(i) Write truth tabl                                                                                                   | the excess number in the<br>le, SOP and POS form (ii)<br>e using basic gates                                                      | -                                                                                                                      |

| care condition:<br>(i) Write truth tabl<br>K-map (iii) Realize                                                                            | le, SOP and POS form (ii)                                                                                                         | -                                                                                                                      |

| care condition:<br>(i) Write truth tabl<br>K-map (iii) Realize                                                                            | le, SOP and POS form (ii)<br>e using basic gates                                                                                  | Simplify for SOP using                                                                                                 |

| care condition:<br>(i) Write truth tabl<br>K-map (iii) Realize<br><u>Truth Table</u><br>Name of Month                                     | le, SOP and POS form (ii)<br>e using basic gates<br>Month in binary                                                               | Simplify for SOP using Output ( F )                                                                                    |

| care condition:<br>(i) Write truth tabl<br>K-map (iii) Realize<br><u>Truth Table</u><br>Name of Month<br>January                          | le, SOP and POS form (ii)<br>e using basic gates<br>Month in binary                                                               | Simplify for SOP using Output ( F ) 1                                                                                  |

| care condition:<br>(i) Write truth table<br>K-map (iii) Realized<br>Truth Table<br>Name of Month<br>January<br>February                   | le, SOP and POS form (ii)<br>e using basic gates<br>Month in binary<br>0000<br>0001                                               | Simplify for SOP using Output ( F ) 1 0                                                                                |

| care condition:<br>(i) Write truth table<br>K-map (iii) Realized<br>Truth Table<br>Name of Month<br>January<br>February<br>March          | le, SOP and POS form (ii)<br>e using basic gates<br>Month in binary<br>0000<br>0001<br>0010                                       | Simplify for SOP using          Output ( F )         1         0         1                                             |

| care condition:<br>(i) Write truth table<br>K-map (iii) Realized<br>Truth Table<br>Name of Month<br>January<br>February<br>March<br>April | Ie, SOP and POS form (ii)         e using basic gates         Month in binary         0000         0001         0010         0011 | Simplify for SOP using Output ( F ) 1 0 1 0 0 0 0                                                                      |

| August    | 0111 | 1 |

|-----------|------|---|

| September | 1000 | 0 |

| October   | 1001 | 1 |

| November  | 1010 | 0 |

| December  | 1011 | 1 |

|           | 1100 | x |

|           | 1101 | x |

|           | 1110 | x |

|           | 1111 | х |

#### SOP Form:

$\Sigma m = m0 + m2 + m4 + m6 + m7 + m9 + m11 + d12 + d13 + d14 + d15$  $Y = \Sigma m(0,2,4,6,7,9,11) + d(12,13,14,15)$

### POS Form :

$\pi M = M1+M3+M5+M8+M10+D12 + D13 + D14 + D15$

$Y = \pi M(1,3,5,8,10) + D(12,13,14,15)$

| 2 a) | Define 1.Implicant 2.Prime Implicant 3.Essential Prime Implicant<br>4. Redundant prime implicant<br>Identify Prime implicant and essential prime implicant |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | f(A,B,C,D)=∑m(1,3,4,5,10,11,12,13,14,15)                                                                                                                   |

|      | Implicant is a product/minterm term in Sum of Products (SOP) or                                                                                            |

|      | sum/maxterm term in Product of Sums (POS) of a Boolean function.                                                                                           |

|      | A group of squares or rectangles made up of a bunch of adjacent<br>minterms which is allowed by the definition of K-Map are called <b>prime</b>            |

|      | implicants(PI)                                                                                                                                             |

|      | These are those subcubes(groups) that cover at least one minterm<br>that can't be covered by any other prime implicant. Essential prime                    |

|      | implicants(EPI) are those prime implicants that always appear in the final solution.                                                                       |

|      | The prime implicants for which each of its minterm is covered by                                                                                           |

|      | some essential prime implicant are redundant prime implicants(RPI).                                                                                        |

|      | This prime implicant never appears in the final solution.                                                                                                  |

|      |                                                                                                                                                            |

|      |                                                                                                                                                            |

|      |                                                                                                                                                            |

|      |                                                                                                                                                            |

|      |                                                                                                                                                            |

|      |                                                                                                                                                            |

|      |                                                                                                                                                            |

|      |                                                                                                                                                            |

|      |                                                                                                                                                            |

|      |                                                                                                                                                            |

|      |                                                                                                                                                            |

|      |                                                                                                                                                            |

CD AB (3 и Prime Implicants BC ' ABD AC b) AB EPI: BC', A'B'D, AC Redundant PI : AB

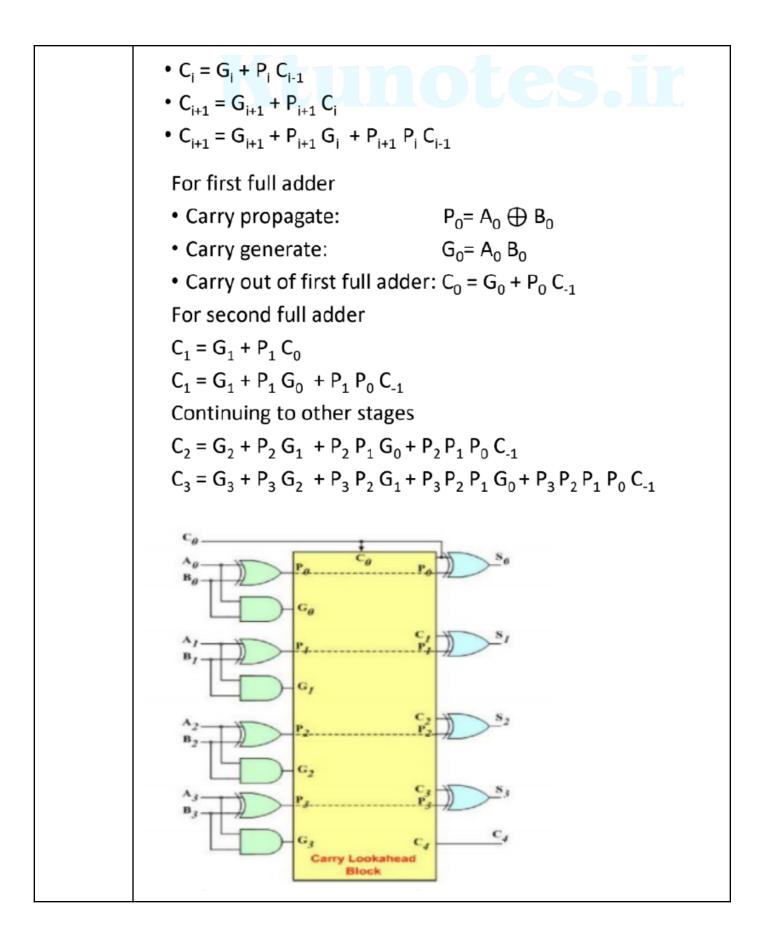

| 3 | a)What is the drawback of n-bit ripple carry adder? Design and explain 4 bit carry look ahead adder                                                                                                                                                                                                      |

|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | The main drawback of an n-bit ripple carry adder is that it can be slow when the value of (N) is large. This is because each full adder must wait for the carry-in from the previous full adder. This means that the nth full adder must wait until all (n-1) full adders have finished their operations |

|   | Carry Look Ahead Adder                                                                                                                                                                                                                                                                                   |

|   | Overcomes the drawback of Parallel adder                                                                                                                                                                                                                                                                 |

|   | <ul> <li>Sum and carry outputs of each stage are made independent of the<br/>results of previous stages- ripple effect is eliminated</li> </ul>                                                                                                                                                          |

|   | Uses concept of look-ahead carry                                                                                                                                                                                                                                                                         |

|   | <ul> <li>Requires additional circuitry but speed becomes independent of<br/>number of bits (or stages)</li> </ul>                                                                                                                                                                                        |

|   | • $C_i = A_i B_i + C_{i-1} (A_i \bigoplus B_i)$                                                                                                                                                                                                                                                          |

|   | • Let $P_i$ be carry propogate, $P_i = A_i \bigoplus B_i$                                                                                                                                                                                                                                                |

|   | • Let $G_i$ be carry generate , $G_i = A_i B_i$                                                                                                                                                                                                                                                          |

|   |                                                                                                                                                                                                                                                                                                          |

|   |                                                                                                                                                                                                                                                                                                          |

|   |                                                                                                                                                                                                                                                                                                          |

|   |                                                                                                                                                                                                                                                                                                          |

```

3 b)

Write a Verilog HDL code to simulate the working of Half adder and Full

adder in data flow and structural model

HALF ADDER

Dataflow Modelling

module half adder (

input a,b,

output sum, carry

);

assign sum = a ^ b;

assign carry = a & b;

endmodule

Structural

module half adder (

input a,b,

output sum, carry

);

xor (s, a, b);

and(c, a, b);

endmodule

FULL ADDER

Dataflow Modelling

module full adder d (

input a,b,cin,

output sum, carry

);

assign sum = a ^ b ^ cin;

assign carry = (a \& b) | (b \& cin) | (cin \& a)

;

endmodule

```

```

Structural Modeling

```

```

module full adder s (

input a, b, cin,

output sum, carry

);

wire w1,w2,w3,w4; //Internal connections

xor(w1,a,b);

//Sum output

xor(sum,w1,cin);

and (w2, a, b);

and(w3,b,cin);

and(w4,cin,a);

or(carry,w2,w3,w4); //carry output

endmodule

Implement Y (A, B, C, D) = ∑m (0, 1, 6, 7, 8, 9, 10, 11, 12, 14) using 8-to-1

4 a)

multiplexer.

```

|      | <u> </u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | STEPS FOR INSTRUCTION EXECUTION<br>Consider the following instruction<br>Ex: 1 Add LOCA, R0                                                                                                                                                                                                                                                                                                                                                                                                     |

|      | This instruction is in the form of the following instruction format                                                                                                                                                                                                                                                                                                                                                                                                                             |

|      | Opcode Source, Destination                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|      | Where Add is the operation code, LOCA is the Memory operand and R0 is<br>Register operand This instruction adds the contents of memory location LOCA<br>with the contents of Register R0 and the result is stored in R0 Register.<br>The symbolic representation of this instruction is<br>$R0 \leftarrow [LOCA] + [R0]$                                                                                                                                                                        |

| 5 b) | The contents of memory location LOCA and Register R0 before and after the execution of this instruction is as follows<br>Before instruction execution After instruction execution<br>LOCA = 23H LOCA = 23H<br>R0 = 22H R0 = 45H                                                                                                                                                                                                                                                                 |

|      | <ul> <li>The steps for instruction execution are as follows</li> <li>1. Fetch the instruction from memory into the IR (instruction register in CPU).</li> <li>2. Decode the instruction 1111000000 10011010</li> <li>3. Access the Memory Operand</li> <li>4. Access the Register Operand</li> <li>5. Perform the operation according to the Operation Code.</li> <li>6. Store the result into the Destination Memory location or Destination Register.</li> <li>Ex:2 Add R1, R2, R3</li> </ul> |

|      | This instruction is in the form of the following instruction format<br>Opcode, Source-1, Source-2, Destination                                                                                                                                                                                                                                                                                                                                                                                  |

|      | Where R1 is Source Operand-1, R2 is the Source Operand-2 and R3 is the Destination. This instruction adds the contents of Register R1 with the contents of R2 and the result is placed in R3 Register.                                                                                                                                                                                                                                                                                          |

|      | The symbolic representation of this instruction is $R3 \leftarrow [R1] + [R2]$                                                                                                                                                                                                                                                                                                                                                                                                                  |

|      | The contents of Registers R1,R2,R3 before and after the execution of this instruction is as follows.<br>Before instruction execution After instruction execution                                                                                                                                                                                                                                                                                                                                |

|      | Flip-Flop                                                                                                                   | Latch                                                                                         |

|------|-----------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|

| 6 b) | Flip-flop is a bistable device i.e., it has two stable states that are represented as 0 and 1.                              | Latch is also a bistable device<br>whose states are also<br>represented as 0 and 1.           |

|      | It checks the inputs but changes the<br>output only at times defined by the<br>clock signal or any other control<br>signal. | It checks the inputs<br>continuously and responds to<br>the changes in inputs<br>immediately. |

|      | It is a edge triggered device.                                                                                              | It is a level triggered device.                                                               |

|      | Gates like <u>NOR, NOT</u> , <u>AND</u> , <u>NAND</u><br>are building blocks of flip flops.                                 | These are also made up of gates.                                                              |

|      | They are classified into asynchronous or synchronous flipflops.                                                             | There is no such classification in latches                                                    |

|      | Flip-flop always have a clock signal                                                                                        | Latches doesn't have a clock<br>signal                                                        |

|      | ex: <u>D Flip-flop, JK Flip-flop</u>                                                                                        | ex:SR Latch, D Latch                                                                          |