## Internal Assessment Test 2 – December 2024

| Sub:  | Digital Desig                                                                                       | gn and Cor                                                                                | nputer Orga    | nization                         |                | Sub Code:      | BCS302            | Bra         | unch: | CSE  | 3  |     |

|-------|-----------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|----------------|----------------------------------|----------------|----------------|-------------------|-------------|-------|------|----|-----|

| Date: | 10/12/2024                                                                                          | 10/12/2024 Duration: 90 minutes Max Marks: 50 Sem / Sec:   Answer any FIVE FULL Questions |                |                                  |                |                |                   | I / A, B, C |       |      | OB | Е   |

|       |                                                                                                     | 4                                                                                         | Answer any FI  | VE FULL Ouesti                   | ons            |                |                   |             | М     | IARK | СО | RBT |

|       | •                                                                                                   |                                                                                           |                |                                  |                |                |                   |             | S     |      |    |     |

|       | a) Write a pro                                                                                      | •                                                                                         | an evaluate th | ne expression (A                 | <b>A-B</b> ) ∙ | + (C*D) usin   | g One and Tw      | 0           | г     | 3+2] | 3  | L3  |

| 1     | address ins                                                                                         | truction                                                                                  |                |                                  |                |                |                   |             | L     | 512] | 5  | 1.5 |

|       | Ans-                                                                                                |                                                                                           |                |                                  |                |                |                   |             |       |      |    |     |

|       | Two-Address                                                                                         |                                                                                           | -              |                                  |                |                |                   |             |       |      |    |     |

|       | MOV R1, A                                                                                           |                                                                                           | ve A into reg  |                                  | •              |                |                   |             |       |      |    |     |

|       | SUB R1, B                                                                                           |                                                                                           |                | R1 (R1 = A - I)                  | 3)             |                |                   |             |       |      |    |     |

|       | MOV R2, C                                                                                           |                                                                                           | love C into r  | •                                |                |                |                   |             |       |      |    |     |

|       | MUL R2, D                                                                                           |                                                                                           | dd R2 (C * I   | th R2 (R2 = C * $\mathbb{R}^{1}$ | * D)           |                |                   |             |       |      |    |     |

|       | ADD R1, R2<br>MOV RESULT                                                                            |                                                                                           |                | l result from R1                 | linto          | momory DE      |                   |             |       |      |    |     |

|       | MOV RESULI                                                                                          | , KI //N                                                                                  | Tove the fina  | I result from K                  | i into         | memory RE      | SULI              |             |       |      |    |     |

|       | One address                                                                                         |                                                                                           |                |                                  |                |                |                   |             |       |      |    |     |

|       | LOAD A                                                                                              |                                                                                           | // Load A i    | nto the accumu                   | lator          |                |                   |             |       |      |    |     |

|       | SUB B                                                                                               |                                                                                           |                | from the accun                   |                | or             |                   |             |       |      |    |     |

|       | STORE T1                                                                                            |                                                                                           | //Store the    |                                  |                | ~ -            |                   |             |       |      |    |     |

|       | LOAD C                                                                                              | /                                                                                         |                | the accumulato                   | r              |                |                   |             |       |      |    |     |

|       | MUL D                                                                                               |                                                                                           |                | with the accum                   |                | r              |                   |             |       |      |    |     |

|       | STORE T2                                                                                            |                                                                                           |                | ult (C * D) into                 |                |                |                   |             |       |      |    |     |

|       | LOAD T1                                                                                             |                                                                                           |                | o the accumulat                  |                |                |                   |             |       |      |    |     |

|       | ADD T2                                                                                              |                                                                                           |                | e accumulator (                  |                | C = (A - B) +  | (C * D))          |             |       |      |    |     |

|       | STORE RESU                                                                                          |                                                                                           |                | l result into RE                 |                |                |                   |             |       |      |    |     |

|       |                                                                                                     |                                                                                           |                |                                  |                |                |                   |             |       |      |    |     |

|       | N.B- "//" are c                                                                                     | omment lin                                                                                | ies            |                                  |                |                |                   |             |       |      |    |     |

|       | (b) Explain any                                                                                     | 5 addressir                                                                               | ig modes.      |                                  |                |                |                   |             | ſ     | 5]   | 3  | L3  |

|       | Ans                                                                                                 |                                                                                           |                |                                  |                |                |                   |             |       | 5]   | 5  | 23  |

|       | The various form                                                                                    |                                                                                           |                |                                  |                |                | an operand is c   | alled       |       |      |    |     |

|       | as "Addressing"                                                                                     |                                                                                           | different type | es of Addressing                 | g Moc          | les are        |                   |             |       |      |    |     |

|       | a) Register Add                                                                                     | e                                                                                         |                |                                  |                |                |                   |             |       |      |    |     |

|       | <ul><li>b) Direct Addres</li><li>c) Immediate Addres</li></ul>                                      | •                                                                                         |                |                                  |                |                |                   |             |       |      |    |     |

|       | d) Indirect Addr                                                                                    | U                                                                                         |                |                                  |                |                |                   |             |       |      |    |     |

|       | e) Relative Add                                                                                     | •                                                                                         |                |                                  |                |                |                   |             |       |      |    |     |

|       |                                                                                                     | 0                                                                                         |                |                                  |                |                |                   |             |       |      |    |     |

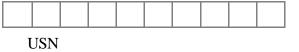

|       | a. REGISTER                                                                                         | ADDRESS                                                                                   | ING:           |                                  |                |                |                   |             |       |      |    |     |

|       | In this mode ope                                                                                    |                                                                                           | ored in the re | gisters of CPU.                  | The n          | ame of the re  | gister is directl | у           |       |      |    |     |

|       | specified in the                                                                                    |                                                                                           |                |                                  | _              |                |                   |             |       |      |    |     |

|       | Ex: MOVE R1,                                                                                        | R2 Where F                                                                                | R1 and R2 are  | the Source and                   | Desti          | nation registe | ers respectively  | •           |       |      |    |     |

|       | This                                                                                                | 6 2011                                                                                    | C 1 4 C T      | <b>N1 1</b>                      |                |                |                   |             |       |      |    |     |

|       | instruction trans                                                                                   |                                                                                           |                | -                                |                |                |                   |             |       |      |    |     |

|       | into R2 register. This instruction does not refer<br>memory for operands. The operands are directly |                                                                                           |                |                                  |                |                |                   |             |       |      |    |     |

|       | available in the                                                                                    |                                                                                           | peranus are c  | meetty                           |                |                |                   |             |       |      |    |     |

|       | available in the                                                                                    | iegisters.                                                                                |                |                                  |                |                |                   |             | I     |      |    | 1   |

|              |                                                                                                                |                                                                                                   |                                                             |      | Т |     |

|--------------|----------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|-------------------------------------------------------------|------|---|-----|

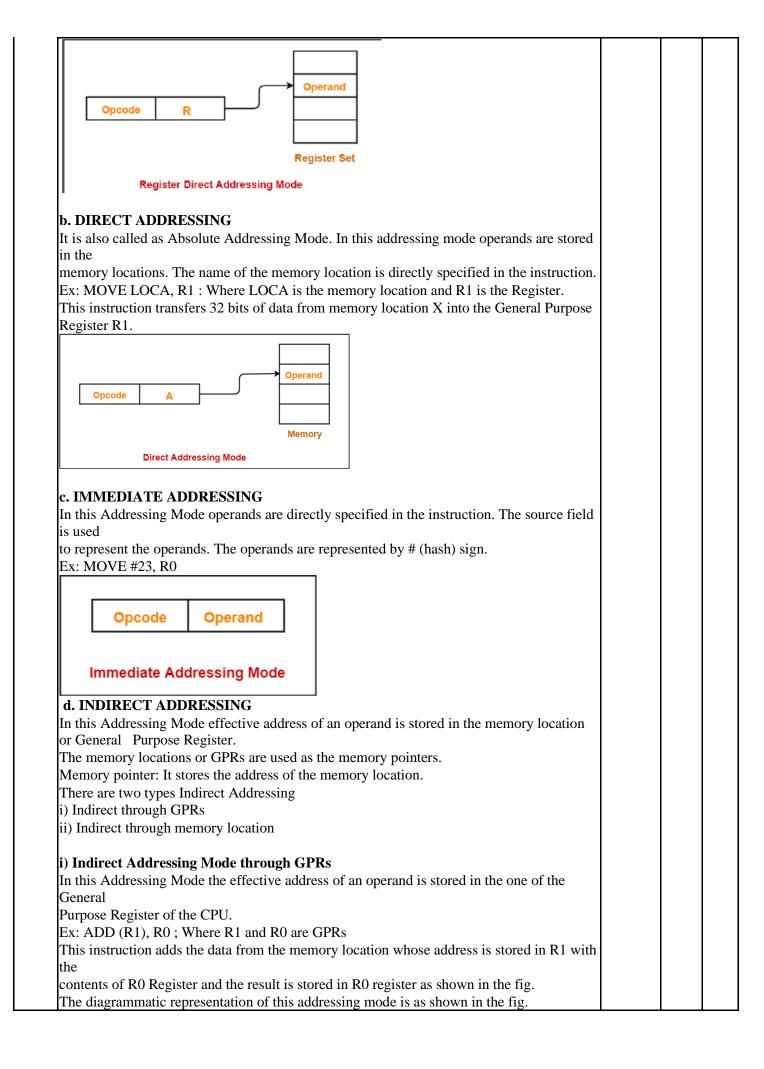

|              | Effectiv<br>= Content of Program Counter                                                                       | re Address                                                                                        | ction                                                       |      |   |     |

|              |                                                                                                                |                                                                                                   |                                                             |      |   |     |

|              | <b></b>                                                                                                        |                                                                                                   |                                                             |      |   |     |

|              |                                                                                                                |                                                                                                   |                                                             |      |   |     |

|              | Opcode A                                                                                                       |                                                                                                   |                                                             |      |   |     |

|              |                                                                                                                |                                                                                                   | -                                                           |      |   |     |

|              |                                                                                                                | Operand                                                                                           |                                                             |      |   |     |

|              | $\downarrow$                                                                                                   | )                                                                                                 |                                                             |      |   |     |

|              |                                                                                                                |                                                                                                   |                                                             |      |   |     |

|              | Relative Addressing Mode   Addressin                                                                           | g Modes Memory                                                                                    |                                                             |      |   |     |

|              | PC                                                                                                             |                                                                                                   |                                                             |      |   |     |

|              | Relative Addre                                                                                                 | essing Mode                                                                                       |                                                             |      |   |     |

|              |                                                                                                                |                                                                                                   |                                                             |      |   |     |

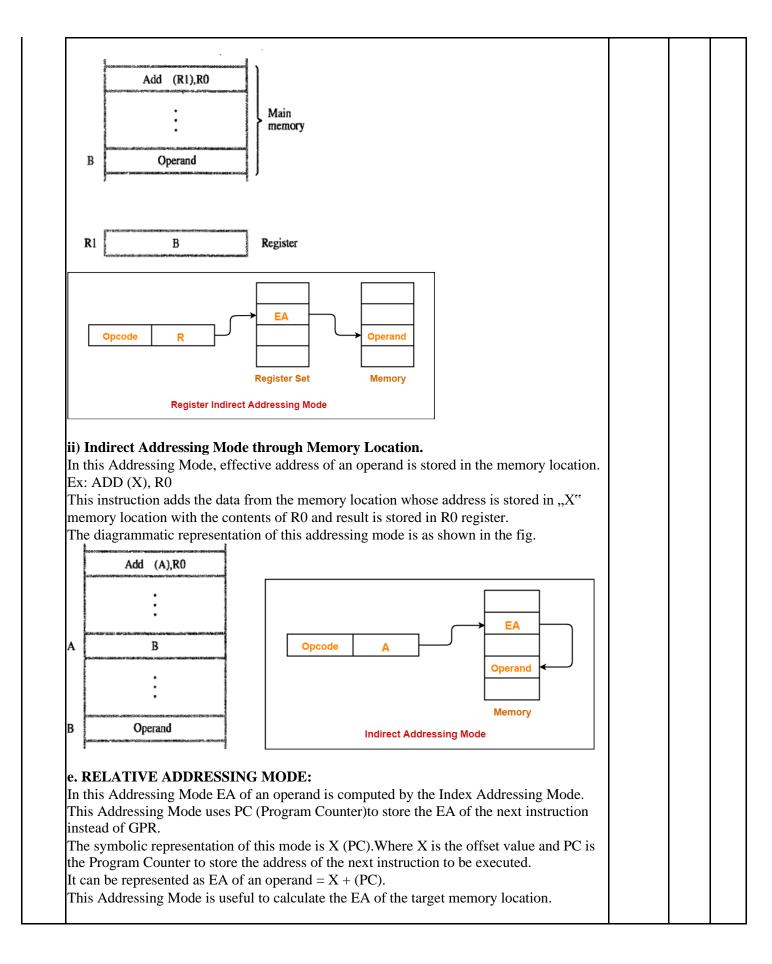

| N R Foll     | owing is the summary o                                                                                         | f all addressing mod                                                                              | es. Don't write only the table.                             |      |   |     |

|              |                                                                                                                | ric addressing modes                                                                              | .s. Don't write only the table.                             |      |   |     |

|              | alan an and a salar data balanca data baha baha sayaba birda                                                   |                                                                                                   |                                                             |      |   |     |

|              | Nапре                                                                                                          | Assembler syntax                                                                                  | Addressing function                                         |      |   |     |

|              | Immediate                                                                                                      | #Value                                                                                            | Operand = Value                                             |      |   |     |

|              | Register                                                                                                       | Ri                                                                                                | $\mathbf{E}\mathbf{A} = \mathbf{R}i$                        |      |   |     |

|              | Absolute (Direct)                                                                                              | LOC                                                                                               | EA = LOC                                                    |      |   |     |

|              | Indirect                                                                                                       | (Ri)                                                                                              | EA = [Ri]                                                   |      |   |     |

|              |                                                                                                                | (LOC)                                                                                             | EA = [LOC]                                                  |      |   |     |

|              | - Index                                                                                                        | X(Ri)                                                                                             | $\mathbf{E}\mathbf{A} = [\mathbf{R}i] + \mathbf{X}$         |      |   |     |

|              | Base with index                                                                                                | (Ri,Rj)                                                                                           | $\mathbf{E}\mathbf{A} = [\mathbf{R}i] + [\mathbf{R}j]$      |      |   |     |

|              | Base with index<br>and offset                                                                                  | X(Ri,Rj)                                                                                          | EA = [Ri] + [Rj] + X                                        |      |   |     |

|              | Relative                                                                                                       | X(PC)                                                                                             | EA = [PC] + X                                               |      |   |     |

|              | Autoincrement                                                                                                  | (Ri)+                                                                                             | EA = [Ri];<br>Increment Ri                                  |      |   |     |

|              | Autodecrement                                                                                                  | ( <b>R</b> <i>i</i> )                                                                             | Decrement Ri;                                               |      |   |     |

|              |                                                                                                                |                                                                                                   | $EA=\{Ri\}$                                                 |      |   |     |

|              | ى يەرىپىيە يەتىرىكە بەرىپىيە يەتىيە بەرىپەر يەتىيە بەرىپەر يەتىيە بەرىپەر يەتىيە يەتىپەر يەتىيە يەتىپەر يەتىيە | na yanga ana pila 15 ki kipang perjaharan dari perjaman di kara dari bir dari kara di kara dari k | 1998-1439 - 48-4993-1997-1997-1997-1997-1997-1997-1997-1    |      |   |     |

|              | ·;   EA = effective address<br>Value = a signed num                                                            | ber                                                                                               |                                                             |      |   |     |

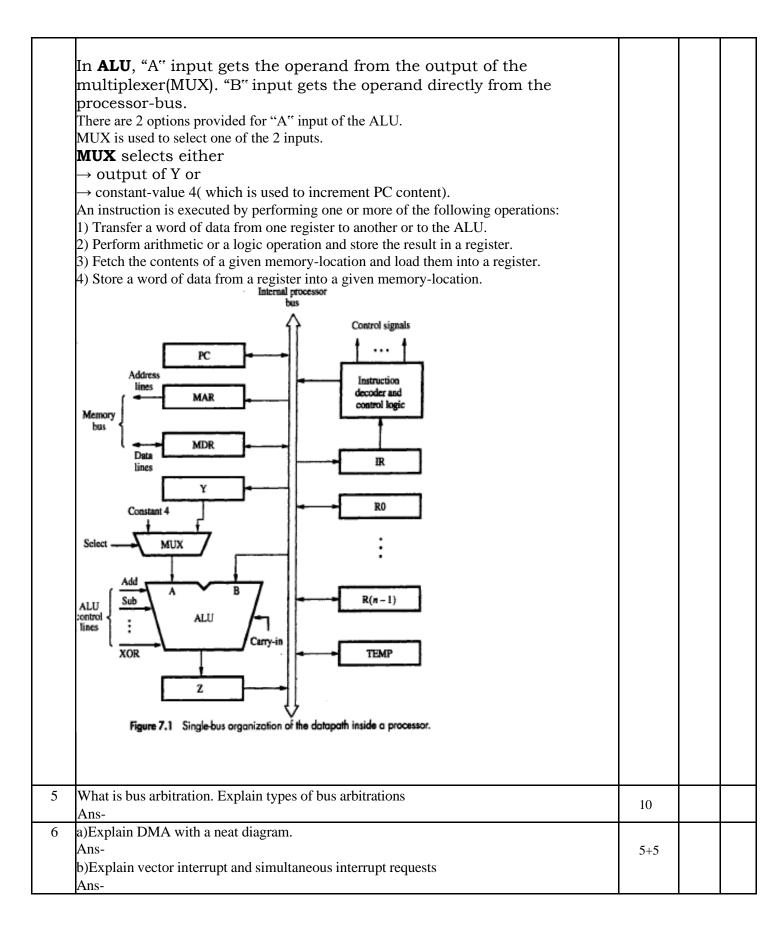

| What is Ans- | cache memory ? Explain                                                                                         | different type of cache                                                                           | mapping function.                                           | [10] | 4 | L2  |

|              | What is pipeline ? Explain                                                                                     | different pipeline haz                                                                            | ards.                                                       | [5]  | 5 | L2  |

|              |                                                                                                                |                                                                                                   | rganizing concurrent                                        | [J]  | 5 | 1.2 |

| -            | in a computer syste                                                                                            |                                                                                                   | -                                                           |      |   |     |

| ÷            |                                                                                                                |                                                                                                   | n instruction into separate<br>c task. This allows multiple |      |   |     |

|              |                                                                                                                |                                                                                                   | in a "pipeline," significantly                              |      |   |     |

|              | ing instruction thro                                                                                           |                                                                                                   | · · / / · · · ·                                             |      |   |     |

|              | ecution of an instruc                                                                                          | ction in a pipeline                                                                               | is divided into stages, such                                |      |   |     |

| as:          |                                                                                                                |                                                                                                   |                                                             |      | 1 | 1   |

|                                                                                                                                                                                                                               | Instructio<br>operation a                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                             | • •                                                                                                                                                                                                                           | ecode the                                                                                                                                                                                                   |                                                                                                                                                                         | uon and                                                                                                                                                                   | luenti                                                                                             | iy the                                    |     |       |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|-------------------------------------------|-----|-------|--|

|                                                                                                                                                                                                                               | Execute (I                                                                                                                                                                                                                                                                                                                 | -                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                               | peration                                                                                                                                                                                                    | (e.g. ari                                                                                                                                                               | ithmetic                                                                                                                                                                  | or logi                                                                                            | c).                                       |     |       |  |

|                                                                                                                                                                                                                               | Memory A                                                                                                                                                                                                                                                                                                                   | •                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                               | -                                                                                                                                                                                                           |                                                                                                                                                                         |                                                                                                                                                                           | -                                                                                                  | ,                                         |     |       |  |

|                                                                                                                                                                                                                               | required.                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                             | ,                                                                                                                                                                                                                             |                                                                                                                                                                                                             |                                                                                                                                                                         | ,                                                                                                                                                                         | j                                                                                                  | ,                                         |     |       |  |

| 5.                                                                                                                                                                                                                            | Write Bac                                                                                                                                                                                                                                                                                                                  | <b>k (WB):</b> W                                                                                                                                                                                                                                                                                                                                                                                            | /rite the                                                                                                                                                                                                                     | result ba                                                                                                                                                                                                   | ick to the                                                                                                                                                              | e register                                                                                                                                                                |                                                                                                    |                                           |     |       |  |

| Each s                                                                                                                                                                                                                        | stage works                                                                                                                                                                                                                                                                                                                | s concurr                                                                                                                                                                                                                                                                                                                                                                                                   | ently on                                                                                                                                                                                                                      | a differer                                                                                                                                                                                                  | nt instru                                                                                                                                                               | ction. Fo                                                                                                                                                                 | or exan                                                                                            | nple:                                     |     |       |  |

| •                                                                                                                                                                                                                             | While instr                                                                                                                                                                                                                                                                                                                | ruction 1                                                                                                                                                                                                                                                                                                                                                                                                   | is in the                                                                                                                                                                                                                     | Decode                                                                                                                                                                                                      | stage, in                                                                                                                                                               | struction                                                                                                                                                                 | n 2 is in                                                                                          | n the                                     |     |       |  |

|                                                                                                                                                                                                                               | Fetch stage                                                                                                                                                                                                                                                                                                                | e, and ins                                                                                                                                                                                                                                                                                                                                                                                                  | struction                                                                                                                                                                                                                     | 3 can er                                                                                                                                                                                                    | nter the p                                                                                                                                                              | pipeline.                                                                                                                                                                 |                                                                                                    |                                           |     |       |  |

|                                                                                                                                                                                                                               | Clock Cycle                                                                                                                                                                                                                                                                                                                | IF                                                                                                                                                                                                                                                                                                                                                                                                          | ID                                                                                                                                                                                                                            | EX                                                                                                                                                                                                          | MEM                                                                                                                                                                     | WB                                                                                                                                                                        |                                                                                                    |                                           |     |       |  |

|                                                                                                                                                                                                                               | 1                                                                                                                                                                                                                                                                                                                          | Instr 1                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                               |                                                                                                                                                                                                             |                                                                                                                                                                         |                                                                                                                                                                           |                                                                                                    |                                           |     |       |  |

|                                                                                                                                                                                                                               | 2                                                                                                                                                                                                                                                                                                                          | Instr 2                                                                                                                                                                                                                                                                                                                                                                                                     | Instr 1                                                                                                                                                                                                                       |                                                                                                                                                                                                             |                                                                                                                                                                         |                                                                                                                                                                           |                                                                                                    |                                           |     |       |  |

|                                                                                                                                                                                                                               | 3                                                                                                                                                                                                                                                                                                                          | Instr 3                                                                                                                                                                                                                                                                                                                                                                                                     | Instr 2                                                                                                                                                                                                                       | Instr 1                                                                                                                                                                                                     |                                                                                                                                                                         |                                                                                                                                                                           |                                                                                                    |                                           |     |       |  |

|                                                                                                                                                                                                                               | 4                                                                                                                                                                                                                                                                                                                          | Instr 4                                                                                                                                                                                                                                                                                                                                                                                                     | Instr 3                                                                                                                                                                                                                       | Instr 2                                                                                                                                                                                                     | Instr 1                                                                                                                                                                 |                                                                                                                                                                           |                                                                                                    |                                           |     |       |  |

| •                                                                                                                                                                                                                             | 5                                                                                                                                                                                                                                                                                                                          | Instr 5                                                                                                                                                                                                                                                                                                                                                                                                     | Instr 4                                                                                                                                                                                                                       | Instr 3                                                                                                                                                                                                     | Instr 2                                                                                                                                                                 | Instr 1                                                                                                                                                                   |                                                                                                    |                                           |     |       |  |

|                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                               |                                                                                                                                                                                                             |                                                                                                                                                                         |                                                                                                                                                                           |                                                                                                    |                                           |     |       |  |

| Any con                                                                                                                                                                                                                       | dition that ca                                                                                                                                                                                                                                                                                                             | uses the nin                                                                                                                                                                                                                                                                                                                                                                                                | eline to sta                                                                                                                                                                                                                  | ll is called :                                                                                                                                                                                              | a hazard                                                                                                                                                                |                                                                                                                                                                           |                                                                                                    |                                           |     |       |  |

| -                                                                                                                                                                                                                             | it types hazard                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                               |                                                                                                                                                                                                             | u 11u2ul U.                                                                                                                                                             |                                                                                                                                                                           |                                                                                                    |                                           |     |       |  |

|                                                                                                                                                                                                                               | n types hazalt                                                                                                                                                                                                                                                                                                             | 15 al <b>C</b> -                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                               |                                                                                                                                                                                                             |                                                                                                                                                                         |                                                                                                                                                                           |                                                                                                    |                                           |     |       |  |

| 1                                                                                                                                                                                                                             | A <b>A</b> / A                                                                                                                                                                                                                                                                                                             | <b>.</b>                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                               |                                                                                                                                                                                                             | 4                                                                                                                                                                       | 4                                                                                                                                                                         | • • •                                                                                              |                                           |     |       |  |

|                                                                                                                                                                                                                               | A data hazar                                                                                                                                                                                                                                                                                                               | -                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                               |                                                                                                                                                                                                             |                                                                                                                                                                         |                                                                                                                                                                           |                                                                                                    | tion                                      |     |       |  |

|                                                                                                                                                                                                                               | operands of a pipeline. As a                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                               |                                                                                                                                                                                                             |                                                                                                                                                                         |                                                                                                                                                                           |                                                                                                    | ctallc                                    |     |       |  |

|                                                                                                                                                                                                                               | Control haza                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                               |                                                                                                                                                                                                             |                                                                                                                                                                         |                                                                                                                                                                           |                                                                                                    |                                           |     |       |  |

|                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                            | it us of misu                                                                                                                                                                                                                                                                                                                                                                                               | ruction na                                                                                                                                                                                                                    | Larus. The                                                                                                                                                                                                  | DIDENNE III                                                                                                                                                             | av also be                                                                                                                                                                | sianeu i                                                                                           | ecause                                    |     |       |  |

|                                                                                                                                                                                                                               | of a <b>delay in</b> :                                                                                                                                                                                                                                                                                                     | the availahi                                                                                                                                                                                                                                                                                                                                                                                                | ility of an i                                                                                                                                                                                                                 | instruction                                                                                                                                                                                                 |                                                                                                                                                                         |                                                                                                                                                                           | Stante a c                                                                                         | Jeeuuse                                   |     |       |  |

|                                                                                                                                                                                                                               | of a <b>delay in</b> a second                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                             | -                                                                                                                                                                                                                             |                                                                                                                                                                                                             | <b>1</b> .                                                                                                                                                              |                                                                                                                                                                           | 5                                                                                                  | Jeeuuse                                   |     |       |  |

| For                                                                                                                                                                                                                           | example, this                                                                                                                                                                                                                                                                                                              | may be a <b>re</b>                                                                                                                                                                                                                                                                                                                                                                                          | esult of a n                                                                                                                                                                                                                  | niss in the                                                                                                                                                                                                 | n.<br>cache .                                                                                                                                                           |                                                                                                                                                                           |                                                                                                    |                                           |     |       |  |