|       | <br> | <br> | <br> | <br> | <br> |

|-------|------|------|------|------|------|

| TICNT |      |      |      |      |      |

|       |      |      |      |      |      |

| ODI   |      |      |      |      |      |

|       |      |      |      |      |      |

|       |      | <br> |      | <br> |      |

#### Internal Assessment Test 2 – December 2024

|     |     |                                                                                                                          |                                                       |                |                 |        |               | -          |       |      |     |     |     |

|-----|-----|--------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|----------------|-----------------|--------|---------------|------------|-------|------|-----|-----|-----|

| Su  | ıb: | Digital De                                                                                                               | sign and Co                                           | omputer Or     | ganization      |        | Sub Code:     | BCS302     | Brai  | nch: | AIM | L   |     |

| Dat | te: | 13/12/24                                                                                                                 | Duration:                                             | 90 minutes     | Max Marks:      | 50     | Sem/Sec:      | III ·      | -A, B | , C  |     | OBE |     |

|     |     |                                                                                                                          | Ans                                                   | wer any FIV    | /E FULL Qu      | estior | <u>IS</u>     |            |       | MAI  | RKS | со  | RBT |

| 1   | a   | Explain Dir                                                                                                              | Explain Direct Memory Access with neat diagram[10]4L2 |                |                 |        |               |            |       |      |     |     |     |

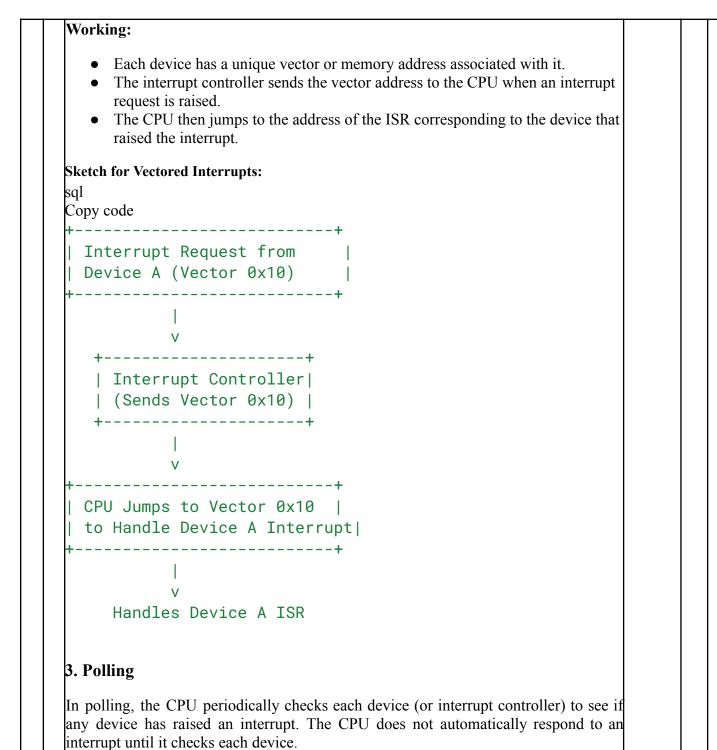

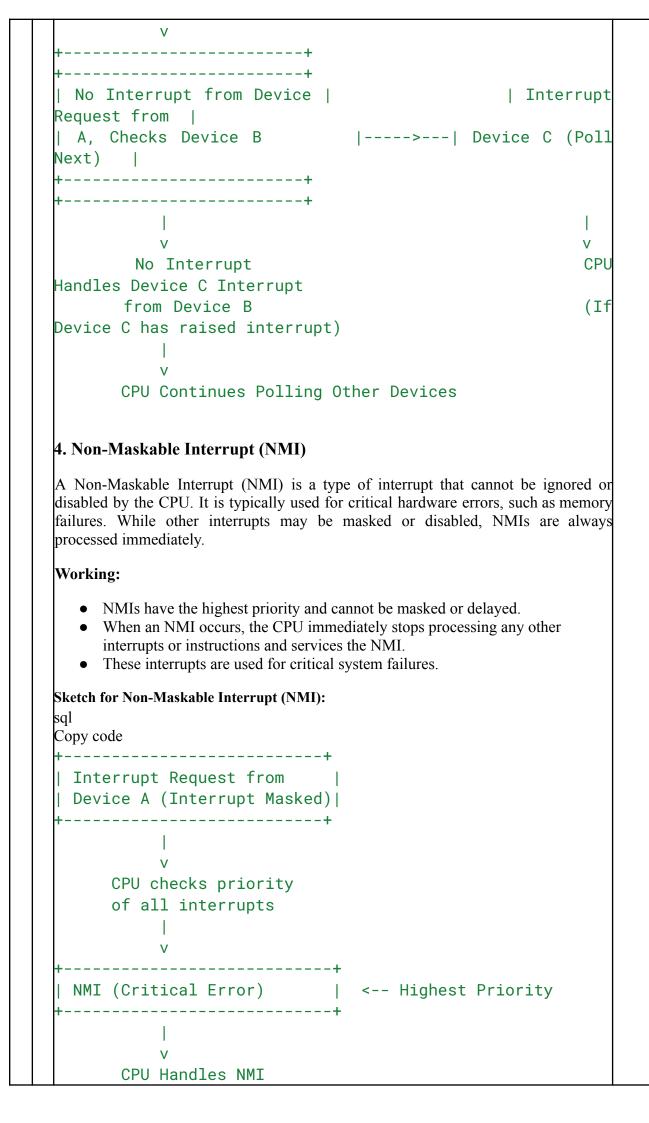

| 2   | a   | With neat sketches, explain various methods for handling multiple Interrupts<br>requests raised by Multiple devices.[10] |                                                       |                |                 |        |               |            | 4     | L1   |     |     |     |

| 3   | a   | What is Ca                                                                                                               | che memory                                            | ? Analyze th   | ne three mappi  | ing fu | nctions of C  | ache memo  | ry.   | [1   | 0]  | 4   | L2  |

| 4   | a   | Illustrate in                                                                                                            | detail the A                                          | LU operatio    | on in a process | or wit | h example.    |            |       | [1   | 0]  | 5   | L3  |

| 5   | a   | Analyze ho                                                                                                               | ow does exec                                          | cution of a co | omplete instru  | ction  | carry out     |            |       | [1   | 5   | L3  |     |

| 6   | a   | What is pip                                                                                                              | elining? Ex                                           | plain the per  | formance of th  | ne pip | eline with ar | n example. |       | [1   | 0]  | 5   | L2  |

CI

\_\_\_\_

# CCI

HoD

| USN |

|-----|

|-----|

| Su  | b:  | Digital De                                                                                                               | sign and Co | omputer Or    | ganization     |        | Sub Code:     | BCS302     | Bra   | nch: | AIM | [L  |     |

|-----|-----|--------------------------------------------------------------------------------------------------------------------------|-------------|---------------|----------------|--------|---------------|------------|-------|------|-----|-----|-----|

| Dat | te: | 13/12/24                                                                                                                 | Duration:   | 90 minutes    | Max Marks:     | 50     | Sem/Sec:      | III        | -A, B | , C  |     | OBE |     |

|     |     |                                                                                                                          | Ans         | wer any FIV   | /E FULL Qu     | estion | IS            |            |       | MAI  | RKS | СО  | RBT |

| 1   | a   | Explain Dir                                                                                                              | rect Memory | Access with   | h neat diagran | 1      |               |            |       | [1   | 0]  | 4   | L2  |

| 2   | a   | With neat sketches, explain various methods for handling multiple Interrupts<br>requests raised by Multiple devices.[10] |             |               |                |        |               |            | 0]    | 4    | L1  |     |     |

| 3   | a   | What is Ca                                                                                                               | che memory  | ? Analyze th  | ne three mappi | ng fu  | nctions of C  | ache memo  | ery.  | [1   | 0]  | 4   | L2  |

| 4   | a   | Illustrate in detail the ALU operation in a processor with example. [10]                                                 |             |               |                |        |               | 0]         | 5     | L3   |     |     |     |

| 5   | a   | Analyze how does execution of a complete instruction carry out [10]                                                      |             |               |                |        |               | 5          | L3    |      |     |     |     |

| 6   | a   | What is pip                                                                                                              | elining? Ex | plain the per | formance of th | ne pip | eline with an | n example. |       | [1   | 0]  | 5   | L2  |

| CI | CCI | HoD |

|----|-----|-----|

|    |     |     |

# USN

| Sub:  | Digital Design and C                                                                                                                                                                                                                                                                             | omputer Or                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ganization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Sub Code:                                                                                                                                                                                                                                                                                                                                     | BCS302                                                                                                                                                                                                                                 | Branch                | AIMI  |    |                 |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-------|----|-----------------|

| Date: | 13/12/24 Duration:                                                                                                                                                                                                                                                                               | 90<br>minutes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Max Marks:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Sem/Sec:                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                        | III                   | -     | C  | )BE             |

|       | <u>A</u>                                                                                                                                                                                                                                                                                         | iswer any F                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | IVE FULL Q                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | uestic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | <u>ons</u>                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                        |                       | MARKS | со | RBT             |

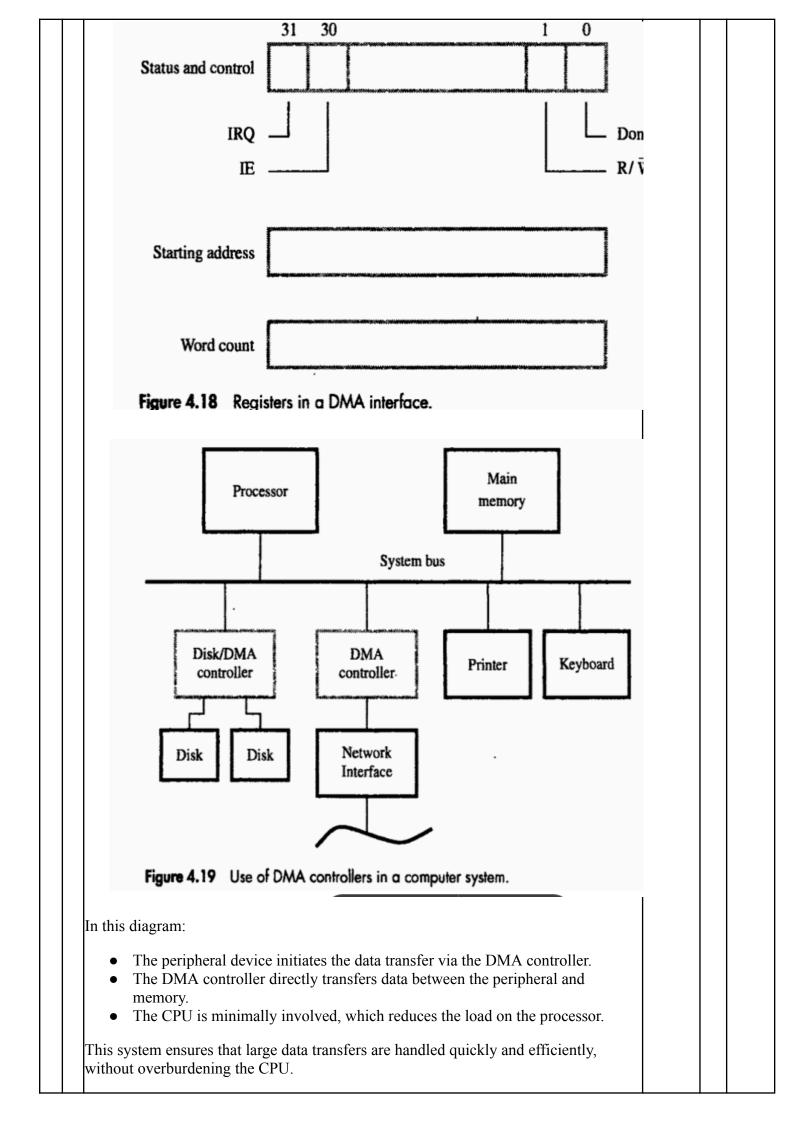

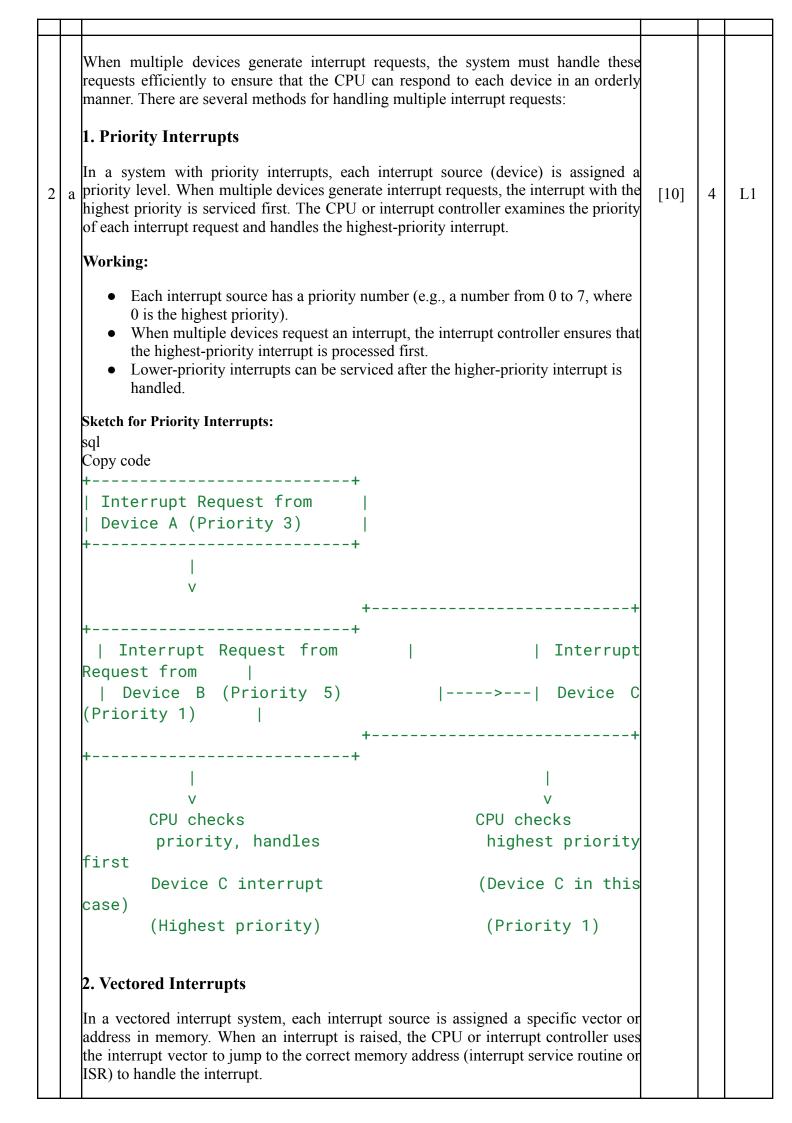

| 1 a   | Explain Direct Mem<br>Direct Memory Access<br>hard drives, sound cards<br>(RAM) directly, withou<br>offloading data transfer<br>movement.<br>How DMA Works<br>1. Peripheral Dev<br>to transfer data t<br>2. DMA Controlle<br>controller. The I<br>3. DMA Controlle<br>o It sends a<br>o Once the | (DMA) is a<br>s, or network<br>t involving t<br>tasks from t<br>s:<br>ice Request<br>o or from me<br>or (DMAC):<br>DMA control<br>or Actions:<br>a request to t<br>CPU ackno<br>memory bus<br>The DMA c<br>ne memory v<br>ice the trans:<br>CPU, notifyin<br>(IA: The DMA<br>the memory v<br>ice the trans:<br>CPU, notifyin<br>(IA: The DMA<br>the memory bus<br>The DMA c<br>ne memory the<br>the memory v<br>ice the trans:<br>CPU, notifyin<br>(IA: The DMA<br>the memory<br>DMA: The I<br>e of data at a<br>ng moved.<br>(IA: The DMA<br>the memory<br>DMA: The I<br>e of data at a<br>ng moved.<br>(IA: The DMA<br>the memory<br>DMA: The I<br>e of data at a<br>ng moved.<br>(IA: The DMA<br>the memory<br>DMA: The I<br>e of data at a<br>ng moved.<br>(IA: The DMA<br>the memory<br>DMA: The I<br>e of data at a<br>ng moved.<br>(IA: The DMA<br>the memory<br>DMA: The I<br>e of data at a<br>ng moved.<br>(IA: The DMA<br>the memory<br>DMA the I<br>e of data at a<br>ng moved.<br>(IA: The DMA<br>the memory<br>DMA the I<br>e of data at a<br>ng moved.<br>(IA: The DMA<br>the memory<br>DMA the I<br>e of data at a<br>ng moved.<br>(IA: The DMA<br>the I<br>e of data at a<br>ng moved.<br>(IA: The DMA<br>the memory<br>DMA the I<br>e of data at a<br>ng moved.<br>(IA: The DMA<br>the memory<br>DMA the I<br>e of data at a<br>ng moved.<br>(IA: The DMA<br>the memory<br>DMA the I<br>e of data at a<br>ng moved.<br>(IA: The DMA<br>the memory<br>DMA the I<br>e of data at a<br>ng moved.<br>(IA: The DMA<br>the memory<br>DMA the I<br>e of data at a<br>ng moved.<br>(IA: The DMA<br>the memory<br>DMA the I<br>e of data at a<br>ng moved.<br>(IA: The DMA<br>the memory<br>(IA: The DMA the | with neat diagr<br>with neat diagr<br>a feature that al<br>c interfaces) to<br>he CPU. DMA<br>he CPU, enable<br>c and the CPU, enable<br>emory.<br>The peripheral<br>ler manages the<br>che CPU to gra-<br>wledges, the D<br>c.<br>ontroller move<br>vithout involvi<br>fer is complete<br>ing it that the tr<br>IA controller the<br>during the tran<br>DMA controller the<br>during the tran<br>DMA controller the<br>controller the<br>during the tran<br>DMA controller the<br>during the tran<br>offloads data the<br>faster than inve<br>Enables high-sp | ram<br>llows<br>acces<br>impring fa<br>device<br>l sence<br>and account account<br>of a sence<br>and account account<br>and account account<br>and account account<br>and account account<br>and account account<br>and account account<br>and account account account<br>account account account<br>account account account<br>account account account<br>account account account account<br>account account account account<br>account account account account<br>account account account account account<br>account account account account account<br>account account account account account account<br>account account account account account account account account<br>account account | peripheral des<br>s the system<br>oves system<br>ster and more<br>e (e.g., a disl<br>ls a request the<br>a transfer pro-<br>controller tal-<br>data directly<br>e CPU.<br>DMA contron<br>r is done.<br>rs data in but<br>ls a cycle of<br>CPU to conti-<br>ers data in blue<br>he CPU is loc<br>er tasks, free<br>pommunication<br>g the CPU. | 's main me<br>performan<br>re efficient<br>a controller<br>o the DMA<br>ocess.<br>ory.<br>a control<br>between th<br>ller sends a<br>ursts, and th<br>the CPU's<br>nue proces<br>ocks witho<br>ocked out d<br>ing the CP<br>on between | mory<br>ce by<br>data | [10]  | 4  | RB <sup>-</sup> |

Working:

- The CPU regularly checks the status of each device to determine if it needs attention.

- The CPU queries all devices and handles the interrupt for the device that has requested it.

- Polling can waste CPU cycles if no device has raised an interrupt, as the CPU keeps checking.

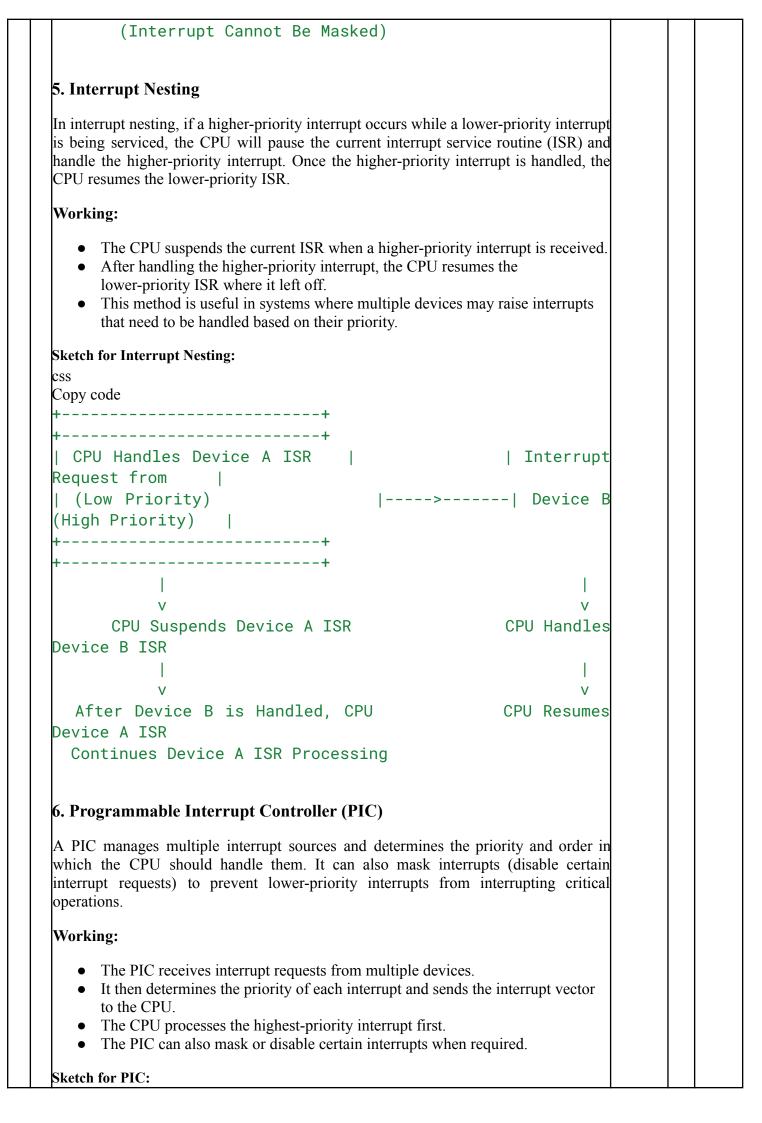

Sketch for Polling:

mathematica Copy code

#### +-----+ | CPU Checks Device A | | for Interrupt | +-----+

| Cache memory is a small, high-speed memory located between the CPU<br>and the main memory (RAM). Its primary purpose is to store frequently<br>accessed data and instructions to improve the speed and efficiency of the<br>system. The cache is faster than the main memory, and it helps reduce the<br>time it takes for the CPU to access data, significantly boosting system<br>performance. | [10] | 4 | L |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---|---|

| Cache memory works by storing copies of data from the main memory, so<br>when the CPU requests data, it first checks if it's available in the cache. If<br>the data is found (a cache hit), the CPU can access it much more quickly. If<br>the data is not found (a cache miss), it has to be fetched from the slower<br>main memory.                                                            |      |   |   |

| Three Mapping Functions of Cache Memory                                                                                                                                                                                                                                                                                                                                                          |      |   |   |

| In cache memory, mapping refers to the technique used to determine where<br>in the cache a particular block of data from main memory will be stored.<br>There are three main types of cache mapping:                                                                                                                                                                                             |      |   |   |

| <ol> <li>Direct-Mapped Cache</li> <li>Fully Associative Cache</li> <li>Set-Associative Cache</li> </ol>                                                                                                                                                                                                                                                                                          |      |   |   |

| Each method has its own approach to placing data into cache and differs in<br>terms of complexity, speed, and efficiency.                                                                                                                                                                                                                                                                        |      |   |   |

| 1. Direct-Mapped Cache                                                                                                                                                                                                                                                                                                                                                                           |      |   |   |

| In a direct-mapped cache, each block of memory can be mapped to exactly<br>one cache line. This means that for a given block of data in main memory,<br>there is a specific location in the cache where it will always be placed.                                                                                                                                                                |      |   |   |

| How it works:                                                                                                                                                                                                                                                                                                                                                                                    |      |   |   |

| • The memory address is divided into three parts: Tag, Index, and Block offset.                                                                                                                                                                                                                                                                                                                  |      |   |   |

| <ul> <li>Tag: Identifies which block of data in memory is being<br/>referenced.</li> </ul>                                                                                                                                                                                                                                                                                                       |      |   |   |

| <ul> <li>Index: Determines which cache line (or set) the block of data will be placed in.</li> <li>Block offset: Indicates the specific location within the cache line.</li> </ul>                                                                                                                                                                                                               |      |   |   |

| Example:                                                                                                                                                                                                                                                                                                                                                                                         |      |   |   |

| If you have a cache with 4 lines and memory with 16 blocks, the index will determine which cache line a block of data from memory should go into.                                                                                                                                                                                                                                                |      |   |   |

Each block of memory will be mapped to exactly one line in the cache.

- Advantages:

- Simple and fast, since each block of memory is mapped to a specific cache line.

- Low hardware complexity.

- Disadvantages:

- Conflict misses: If multiple memory blocks map to the same cache line, they will overwrite each other. This results in cache misses, even if there is enough space in the cache overall.

2. Fully Associative Cache

In a fully associative cache, any block of memory can be placed in any cache line. There is no restriction on which memory block goes into which line of the cache.

How it works:

- The memory address is divided into two parts: Tag and Block offset.

- Tag: Identifies the block of data being referenced.

- $\circ~$  Block offset: Indicates the location within the block.

- There is no "index" part because any cache line can hold any block of data.

Example:

If you have a cache with 4 lines and memory with 16 blocks, any block of memory can be placed in any of the 4 cache lines.

- Advantages:

- No conflict misses since there are no restrictions on which cache line a block can occupy.

- Better for scenarios where data access patterns are unpredictable.

• Disadvantages:

• Slower lookup: Since any block can be stored in any line, checking if the block is in the cache involves searching all cache lines. This requires more time and complexity, making it slower than direct-mapped caches.

• Higher hardware complexity: Requires extra logic to manage the mapping and searching of cache lines.

3. Set-Associative Cache

A set-associative cache is a compromise between direct-mapped and fully associative caches. In this type of cache, the cache is divided into multiple sets, and each set contains multiple lines. A block of memory can be placed in any line within a set, but it cannot be placed in just any line across the entire cache.

How it works:

- The memory address is divided into three parts: Tag, Set index, and Block offset.

- Tag: Identifies the block of data.

- Set index: Determines which set in the cache the block will go to.

- Block offset: Specifies the location within the block.

- The cache is divided into NNN sets, and each set contains MMM cache lines. A block can be mapped to any line within its assigned set.

Example:

If you have a cache with 4 sets and 2 lines per set, a block of memory will be placed in one of the two lines within the set determined by the set index. If a block from memory maps to a set with available space, it is stored there.

- Advantages:

- Fewer conflict misses than direct-mapped cache because each set contains multiple lines. This allows for some flexibility in where blocks of data can be stored.

- Faster lookups compared to fully associative caches since only a subset of cache lines needs to be searched.

- Disadvantages:

- More complex than direct-mapped cache but less complex than fully associative cache.

- Performance depends on the number of sets and lines in each set. If there are too many sets or too few lines per set, cache performance may degrade.

**Comparison of Mapping Techniques** Mapping Comple Lookup **Conflict Misses** Cache Hardwar Speed **Miss Rate** e Cost Type xity **Direct-Ma** Low High (if Fast High (in Low collisions pped some occur) cases)

| 4       a       Set-Associ Medium Moderat Reduced (less Moderate Medium (balanced) direct-mapped )       (balanced) direct-mapped )         4       a       The Arithmetic Logic Unit (ALU) Operation in a Processor       [10]         4       a       The Arithmetic Logic Unit (ALU) Operation in a Processor       [10]         5       L3         6       Arithmetic Logic Unit (ALU) is a fundamental component of the CPU that performs arithmetic and logical operations. It operates on data that it retrieves from registers or memory and outputs the result back to registers or memory. The operations performed by the ALU include addition, subtraction, multiplication, division (arithmetic operations), as well as logical operations like AND, OR, XOR, NOT, and comparison operations (logical operations).         Basic ALU Operations       1. Arithmetic Operations: <ul> <li>Addition: Adds two numbers.</li> <li>Subtraction: Subtracts one number from another.</li> <li>Multiplication: Multiplication multiplication anumber.</li> <li>Logical Operations:             <ul> <li>AND: Performs a bitwise AND operation between two numbers.</li> <li>OR: Performs a bitwise AND operation between two numbers.</li> <li>Subtraction: Subtracts OR operation inverts each bit).</li> </ul> </li> <li>Shift Operations:         <ul> <li>Shift Performs a bitwise XOR (exclusive OR) operation.</li> <li>NOT: Performs a bitwise XOR operation (inverts each bit).</li> </ul> </li> <li>Shift Right (&gt;&gt;) or Arithmetic Right Shift: Shifts all bits to the right, dividing the value by 2.</li> <li>Shift Right (&gt;&gt;) or Arithmetic Right Shift: Shifts</li></ul> |            | Fully<br>Associativ<br>e                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | High                                                                       | Slow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Low                                                                          | High                                |  |   |    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|-------------------------------------|--|---|----|

| 4 a       The Arithmetic Logic Unit (ALU) is a fundamental component of the CPU that performs arithmetic and logical operations. It operates on data that it retrieves from registers or memory and outputs the result back to registers or memory. The operations performed by the ALU include addition, subtraction, multiplication, division (arithmetic operations), as well as logical operations like AND, OR, XOR, NOT, and comparison operations (logical operations).       [10]         Basic ALU Operations       • Addition: Adds two numbers.       • Subtraction: Subtracts one number from another.       • Multiplication: Multiplies two numbers (in some processors).       • Division: Divides one number by another (in some processors).       • Division: Divides one number by another (in some processors).       • Increment/Decrement: Adds or subtracts 1 from a number.         2. Logical Operations:       • AND: Performs a bitwise OR operation between two numbers.       • NOT: Performs a bitwise VOR (exclusive OR) operation.         • NOT: Performs a bitwise NOT operation (inverts each bit).       3. Shift Operations:       • Shift Left (<:): Shifts all bits to the left, which generally multiplies the value by 2.         • Shift Right (>>) or Arithmetic Right Shift: Shifts all bits to the right, dividing the value by 2.       • Shift Right (>>) or Arithmetic Right Shift: Shifts all bits to the right, dividing the value by 2.                                                                                                                                                                                                             |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Medium                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | than                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                              | Medium                              |  |   |    |

| <ol> <li>Arithmetic Operations:         <ul> <li>Addition: Adds two numbers.</li> <li>Subtraction: Subtracts one number from another.</li> <li>Multiplication: Multiplies two numbers (in some processors).</li> <li>Division: Divides one number by another (in some processors).</li> <li>Increment/Decrement: Adds or subtracts 1 from a number.</li> </ul> </li> <li>Logical Operations:         <ul> <li>AND: Performs a bitwise AND operation between two numbers.</li> <li>OR: Performs a bitwise OR operation between two numbers.</li> <li>XOR: Performs a bitwise XOR (exclusive OR) operation.</li> <li>NOT: Performs a bitwise NOT operation (inverts each bit).</li> </ul> </li> <li>Shift Operations:         <ul> <li>Shift Left (&lt;&lt;): Shifts all bits to the left, which generally multiplies the value by 2.</li> <li>Shift Right (&gt;&gt;) or Arithmetic Right Shift: Shifts all bits to the right, dividing the value by 2.</li> </ul> </li> <li>Comparison Operations:         <ul> <li>Comparison Operations:</li> </ul> </li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <u>4 a</u> | The <b>Arithmet</b><br>performs arith<br>registers or me<br>performed by<br>(arithmetic op                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ic Logic Un<br>metic and lo<br>emory and o<br>the ALU inc<br>erations), as | it (ALU) is a gical operation operation operation of the rest of the rest of the rest of the rest operation operatio | a fundamental componential com | ponent of the C<br>data that it retri<br>s or memory. T<br>iplication, divis | eves from<br>The operations<br>sion |  | 5 | L3 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |            | <ol> <li>Arithmetic Operations:         <ul> <li>Addition: Adds two numbers.</li> <li>Subtraction: Subtracts one number from another.</li> <li>Multiplication: Multiplies two numbers (in some processors).</li> <li>Division: Divides one number by another (in some processors).</li> <li>Increment/Decrement: Adds or subtracts 1 from a number.</li> </ul> </li> <li>Logical Operations:         <ul> <li>AND: Performs a bitwise AND operation between two numbers.</li> <li>OR: Performs a bitwise OR operation between two numbers.</li> <li>XOR: Performs a bitwise XOR (exclusive OR) operation.</li> <li>NOT: Performs a bitwise NOT operation (inverts each bit).</li> </ul> </li> <li>Shift Operations:         <ul> <li>Shift Left (&lt;&lt;): Shifts all bits to the left, which generally multiplies the value by 2.</li> <li>Shift Right (&gt;&gt;) or Arithmetic Right Shift: Shifts all bits to the right, dividing the value by 2.</li> </ul> </li> <li>Comparison Operations:         <ul> <li>Comparison Operations:</li> <li>Shift Shift: Shifts all bits to the right, dividing the value by 2.</li> </ul> </li> </ol> |                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                              |                                     |  |   |    |

The ALU typically consists of:

- **Inputs**: The ALU receives two inputs (A and B), which are usually numbers stored in registers or provided by memory.

- **Control Unit**: The control unit of the CPU sends control signals to the ALU, specifying which operation the ALU should perform.

- ALU Operation Control Lines: The ALU has control lines that select the operation, such as:

- Add, Subtract, AND, OR, etc.

- **Output**: The result of the operation is returned as output (often to a register or memory).

# ALU Example: Addition and Logical AND Operations

Let's consider two 4-bit numbers, A = 1011 (binary) and B = 0110 (binary), and examine the ALU operations that could be performed on them.

```

1. Addition Operation (A + B)

```

In this case, the ALU will perform a binary addition operation on the two numbers **A** and **B**.

A = 1011B = 0110

The ALU performs the following operation (from least significant bit to most significant bit):

sql

Copy code

1011

+ 0110

```

10001 (Result: 10001 in binary, which is 17 in decimal)

```

• The carry bit is 1, so the final result is **10001** (which is 17 in decimal).

# 2. Logical AND Operation (A AND B)

The ALU can also perform logical operations. In this case, we will perform a **bitwise AND** operation on the two numbers **A** and **B**.

A = 1011B = 0110

The bitwise AND operation compares each bit of **A** and **B** and outputs 1 if both bits are 1, otherwise, it outputs 0.

less Copy code A = 1011B = 0110

```

A AND B = 0010 (Result: 0010 in binary, which is 2 in decimal)

```

• The **AND** operation between these two binary numbers results in **0010** (which is 2 in decimal).

# Step-by-Step ALU Operation Example

Let's break down the addition and logical AND operations in detail, assuming that the ALU is controlled by a set of control signals that select the operation (such as addition or AND).

# Step 1: ALU Setup

- The processor has the two input operands, **A** and **B**, ready in the registers (or fetched from memory).

- The **Control Unit** sends control signals to the ALU, telling it which operation to perform (e.g., addition or AND).

# Step 2: ALU Operation – Addition

- For addition, the control signals tell the ALU to use an **add** operation.

- The ALU performs a **binary addition** of **A** and **B**.

First, the bits are aligned:

css

Copy code

A = 1011

```

B = 0110

```

- 0

- Then, each bit is added starting from the least significant bit, handling any carry-over from the previous addition.

- The result is stored in a temporary register and eventually written back to a result register or memory.

# Step 3: ALU Operation – Logical AND

- For the **AND** operation, the control signals instruct the ALU to perform the logical AND operation between **A** and **B**.

- Each bit of **A** is compared with the corresponding bit of **B**, and the result is stored.

• A: 1011

- **B**: 0110

- A AND B: 0010 (binary result)

# Step 4: ALU Output

• After performing the operation (addition or AND), the ALU outputs the result. In the case of addition, it would be **10001**, and for the AND operation, it would be **0010**.