## Internal Assesment Test - I

| Sub:                                                                                                                                                     | Electronic Principles and Circuits                                                                                                                                                                                                            |           |         |               |    |       |      | Code:   |           | BEC303 |    |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|---------|---------------|----|-------|------|---------|-----------|--------|----|--|

| Date:                                                                                                                                                    | 07/11/2024                                                                                                                                                                                                                                    | Duration: | 90 mins | Max<br>Marks: | 50 | Sem:  | 3rd  | Branch: |           | ECE    |    |  |

| Answer Any FIVE FULL Questions                                                                                                                           |                                                                                                                                                                                                                                               |           |         |               |    |       |      |         |           |        |    |  |

|                                                                                                                                                          |                                                                                                                                                                                                                                               |           |         |               |    |       | Mark | S CO    | BE<br>RBT |        |    |  |

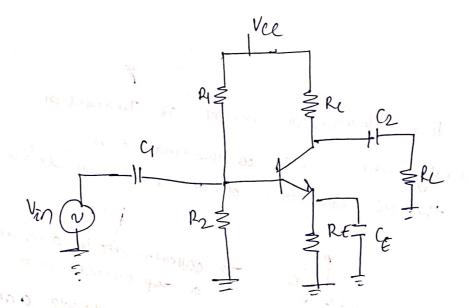

| 1.                                                                                                                                                       | (a) Discuss Two transistor models of Transistor. (b) Explain BJT AC model of Voltage Divider Biased Amplifier.                                                                                                                                |           |         |               |    |       |      |         | [4+6]     | CO1    | L2 |  |

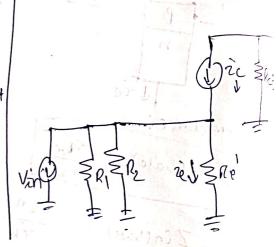

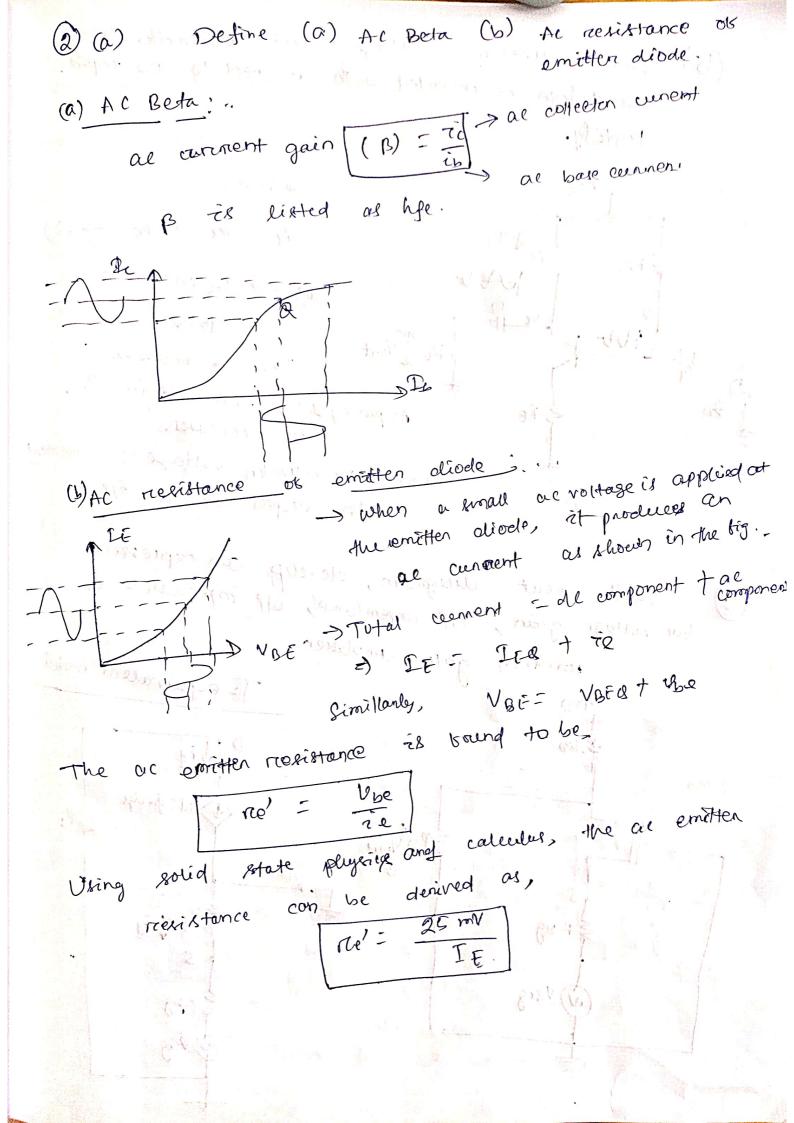

| 1 2                                                                                                                                                      | <ul> <li>(a) Define (i) AC Beta (ii) AC Resistance of the emitter diode.</li> <li>(b) The collector voltage at emitter biased amplifier is inverted with respect to input. Justify the statement with the help of circuit diagram.</li> </ul> |           |         |               |    |       |      |         | [4+6]     | CO1    | L2 |  |

|                                                                                                                                                          | With not singuit diagram dayslan an aymassion for valtage gain input                                                                                                                                                                          |           |         |               |    |       |      | [10]    | CO1       | L2     |    |  |

| a) Explain the working of an inverting op-amp with the help of diagram and derive its voltage gain.  (b) Explain the concept of virtual ground in OPAMP. |                                                                                                                                                                                                                                               |           |         |               |    | [6+4] | СОЗ  | L2      |           |        |    |  |

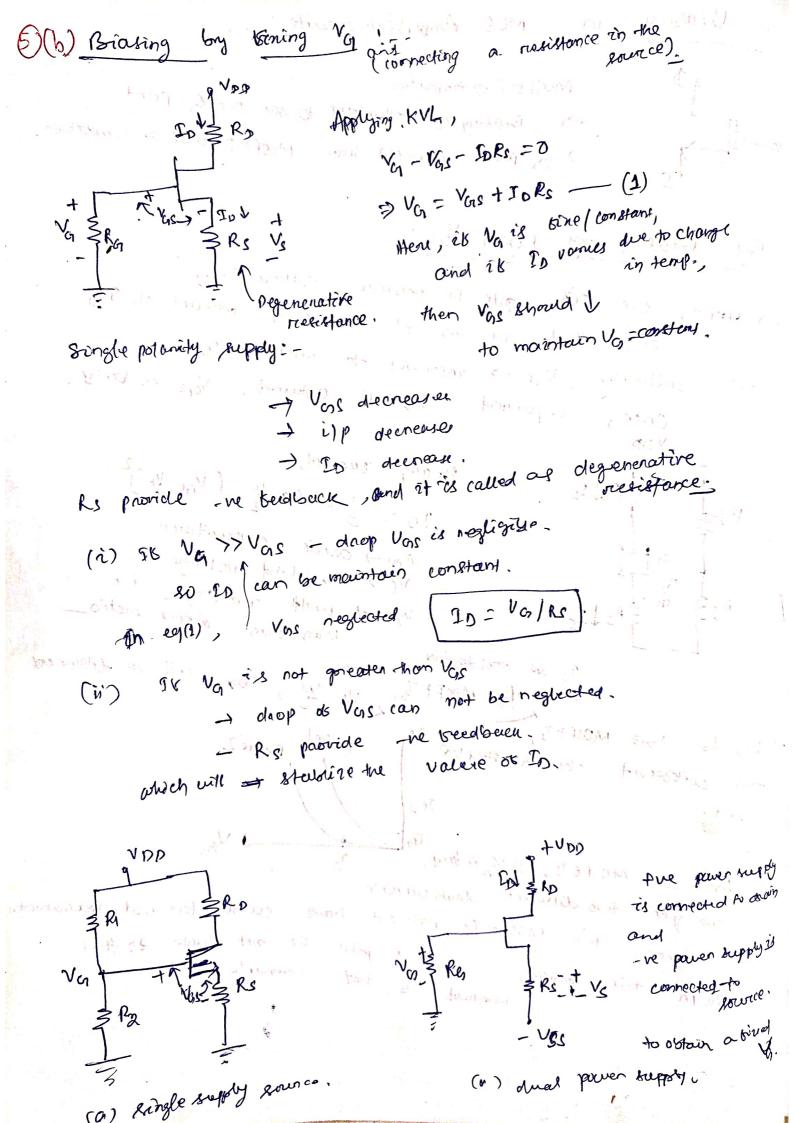

| 5. | <ul><li>(a) With circuit diagram, explain the source follower and derive its voltage gain.</li><li>(b) With neat circuit diagrams, explain biasing of MOSFET by fixing the gate voltage.</li></ul>                                                                                                                                                                                                     | [5+5] | CO2 | L2 |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----|----|

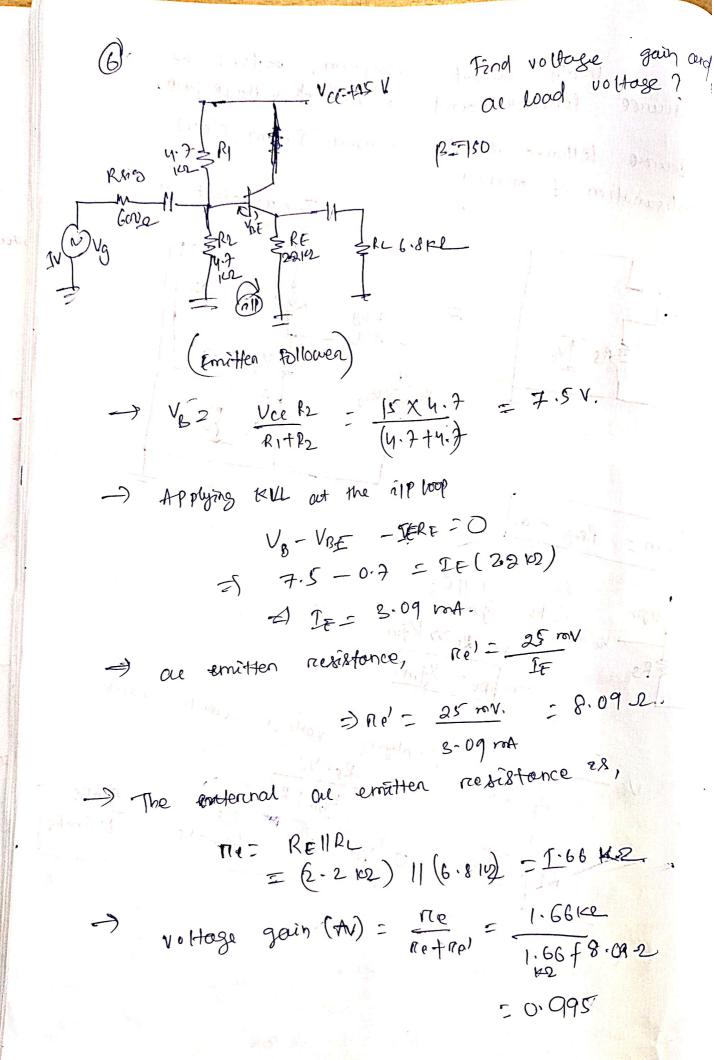

| 6. | For the circuit shown in Fig 1, determine the voltage gain and ac load voltage if $\beta = 150$ .                                                                                                                                                                                                                                                                                                      | [10]  | CO1 | L3 |

| 7. | For an amplifier in fig 2, let $V_{DD} = 5V$ , $R_D = 10K$ , $V_t = 1V$ , $k_n' = 20\mu A/V^2$ , $W/L = 20$ , $V_{GS} = 2V$ , $\lambda = 0$ . (a) Find the dc current $I_D$ and dc voltage $V_{DS}$ (b) Find $g_m$ (c) Find the voltage gain (d) If $v_{gs} = 0.2$ sinot volts find $v_{ds}$ assuming that the small signal approximation holds. What are the minimum and maximum values of $v_{DS}$ . | [10]  | CO2 | L3 |

Sub: EPC

Ampliful Co

som: 3rd (ECE)

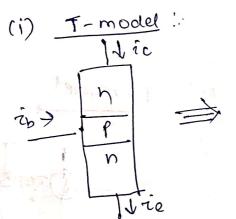

1.(a) Discuss Two transiston model or Transiston.

we need to study the model as the transistin to analyze the ac operation of mansistra amplifier.

ne' \ re!

-> collector déode acts as a dep current source E -) emitter diode octions ac resistance re'.

(Ebers-Moth model)

Input imperdance: Zinchase) = Vose

Zin(lase) =

>Zin(bale) = Bre'

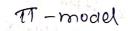

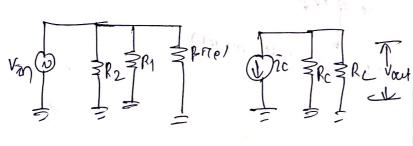

IT - model.

-> cur ilp impendance Brie) vill bood the acrostage source driving the base. Zin = 13172

The voltage goin is given ces

$$AV = \frac{V_{\text{out}}}{V_{\text{on}}}$$

(1)

Total collector resistance

RITRE = ac collector resistance

Puffing this in eq(2)

AV = Re

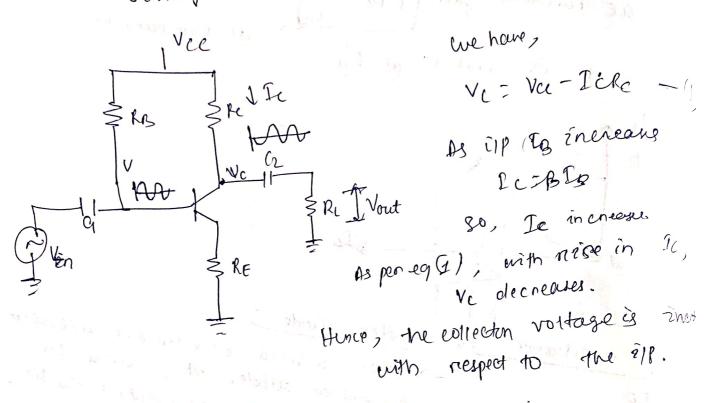

(b) The collector voltage at the emetter bares amplifier is inverted with respect to the input Justify.

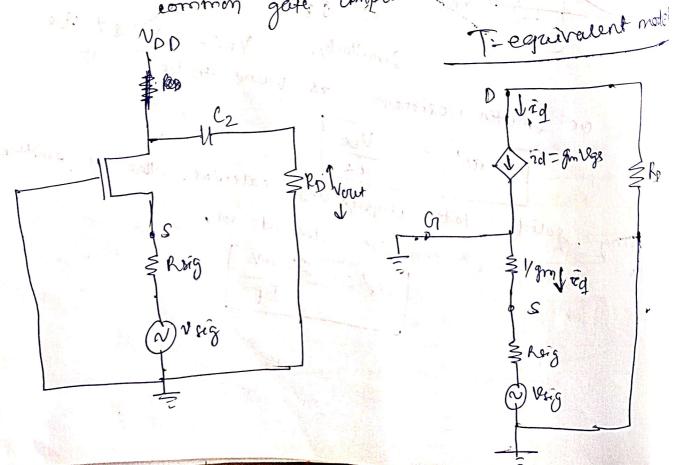

(3) with neat diagnaim, develop an empactaion son voltage gean, ill impendance, of impendance of common gate. amplitiem.

Heme, > Rm = R 1/gm -> Rood = RD -> Von= -id ( Ygm) Vact = -iard AV = gmRD -> Overall voltage gain · CN = (Vgm) · Ar = Av = groke = 1+gmkis = 1+gmkis (a) Berive the voltage gain or Enventing opents. Inventing amplifien gives a phase shift ob 1800 between rip and off signal. I Thin all voltage is connected to the inventing and the non-innerting terminal is garanded. -) As per the virotual ground concept,  $V_A - V_B = 0$   $V_A = 0 V.$ · NP =0 =)

Bring of the desired

Applying KIL at paint A, Q = tint If Iin 20,80 Due to oramp high zonpendance II = If WH Putting VA = 0 V. Explain the concept or virolual governed in (b) opamp. In opamp, the term virtual ground means that voltage at a perticular node is almost equal to the ground voltage (OV.).

The ground voltage (OV.).

As point B is grounded > Vs = 6 V. As in opamp, VA-VB=0 =) VA = VB = OV. Evenils point A is not physically connected ground, bout still voltage at point A (VA) 80, print A is seined to be out Virutual grand

diagram, explain the with circuit source follower and derive its vottage jain. Source follower is the common Drivin (CD) configuration of MOSFET. T-equivalent model Rus Rsig VEG Rin = Reg = 0 : Ro = gro Rs As Rs >> Vgm =) Ro= Ygm roule, vortage - dividen Applying Vo : N: ygpa+ Rs

(in) may

The input impendance of the base is Zin (base) = B(Retre!) = 150 (1.66K2 + 8.09-2) = 250 K2. Zin(stage) = PIIIP2 11 B(Retre!) = (4.7 12) 11 (4.712e) 11 150 (1.66 We +8.09.2) the al ilprobage 2.35 102. Applysing vottage dividen rules. Van = Zen(81 egp) X Vin Ring + Zin(stage)  $= (2.35 \text{ (12)}) \times (1 \text{ V.}) = 0.797 \text{ V.}$ E) Vout = (Av. Van) = (0.995)(0.797) UDD= 5V. RD: 10162 Kn! = 20 MA/V2. ₩ = 20, Ups = 21, 7 =0 (a) Find de evennent ID, de voltage Vas\_ (b) Fird gm (c) Find voltage gain (Ay).

(a) (we have,

$$P_0 = \frac{1}{2} k_0 \frac{W}{L} (V_{05} - V_{4})^2$$

$P_0 = \frac{1}{2} (20) (20) (21)^2$

$P_0 = \frac{1}{2} (20) (20) (20) (20) (20)$

$P_0 = \frac{1}{2} (20) (20) (20) (20) (20)$

$P_0 = \frac{1}{2} (20) (20) (20) (20)$

$P_0 = \frac{1}{2} (20) (20) (20) (20)$

$P_0 = \frac{1}{2} (20)$

$P_$