|                                                                                                                 |    | Module – 1                                                                                                                                                                                                                                                                                                                              | Μ  | L  | С   |

|-----------------------------------------------------------------------------------------------------------------|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|----|-----|

| Q.1                                                                                                             | a. | Derive expressions $V_{in}$ , $V_{out}$ and $A_Y$ for a common emitter circuit with ac equivalent circuit with $\pi$ – model.                                                                                                                                                                                                           | 12 | L1 | CO2 |

|                                                                                                                 | b. | What is the voltage gain and output voltage across the load resistor of $V_{DB}$<br>amplifier?<br>$R_1 = 10 \text{ k}\Omega$ , $R_2 = 2.2 \text{ k}\Omega$ , $R_C = 3.6 \text{ k}\Omega$ , $R_E = 1 \text{ k}\Omega$ , $R_L = 10 \text{ k}\Omega$ ,<br>$V_{CC} = 10 \text{ V}$ , $V_{BE} = 0.7 \text{ V}$ and $V_{in} = 2 \text{ mV}$ . | 8  | L1 | COI |

|                                                                                                                 | -  |                                                                                                                                                                                                                                                                                                                                         |    |    | _   |

|                                                                                                                 |    | OR                                                                                                                                                                                                                                                                                                                                      |    | -  |     |

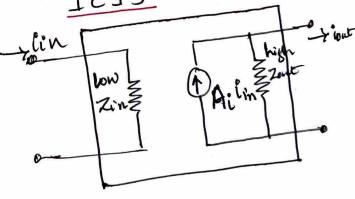

| Q.2                                                                                                             | a. | With a neat diagram, explain loading effect of input impedence.                                                                                                                                                                                                                                                                         | 10 | L1 | C01 |

|                                                                                                                 | b. | <ul> <li>Explain three types of Bias circuit,</li> <li>(i) Emitter feedback bias.</li> <li>(ii) Collector feedback bias and</li> <li>(iii) Collector and emitter feedback.</li> </ul>                                                                                                                                                   | 10 | L1 | CO1 |

|                                                                                                                 |    | Module – 2                                                                                                                                                                                                                                                                                                                              |    |    |     |

| Q.3                                                                                                             | a. | Explain the three biasing methods to bias MOS amplifiers with neat circuit diagram.                                                                                                                                                                                                                                                     | 10 | L2 | CO2 |

|                                                                                                                 | b. | Explain the T-equivalent circuit model of MOSFET.                                                                                                                                                                                                                                                                                       | 10 | L3 | CO2 |

|                                                                                                                 |    | OR                                                                                                                                                                                                                                                                                                                                      |    |    |     |

| Q.4                                                                                                             | a. | With a small signal equivalent model of MOSFET, derive an expression of voltage gain and transconductance.                                                                                                                                                                                                                              | 10 | L2 | CO2 |

|                                                                                                                 | b. | Explain common source follower and derive the expression of voltage gain with necessary equation.                                                                                                                                                                                                                                       | 10 | L2 | CO2 |

|                                                                                                                 |    | Module – 3                                                                                                                                                                                                                                                                                                                              |    |    |     |

| Q.5                                                                                                             | a. | Explain R and 2R resistor Digital to Analog converter and also derive the expression of output voltage.                                                                                                                                                                                                                                 | 10 | L2 | CO3 |

|                                                                                                                 | b. | With a neat circuit diagram, explain the operation of Monostable multivibrator.                                                                                                                                                                                                                                                         | 10 | L2 | CO3 |

| in the second |    | OR                                                                                                                                                                                                                                                                                                                                      |    |    |     |

| Q.6                                                                                                             | a. | With a neat diagram, explain operation of RC-phase shift oscillator using op-amp. Write the expression for frequency of oscillations.                                                                                                                                                                                                   | 8  | L2 | CO3 |

|                                                                                                                 | b. | With a net diagram, explain operation of crystal oscillator using BJT and Write necessary equations.                                                                                                                                                                                                                                    | 6  | L2 | CO3 |

|                                                                                                                 | c. | A crystal has these values $L = 3$ H, $C_S = 0.05$ PF, $R = 2$ k $\Omega$ and $C_m = 10$ PF. What are the series and parallel resonant frequencies of the crystal?                                                                                                                                                                      | 6  | L3 | CO3 |

CF.

## **BEC303**

| Q.7  |          | Module – 4                                                                     |    |          | 1        |

|------|----------|--------------------------------------------------------------------------------|----|----------|----------|

|      | a.       | Explain the first order Low Pass filter with frequency response.               | 10 | L2       | CO       |

|      | b.       | Explain the two types of Band Pass filters.                                    | 10 | L2       | CO       |

|      |          | OR                                                                             |    |          |          |

| Q.8  | a.       | Explain the four types of Negative feedback circuits.                          | 10 | L2<br>L2 | CO<br>CO |

|      | b.       | Explain the working of $2^{nd}$ order high pass filter with a neat circuit and | 10 | . L2     |          |

|      |          | frequency response.                                                            | 1  |          |          |

|      |          | Module – 5                                                                     |    |          |          |

| 0.0  |          | Explain two load lines with necessary circuit diagram and equations.           | 10 | L2       | CC       |

| Q.9  | a.<br>b. | With a neat diagram explain the working of a Thyristor.                        | 10 | L2       | CC       |

|      | υ.       | With a neat diagram, explain the working of a Thyristor.                       | -  |          |          |

|      | -        | OR BANGALORE - 560 037                                                         |    |          |          |

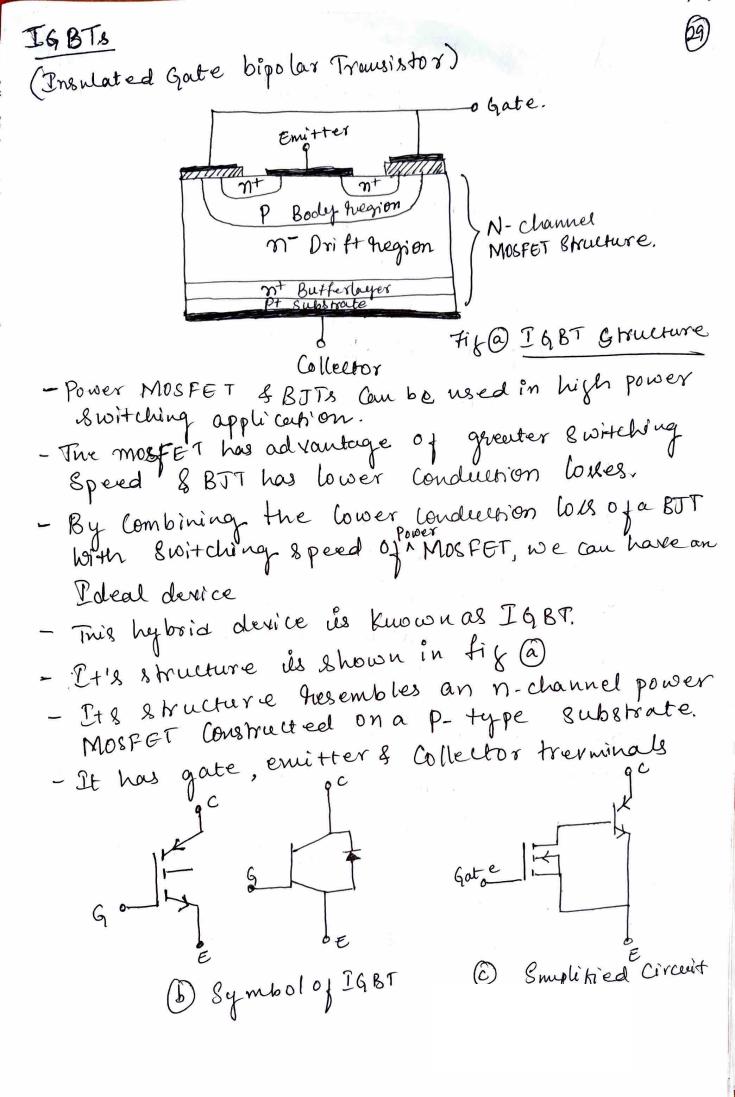

| Q.10 | a.       | Explain Basic Construction and working of IBGTs with necessary figure.         | 10 | L2       | CC       |

| x    | b.       | With a neat diagram, explain the working of UJT relaxation oscillator.         | 10 | L2       | CC       |

|      |          |                                                                                |    |          |          |

|      |          | ****                                                                           |    |          |          |

|      |          |                                                                                |    |          |          |

|      |          |                                                                                |    |          |          |

|      |          |                                                                                |    |          |          |

|      |          |                                                                                |    |          |          |

|      |          |                                                                                |    |          |          |

|      |          |                                                                                |    |          |          |

|      |          |                                                                                |    |          |          |

|      |          | A CY A                                                                         |    |          |          |

|      |          |                                                                                |    |          |          |

|      |          |                                                                                |    |          |          |

|      |          |                                                                                |    |          |          |

|      |          |                                                                                |    |          |          |

|      |          |                                                                                |    |          |          |

|      |          |                                                                                |    |          |          |

|      |          | CR 0:55 CR                                                                     |    |          |          |

|      |          | 30. 8                                                                          |    |          |          |

|      |          | e .3º .8                                                                       |    |          |          |

|      |          | E                                                                              |    |          |          |

|      |          | Et 1.30. Et                                                                    |    |          |          |

|      |          | CR DIB CR                                                                      |    |          |          |

|      |          | R' CR' CR'                                                                     |    |          |          |

|      |          | CR 250 01.30. CR                                                               |    |          |          |

|      |          | CR CR OLD CR CR                                                                |    |          |          |

|      |          | CR CR 01:30. CR                                                                |    |          |          |

|      | ~        | CR CR 2020 01.30 CR CR                                                         |    |          |          |

|      |          | CR CR 01:30 CR CR                                                              |    |          |          |

|      | 5        | CR CR 01.30° CR                                                                |    |          |          |

|      | C?       | CR. CR. 01.30. CR. CR.                                                         |    |          |          |

|      | 5        | CR CR 01.20 CR CR                                                              |    |          |          |

|      | 5        | CR CR 01.20 CR CR                                                              |    |          |          |

|      | 5        | CROMPAD CROCK                                                                  |    |          |          |

|      | 5        | CR CR OLD CR CR                                                                |    |          |          |

|      | S        | CR CR OLD CR CR                                                                |    |          |          |

|      | C>       | CR. CR. OR. CR. CR. CR. CR. CR. CR. CR. CR. CR. C                              |    |          |          |

|      | Cr.      | CR. CR. OR. CR. CR. CR. CR. CR. CR. CR. CR. CR. C                              |    |          |          |

|      | 3        | CR. CR. OR. CR. CR. CR.                                                        |    |          |          |

|      | 0        |                                                                                |    |          |          |

|      | 5        | CR CR CR CR                                                                    |    |          |          |

|      | S        | CR OR OR OR OR                                                                 |    |          |          |

|      | C.       | CR 2 of 2                                                                      |    |          |          |

|      | Cr       | CR 2 of 2                                                                      |    |          |          |

|      | Ch.      | CR. CR. CR. CR.                                                                |    |          |          |

|      | 3        | CR. CR. CR. CR.                                                                |    |          |          |

|      | 3        | CR. CR. CR. CR. CR.                                                            |    |          |          |

|      |          | CR.                                        |    |          |          |

Electronic, Poinciples and Circuits Module-I 1 (a) Derive expressions Vin, Vout and Ay for a common emilter circuit with ac equivalent circuit with II-model. NO NO RELETE ▲ Common Emitter circuit & its AC equivalent circuit Using TI-model. · Using Ohm's law, the 1/P voltage can be expressed Vin = ib Bre • In the collector circuit, the ac D/P voltage: Vout = ic (RC11RL) -> Vout - Bib (RellRi) [: B=ic] · Voltage gain is given by Av = Vout - Bto (RellR1)  $\frac{V_{in}}{A_v = \frac{R_c IIR_l}{r_e'}}$ • Expression for ac collector resistance re= Rc11RL 'Av = rc where re'= 25mV TES

1(b) What is the veltage gain and output voltage across the load netistor of Upp amplifier? -> Given: RI=10KD, R=2.2KD, Rc=3.6KD, RE=1KD, R1= 10 KS2, Vec = 10V, VAE = 0,7V, Vin = 2 mV. W.KT: AV = RellRL [from ac II-model] VCC-10V ASION SR. 3, CKA 9 re= 25mV Vin Rescale Rescience JEQ. · From the circuit. VB = Vac XR2 RI+R2 = 10 × 2.2K 10K+2,2K Since, = 1.80V.VE = IERE IEg= VE RE VBE = VB-VE, = 1.1 M = 1.1 mAVE - VB - VBE = 1.80-0.7 re'= 25mV = 22.727.02 VE = 1.1V 1.1mA '. Av = RellRL = 3.6K1110K - 2.64K re' 22.73 22.73 Av = 116.19 · W.K.T: Av = Vout Vin . Vout = Av. Vin = 116.14×2mV Vout = 0,232 V

2(a) With a neat diagram explain loading effect of input impedance. > De analyze the leading effect of 1/P impedance, we use a source resultor or generator resistor (RG) across the 1/P voltage supply.  $R_{G} = R_{2} = R_{E} = C_{E} + C_{2} = R_{G} = R_{1} = R_{2} = R_{1} = R_{2} = R_{2} = R_{1} = R_{2} = R_{2$ ▲ CE amplifier. ▲ ac equivalent TI-model · Drie to some vellage drop across Rg, the net AC -voltage across the emilter diale will derease. · The 1/P impedance includes the effects of the biasing resisters R1 E1R2, in parallel with the input impedance of base Zin (base). · Input impedance at stage: Zin(stage) = R. 11R211 Bre' · Input impedance at base: Zin (base) = Bre' Winn → Winn von write: Wy ₹ Zm(Mage) Vin - Zin (stage) × Vg RG + Zin (stage) -> With voltage divider theorem,

PAGENO DATE 2(b) is Emitter-Feedback Bias: +Vcc · Basic idea of this Bias circuit WI RC ERB > If Ic moreases, VE increases causing the in VB which leds to less TB which is opposing original increase in Ic. → In this bias Emilter voltage is ted FRE back to the base circuit & it is negative because it opposes the original change in Ic stabilizing 8-point. -> But this bias circuit is not much popular, because &-point variation is still too large -> Equations of Emilter feedback bias: IE - Va- VBE RE + RB/Bdc VE = FERE  $V_{B} = V_{E} + 0.7V$ Ve - Vec - Icke, (ii) Collector Feedback bias: + VCC · Also known as self bias RB ZRC · Suppose, if Ic increases, it deireases Vc -> decreases VB inturn decreasing TB, which again opposes original increase in Ic > Hence, it uses a negative feedback in attempt to reduce original change in collector urrent. , VB= D. 7V, Vc= Vcc-IcRc IE = VCC - VBE RC + RB/BdC

· collector -feedback bias is more effective than emitter-feedback in stabilizing g-point (iii) Collector & Emitta Feedback bias: +Vcc > This feedback bias is more a combination of both Emitter feedback bias cht RC RB m and collector feedback bias asaut. · Analyzing equations are : fe TE = Vcc - VBE RC+RE+RB/BdC VE = JERE VB = VE + 0.7V Ve = Vec - VeRc 3(a) The three biasing mades to bias mos amplifier arei (i) Biaring by fixing Vas: · Most straight toward method to bias a MOSFET. · Initially Vas is varies to get required ID. · Once adequate Ip is obtained, vos is fixed · But, this biasing is not a good approach WikiTi ID= + Mn Cox W (VGS-Vt)2 · Values of pen, cox, w, Vt vary for two differen t mater MOSFET's. Both MD & Vt depend on temp - erative

PAGE NO DATE · tlence, if we fix Vgs, ID becomes very much timperature dependant, due to which variability of ID increases very much Vas Vas in the source. Vpp We can nonte, By KVL, VD = VD - VS. · In eq"D, if Vg is much greater than Vgs, Ip will be mostly determined by values of Vg G Rs. · However, it Va is not much greater than Vas, resistor Rs provides negative feedback which acts to stabilize the values of bias aerrent TD · Eq" () inducates that since va is fixed, vas will have to decrease, but this inturn decreases Ip Dhus the negative feedback action of ks keeps

D as constant as possible,

It reduces the variability Tp, hence stabilizing 3-point

(iii) Drain to gate Feedback Resister: Ra Seo [30 Negative feedback increases bias stability. Ra Seo [30 Nop increases bias stability. Nop increases bias stability. Nop: Nop - Vob + I o Ro + Vos = 0 Vob = Jo Ro + Vos = 0 Vob = Jo Ro + Vos = 0 From circuit, Vg = Vp  $V_{GS} = V_{G} - V_{S} = V_{D} - V_{S} = V_{DS}$ :  $[V_{GS} = V_{DS}]$ Therefore, eq? O can also be written as Nor in saturation, 1 = 1 µp cox w (Vas - Vt)2 - 3 Hence, eq @ can be written as  $T_{p} = \begin{pmatrix} -1 \\ R_{p} \end{pmatrix} V_{qs} + V_{pp} \\ R_{p} \end{pmatrix} V_{pp} \\ R_{p} \end{pmatrix} V_{pp}$ Devia 1 Kegnos Regnos  $y = m \chi + c.$ > If temperature increases, Ja PDL Ip should reduce, which inturn reduces Vas · According to drain chase clinistics, if Ups Ise, To Use, which opposes mitial assumption · seence, here the negative feedback resistor RG comes into action. It maintains To current a constant as much as possible. · fleuce, &-paint will be stable.

3(b) Explain the T-equivalent circuit model of MOSFET. · Figure shows T-equivalent model of MOSFET without internal resistance no. · By including the internal resistance ro, the t-equivalent model can be redrawn as G + Ugs Ts- gm T-equivalent model is preferred when source resistance r<sub>s</sub> is included.

Π-model is preferred if source resistance r<sub>s</sub> is absent. is absent. 4 (a) With a small-signal equivalent model of MOSFET, derive an expression of voltage gain and transconductance.

VDD RD JD ⇒ the did=gmigs = ro · VD O vg T Small signal equivalent model · Total aurrent is represented as: iD = 1 Km W (Vas - VL)<sup>2</sup> = + Km W [ Vas + Vgs + (-Ve)]2 → Total ac component can be obtained by considering only ac components id = 1 Kn W [ Vgs + 2 Vgs Vgs - Vgs Vt] ia = 1 Kn w 2 [ Vas Vas - Vas Vt] id = Km W/ Vqs - Vt] Trans conductance: . Defined as ratio of output to the 1/P gm = <u>DIP current</u> = <u>Id</u> <u>UP voltage</u> <u>Ugs</u> we have: <u>id</u> = Km <u>W</u> [<u>Vgs</u> (<u>Vgs</u>-Vt)] voltage  $\frac{ig}{v_{gs}} = \frac{K_n W \left[ \frac{V_{gs}}{V_{gs}} \left( \frac{V_{qs} - V_{\ell}}{V_{gs}} \right) \right]}{\frac{V_{gs}}{V_{gs}}}$ 9m = KnW (Vas-Vt)

· Voltage gain Av = Vout : id Rp Vas Vgs Vas Av- gmRD 4(b) Explain common source follower and derive the expression of voltage gain with necessary equation -> The common-Drain configuration of MOSFET is known as common source follower. mm 12, 15 Step1: ac equivalent T-model of Common Drain Configeration; > id 80 MM ars=gm Vsig (~ Rs SRL Stepa: Input & Output Resistance Rin = 00 ( due to Gate insulation ) Rout = No II\_I gm

$tep3: A_V = Vout = Rs$   $V_{in} = Rs + 1$  gm. Vout 2 Vin Rs Rs + I gm => Av= gmRs 1+gmRs

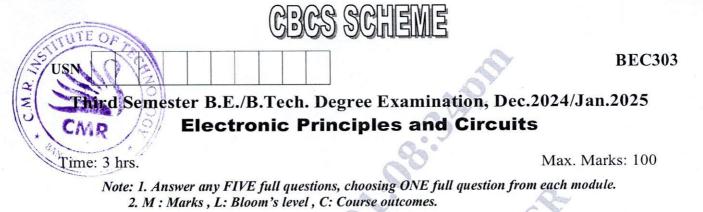

## R/2R ladder D/A converter

#### Fig 18-25

A 4-input D/A converter has 16 possible outputs, an 8-input A/D converter has 256 possible outputs, and a 16-input D/A converter has 65,536 possible outputs. This means that the negative-going staircase voltage of Fig. 18-24b can have 256 steps with an 8-input converter and 65,536 steps with a 16-input converter. A negative-going staircase voltage like this is used in a digital multimeter along with other circuits to measure the voltage numerically. The binary-weighted D/A converter can be used in applications where the number of inputs is limited and where high precision is not required. When a higher number of inputs is used, a higher number of different resistor values is required. The accuracy and stability of the D/A converter depends on the absolute accuracy of the resistors and their ability to track each other with temperature variations. Because the input resistors all have different values, identical tracking characteristics are difficult to obtain. Loading problems can also exist with this type of D/A converter because each input has a different input impedance value. The R/2R ladder D/A converter, shown in Fig. 18-25, overcomes the limitations of the binary-weighted D/A converter and is the method most often used in integrated-circuit D/A converters. Because only two resistor values are required, this method lends itself to ICs with 8-bit or higher binary inputs and provides a higher degree of accuracy. For simplicity, Fig. 18-25 is shown as a 4-bit D/A converter. The switches D0 - D3 would normally be some type of active switch. The switches connect the four inputs to either ground (logic 0) or 1Vref (logic 1). The ladder network converts the possible binary input values from 0000 through 1111 to one of 16 unique output voltage levels. In the D/A converter shown in Fig. 18-25, D0 is considered to be the least significant input bit (LSB), while D3 is the most significant bit (MSB). To determine the D/A converter's output voltage, you must first change the binary input value to its decimal-equivalent value BIN.

$BIN = (D_0 \times 2^0) + (D_1 \times 2^1) + (D_2 \times 2^2) + (D_3 \times 2^3)$

Then, the output voltage will be found by:

$$V_{\text{out}} = -\left(\frac{\text{BIN}}{2^N} \times 2V_{\text{ref}}\right)$$

where N equals the number of inputs.

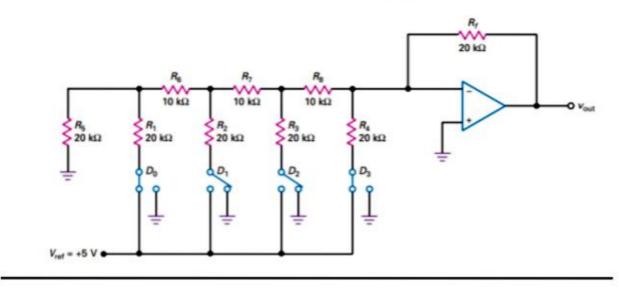

Monostable Multivibrator

#### Operation

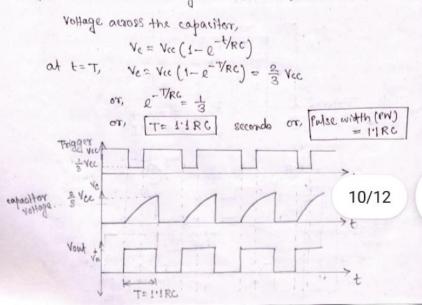

In standby mode, FF holds transistor  $Q_1$  on, thus clamping the external timing expected C to ground. The FF is in reset condition.  $\therefore Q = 1$ , of p = LOW.

As the trigger passes through  $\frac{V(c)}{3}$ , the FF is set i.e e=0, This makes Q<sub>1</sub> off and the short circuit across the timing capacitor is released. But Q is LOW, output goes HIGH (=vec). The timing eycle now begins. since C is unclamped, voltage across it raises exponentially through R two towards vec with a time constant Rc.

If the voltage across the capacitor is just greater them  $\frac{2}{3}$  vice and the upper comparator resets the FF i.e R=1,S=0. This makes  $\overline{Q}=1$ , transistor  $Q_1$  goes on (i.e saturates), the output returns to standby state (i.e Low).

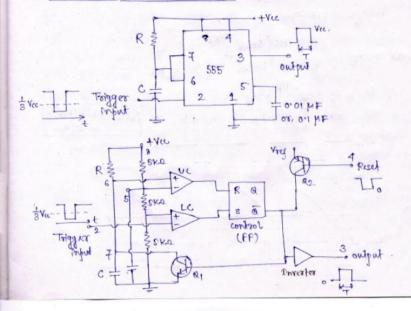

Phase shift Oscillator:  $-\frac{R}{C} + \frac{R}{C} + \frac{R$ R R R R R VO -VEE phase shift oscillator with a) Phase shift oscillator with (b) phase shift oscillator with 3 lead circuit

Jead circuit

fr= 1/2TNRc

B>1/2

Av = 29

Av = 29

Av = 20 Cercuet in feedback path. - lead circuit produce a phase shift of 0°t090° - each lead circuit produce a phase shift of 60°, at some fray, - The total phase shift of three lead Circuit is 130° - The amplifier has a phase shift of 180° - As a result the overall phase shift is 360° @ 0° - When AVBYI, then the Oscillations start - Fig B shows the phase shift Oscillator with there dag Circuit - The operation is simillar to figue - Long Circuit produces - 180° phase shift at some - The amplifier produces a phase shift of 180° - As a gresult overall phase shift is 0°. - If ANBYI, then the Oscillations start. - This oscillator is not popular circuit - Problem is that it can not easily adjust to large for hange

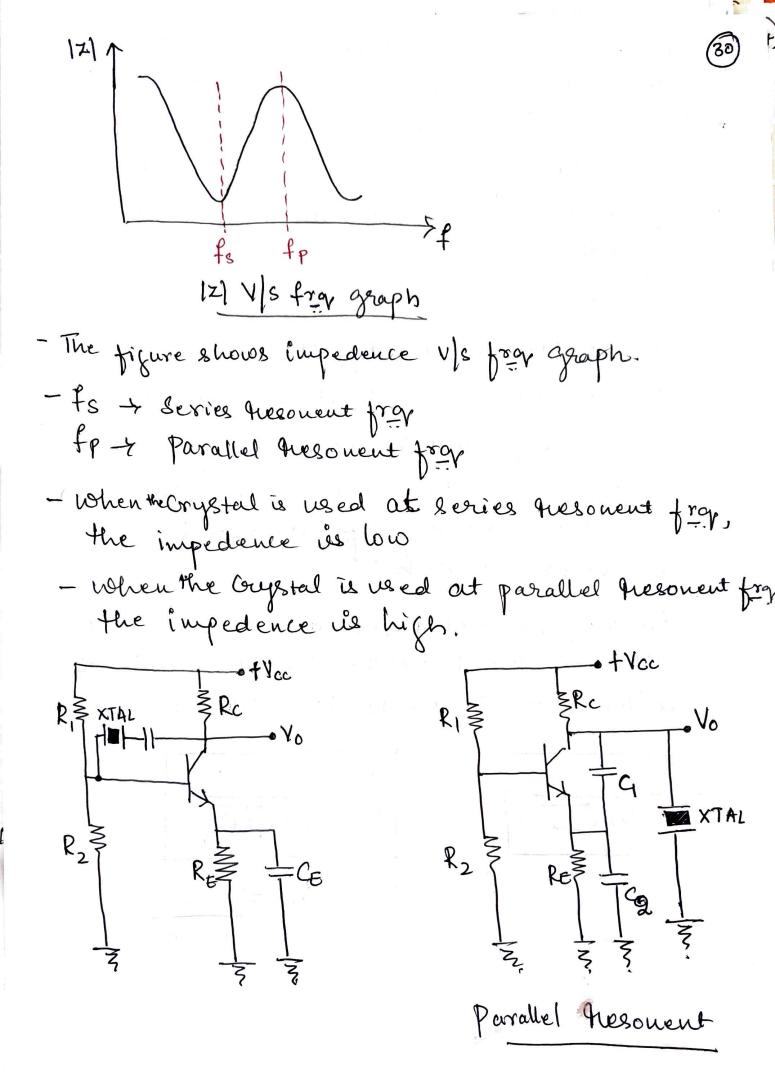

| Crystal Oscillator:                                                                                                                               |

|---------------------------------------------------------------------------------------------------------------------------------------------------|

| - These oscillators are used in Radio & Tele communications                                                                                       |

| - They are used in many digital Circuits                                                                                                          |

| - They are essential part of Milro Controllogs to acupsate                                                                                        |

| - They are essential part of Milro Controlleurs to generate<br>the Clock Signals.                                                                 |

| - It Can generate Stable fraguencées from 100 KHz                                                                                                 |

| TO (00'MH22.                                                                                                                                      |

| - It works on the principle of Turning Di                                                                                                         |

| - It works on the principle of Inverse-Piezo<br>electric effect.                                                                                  |

| V V HVV                                                                                                                                           |

| 1 11/41 -                                                                                                                                         |

| Inverse prezoelectric Piezo electric effect.                                                                                                      |

| effect.                                                                                                                                           |

| Diar a lectric material is                                                                                                                        |

| - when & Good the pieto cue they generate the                                                                                                     |

| mechanically Vibrales, terminals This is known                                                                                                    |

| - when # End the Piezo electric material is<br>mechanically Vibrated, then they generate the<br>Noltage accross the two terminals, This is, Enown |

| as. Piezo electric effect.<br>Biezo electric effect is reverse operat                                                                             |

| - In verse piezo electric effect is reverse operat                                                                                                |

- In verse piezo electric effect us neverse operat of Piezo electric effect. - If Certain amount of Voltage is applied to Piezo electric material, Itwill also Vibrate Piezo electric material, Itwill also Vibrate

- Hence fx\_1 Thick news of Crystal. - Commonly used Crystal is grantz Crystal to produce Sinusoidal Oscillations, because (DIt is mechanically strong (i) good piezo electric Leusitivity (iii) less expensive  $rac{1}{r}$   $rac{$ Symbol electrical equivalent Cercuit. The above figure shows the Symbol of the Orystal and its electrical equivalent Circuit. R -> electrical equèvalent Tresistance of Crystal L > electrical equivalent Inductance of crystal Mars - here C -> electrical equivalent. Cours tal Capacitance Cm + Capacitance due to mechanical mounting of Crystal. - Carye tal have two resonant prequencies. (i) Series presonent frag (ii) parallel presonent frag

- -In both Series & parall el Résonant Circuit, Common emitter Voltage divider cis used as an amplifier

- In Series resonant, the Crystal is Converted as a series element in the feedback

- And in parallel fresoment, the Caystal is connected in parallel.

- Both the Circuit will operate on the principle of Universe Prezoeleuric effect.

- when Voltage is applied the erystal will Vibrate and produce of P

- Vibrate and produce some frequency. - In the series resonant, the impedence is low of the amount of feed back to the Amplifier is high.

- In the parallel fuesonew, the Orystal ies acting as an inductor, hence the Circuit Will & work as a Colpitts Oscillator

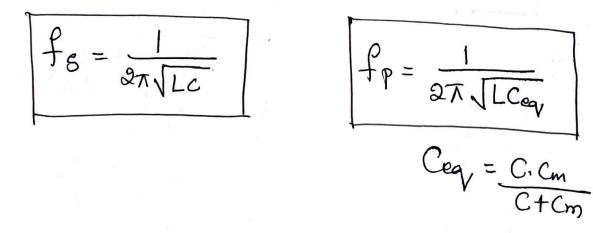

Calculate Series Resonant Frequency ( $f_s$ )

$$f_s = rac{1}{2\pi \sqrt{L \cdot C_s}}$$

Substitute the given values:

$$egin{aligned} f_s &= rac{1}{2\pi \sqrt{(3)(0.05 imes 10^{-12})}} \ f_s &= rac{1}{2\pi \sqrt{1.5 imes 10^{-13}}} \ f_s &= rac{1}{2\pi (1.2247 imes 10^{-7})} \ f_s &= rac{1}{7.698 imes 10^{-7}} \ f_s &pprox 1.298 \,\mathrm{MHz} \end{aligned}$$

# Calculate $C_m^\prime$ (Effective Capacitance)

$$C'_m = \frac{C_s \cdot C_m}{C_s + C_m}$$

Substitute the given values:

$$C_m' = rac{(0.05 imes 10^{-12}) \cdot (10 imes 10^{-12})}{0.05 imes 10^{-12} + 10 imes 10^{-12}} \ C_m' = rac{0.5 imes 10^{-24}}{10.05 imes 10^{-12}} \ C_m' pprox 0.04975 \, \mathrm{pF} = 0.04975 imes 10^{-12} \, \mathrm{F}$$

Calculate Parallel Resonant Frequency  $(f_p)$

$$f_p = rac{1}{2\pi \sqrt{L \cdot C_m'}}$$

Substitute the values:

$$egin{aligned} f_p &= rac{1}{2\pi \sqrt{(3)(0.04975 imes 10^{-12})}} \ f_p &= rac{1}{2\pi \sqrt{1.4925 imes 10^{-13}}} \ f_p &= rac{1}{2\pi (1.2217 imes 10^{-7})} \ f_p &= rac{1}{7.673 imes 10^{-7}} \ f_p &pprox 1.303 \,\mathrm{MHz} \end{aligned}$$

6c)

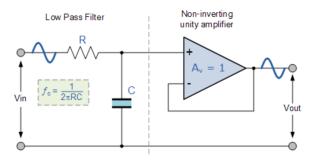

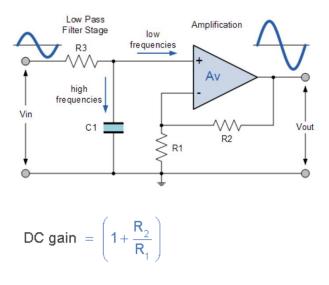

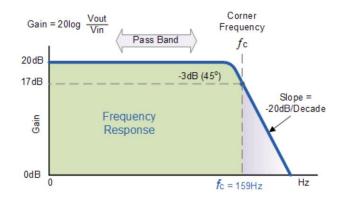

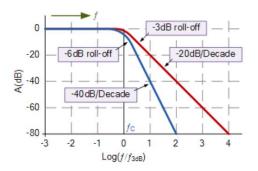

## **First-Order Low-Pass Filter**

A **first-order low-pass filter** is a basic electrical circuit that allows low-frequency signals to pass through while attenuating high-frequency signals. It is called "first-order" because its output depends linearly on the input frequency (i.e., the roll-off rate is 20 dB/ decade).

First Order Low Pass Filter

This first-order low pass active filter, consists simply of a passive RC filter stage providing a low frequency path to the input of a non-inverting operational amplifier. The amplifier is configured as a voltage-follower (Buffer) giving it a DC gain of one, Av = +1 or unity gain as opposed to the previous passive RC filter which has a DC gain of less than unity.

The advantage of this configuration is that the op-amps high input impedance prevents excessive loading on the filters output while its low output impedance prevents the filters cut-off frequency point from being affected by changes in the impedance of the load.

While this configuration provides good stability to the filter, its main disadvantage is that it has no voltage gain above one. However, although the voltage gain is unity the power gain is very high as its output impedance is much lower than its input impedance. If a voltage gain greater than one is required we can use the following filter circuit.

Active Low Pass Filter with Amplification

#### Gain of a first-order low pass filter

$$Voltage \ Gain, (Av) = \frac{Vout}{Vin} = \frac{A_F}{\sqrt{1 + \left(\frac{f}{fc}\right)^2}}$$

Where:

$A_F$  = the pass band gain of the filter, (1 + R2/R1)

*f* = the frequency of the input signal in Hertz, (Hz)

*f*c = the cut-off frequency in Hertz, (Hz)

## Frequency Response Curve

Multiple Feedback (MFB) Band pars Filters:

- Bandpars Filter has Center fry and Band width

$$3W = f_2 - f_1$$

$$f_0 = \sqrt{f_1 f_2}$$

$$Q = \frac{f_0}{BW}$$

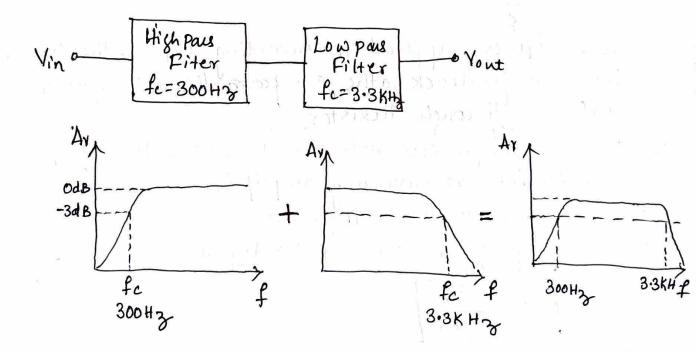

-Nohen Q<1 then Filter has wide band thesponse and when Q>1 the Fiter has narrow thesponse. - The bandpark Filter are designed by cascading a LPF stage & a HPF stage\*(for Q<1)\* Wideband Fiters:-

- If we Want to build a Bound pail Filter with lower Cut off Frag 300 Hz & upper Cut off  $\int \frac{1}{2} \frac{1}{9} \frac{1}{9}$

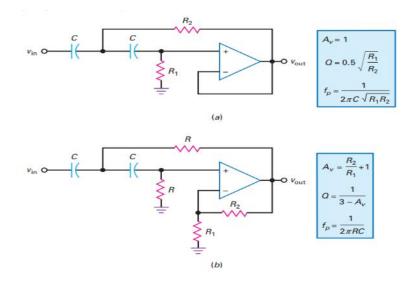

-The HPF has fc= 300Hz & LPF has fc=3.3kHz. - When two decibles thesponse are added we will get A ROM a BPF mesponse with cut off frquencies of 300 Hz & 3.3KHz - When Q<1 we will use Cascade approach. Narrow band Filters -When QYI, We can use multiple Feedback (MFB) Fitter as shown in fif. below Vin Milt - Here i | P is applied to inverting i | P & the circuit has two feedback patt -ne press. through Capacitor & another through fres s For the Afrequencies between low fry & High fry the Circuit acts as inverting amplifier. - For other frquencies 0/plus Kero. - The Voltage gain at the Center frag is  $A_V = \frac{-R_2}{2R_1}$ - The Q of the Circuit is  $Q = 0.5 \frac{R_2}{R_1} \quad \text{ or } \quad Q = 0.707 \sqrt{-Av}$ - The center  $\frac{1}{2\pi}r_{0}r_{1}$  is  $f_{0} = \frac{1}{2\pi\sqrt{R_{1}R_{2}C_{1}C_{2}}}$  $C_1 = C_2 \qquad f_0 = \frac{1}{2\pi c \cdot \sqrt{R_1 R_2}}$

10)

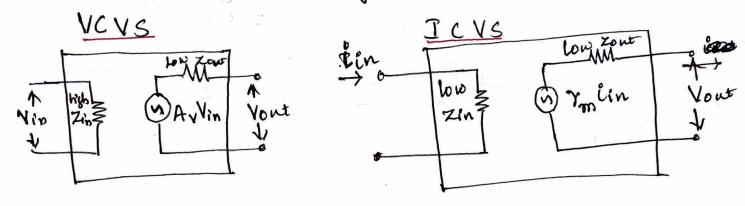

|       | v   | V       |          |      |          |          |              |                   |

|-------|-----|---------|----------|------|----------|----------|--------------|-------------------|

| Input | 019 | Circuit | Zin      | Zont | Converts | Partio S | ymbol        | Type of amplifier |

| V     | ٧   | VCVS    | $\infty$ | 0    | -        | Nouthin  | Aγ           | Voltage Amplipier |

|       |     | ICVS    |          |      | itoV     | Vout/in  | $\gamma_{m}$ | Trans reststance  |

| V     | Ĩ   | VCIS    | 60       | 00   | Vtoi     | Vin Vin  | Jon          | Trans Conductance |

| I     | Ĩ   | ICIS    | 0        | 100  | -        | lout/lin | Αĉ           | Current Amplifier |

|       |     |         |          | 1    |          |          |              |                   |

- I P to negative feedback Combe eithera Voltage (3) a Current

- 0 | p signal Cambe either a voltage (3) a Current.

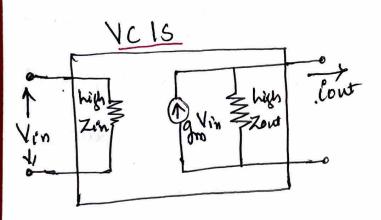

- There are 4 types of negative feedback.

2n

- NVC NS (Voltage Combrolled Voltage Source), i | p is Voltage & o | p is also Voltage , it has Stabilized gain, infinate i | p impedence & Zero o | p impedence it & known as voltage Amplipier.

- In ICNS (Current Controlled Voltage Source), i / p is

Current & Opries Voltagre, here "ilp impedences Oprimpedence ils Xero, it is known as Frans thesistance Amplitier

- In NCIS (Voltage controlled Current Source), the ip 2 is Voltage 3 ofpris current, here ils impedence 3 Opprimpedence areinginate, it is known as Transconductare Amplifier.

- In ICIS (Current Controlled Current Source), the ip is current & Olp is also current, here ip imper dence is 'd' and ofp impedence is 'os'. It is known as augrent Amplipier.

- E CNS Converts Current to Voltage and VCI's Converts Voltage to avoient.

ILIS

## Second-Order High-Pass Filter

A **second-order high-pass filter** allows high-frequency signals to pass while attenuating low-frequency signals. Being "second-order" means it has a roll-off rate of 40 dB/decade) in the stopband, which is steeper than a first-order filter.

## **Circuit Diagram**

A second-order high-pass filter can be implemented using two reactive components (capacitors) and two resistors. The most common configuration uses an **active filter design** with an operational amplifier (op-amp) to improve performance.

Frequency Response

Most designs of second order filters are generally named after their inventor with the most common filter types being: *Butterworth*, *Chebyshev*, *Bessel* and *Sallen-Key*. The Sallen-Key filter design is one of the most widely known and popular 2nd order filter designs, requiring only a single operational amplifier for the gain control and four passive RC components to accomplish the tuning.

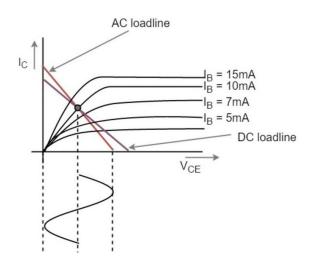

#### Load Line Analysis

Load line analysis is a graphical method used in electronics to study the interaction between a circuit (typically involving a transistor or diode) and its connected load. The load line represents all possible operating points of the circuit under given conditions. There are two types of load lines:

- 1. DC Load Line: Represents the constraints imposed by the power supply and resistive load.

- AC Load Line: Represents the constraints during small-signal operation, considering the impedance of the circuit.

#### 1. DC Load Line

The **DC load line** shows the relationship between the output current and voltage of a device, based on the external DC circuit connected to it.

#### Derivation:

Using Kirchhoff's Voltage Law (KVL), consider a simple circuit with a transistor (or diode), a supply voltage ( $V_{CC}$ ), and a load resistor ( $R_L$ ):

$$V_{CC} = I_C R_L + V_{CE}$$

Where:

- V<sub>CC</sub>: Supply voltage

- $I_C$ : Collector current

- V<sub>CE</sub>: Voltage across the transistor

- R<sub>L</sub>: Load resistance

Rearranging for

$$I_C$$

:

$$I_C = rac{V_{CC} - V_{CE}}{R_L}$$

#### Equation of the DC Load Line:

$$V_{CE} + I_C R_L = V_{CC}$$

This equation represents a straight line on the  $I_C\text{-}V_{CE}$  plane.

- Intercepts:

- When  $I_C=0$ :  $V_{CE}=V_{CC}$  (x-axis intercept).

- When  $V_{CE}=0$ :  $I_C=rac{V_{CC}}{R_L}$  (y-axis intercept).

#### Significance:

The DC load line provides all possible operating points for the device under steady-state conditions.

#### 2. AC Load Line

The AC load line is used to analyze small-signal behavior. It considers the dynamic impedance  $(r_L)$  of the circuit during signal operation.

#### Derivation:

In small-signal analysis, the impedance  $r_L$  replaces  $R_L$ , and the voltage-current relationship during AC operation is given by:

$$v_{ce} + i_c r_L = V_{CE(Q)}$$

Where:

- $v_{ce}$ : AC voltage across the transistor

- *i<sub>c</sub>*: Small-signal current

- $V_{CE(Q)}$ : Quiescent point (Q-point) voltage

#### AC Load Line Equation:

$$v_{ce} = V_{CE(Q)} - i_c r_L$$

This line has a slope of  $-1/r_L$  and passes through the Q-point. It is steeper than the DC load line if  $r_L < R_L.$

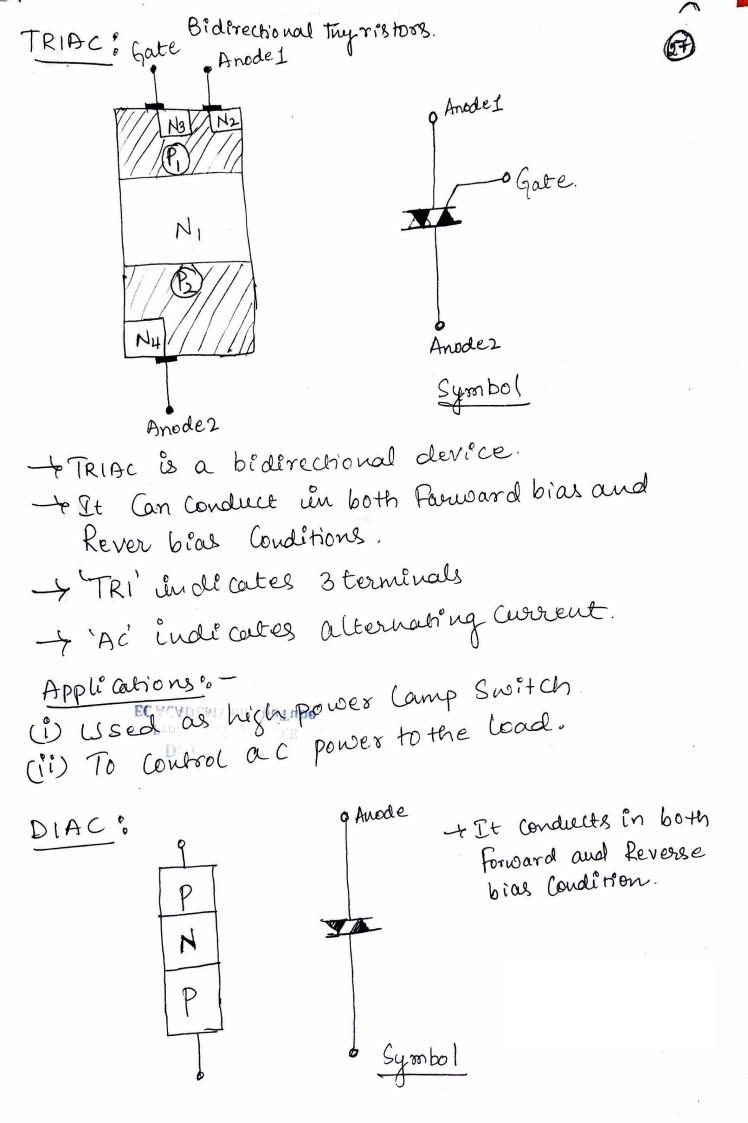

- te Two terminal device with three Semiconducting layers. - \* "D1' indicates two terminals. - > AC indicates Alternahing current. Application:-(i) It can be used as lamp dimmer.

- Two Versionsons device are reflered as punch (30) Through (PT) & non punch Through (NPT) IGBTS - Que punch through (PT) IGBT has our nt buffer clayer b/w pt&n-region. - NPT IGBT has int buffer layer. - fig @ shows an equivelent Circuit of IGBT. - Enput control is V+g b/w Gate & Emitter f Output is Current . b/w Collector & Emitter. other Thyristors (i) pho to - scR open 3 - Et is also Known as light activated g+Vcc - The arrow hepresents incoming light that passes through a windo is thits the depleation larger SCR. then the valance electrons. dislodge from their location & become free - free electrons the Starts positive feedbuck and SCR Closes. has - After light trigger "Closed, the SCR still fremain closed. - For maximum Sensitivity to light, Gate is uleft - open.

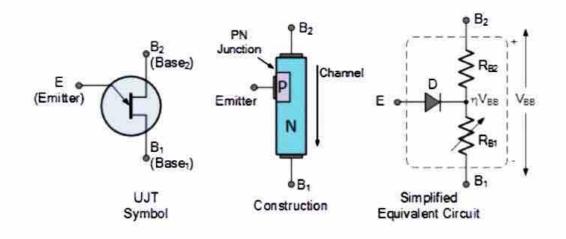

# **Unijunction Transistor**

The UJT is a three-terminal, semiconductor device which exhibits negative resistance and switching characteristics for use as a relaxation oscillator in phase control applications

The **Unijunction Transistor** or **UJT** for short, is another solid state three terminal device that can be used in gate pulse, timing circuits and trigger generator applications to switch and control either thyristors and triac's for AC power control type applications.

Like diodes, unijunction transistors are constructed from separate P-type and N-type semiconductor materials forming a single (hence its name Uni-Junction) PN-junction within the main conducting N-type channel of the device.

Although the Unijunction Transistor has the name of a transistor, its switching characteristics are very different from those of a conventional bipolar or field effect transistor as it can not be used to amplify a signal but instead is used as a ON-OFF switching transistor. UJT's have unidirectional conductivity and negative impedance characteristics acting more like a variable voltage divider during breakdown.

Like N-channel FET's, the UJT consists of a single solid piece of N-type semiconductor material forming the main current carrying channel with its two outer connections marked as *Base 2* ( $B_2$ ) and *Base 1* ( $B_1$ ). The third connection, confusingly marked as the *Emitter* (E) is located along the channel. The emitter terminal is

represented by an arrow pointing from the P-type emitter to the N-type base.

The Emitter rectifying p-n junction of the unijunction transistor is formed by fusing the P-type material into the N-type silicon channel. However, P-channel UJT's with an N-type Emitter terminal are also available but these are little used.

The Emitter junction is positioned along the channel so that it is closer to terminal  $B_2$  than  $B_1$ . An arrow is used in the UJT symbol which points towards the base indicating that the Emitter terminal is positive and the silicon bar is negative material. Below shows the symbol, construction, and equivalent circuit of the UJT.

## 3.7 THE PROGRAMMABLE UNIJUNCTION TRANSISTOR (PUT)

The PUT is an improved version of a UJT. Actually, the PUT is a *PNPN* device, but its operation is so similar to the UJT that it is always considered with the UJT. As we shall see, the PUT behave like a UJT whose trigger voltage  $V_p$  can be set by the circuit designer via an external voltage divider.

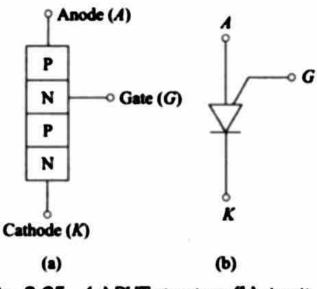

Figure 3.25 shows the *PNPN* structure and the circuit symbol for the PUT. The anode (A) and cathode (K) are the same as for any *PNPN* device. The gate (G) is connected to the *N*-region next to the anode. Thus, the anode and gate constitute a *P-N* junction. It is this *P-N* junction which controls the "on" and "off" states of the PUT. The gate is usually positively biased relative to the cathode by a certain amount,  $V_g$ . When the anode voltage is less than  $V_g$ , the anode-gate junction is reverse-biased and the *PNPN* device is in the "off" state, acting as an open-switch between anode and cathode. When the anode voltage exceeds  $V_g$  by about 0.5 V, the anode gate junction conducts, causing the *PNPN* device to turn "on" in the same manner as does forward biasing the gate cathode junction of an SCR. In the "on" state, the PUT acts like any *PNPN* device between anode and cathode (low resistance and  $V_{AK} \approx 1V$ ). The PUT is also referred to as a complementary SCR (CSCR).

The normal bias arrangement for the PUT is shown in Fig. 3.26. The voltage divider,  $R_1$  and  $R_2$  sets the voltage at the gate  $V_g$ . Note that  $R_1$ and  $R_2$  are external to the device and can therefore be chosen to produce any desired value of  $V_g$ . The anode cathode bias is provided by  $E_{dc}$ . As long as  $E_{dc} < V_g$ , the device is "off" with  $I_A = 0$  and all of  $E_{dc}$  present across the anode cathode ( $V_{AK} = E_{dc}$ ). The "off" state is summarized in part (a) of the figure.

Fig. 3.25 (a) PUT structure (b) circuit symbol

If  $E_{dc}$  is increased to about 0.5V greater than the  $V_g$  bias value, the device turns "on". In other words, the peak-point voltage  $V_p$  for the PUT is given by

$$V_p = V_q = 0.5 \text{ V}$$

(3.19)

In the "on" state, the anode-cathode voltage,  $V_{AK}$ , drops to = 1V and the anode current,  $I_A$ , is essentially equal to  $E_{dc}/R_1$  being limited by R. In addition,  $V_g$  drops to a very low value (= 0.5 V) since  $R_2$  is now shunted by the "on" *PNPN* structure. The PUT will remains in the "on"-state until the anode current is decreased below the valley-current,  $I_P$ . The "on" state is summarized in part (b) of the figure.