# **Solutions to IAT1 ESD**

|     |  |  |  |  |  | -10 1954 |

|-----|--|--|--|--|--|----------|

| USN |  |  |  |  |  |          |

|     |  |  |  |  |  | * ONLINE |

CMR INSTITUTE OF TECHNOLOGY

### Internal Assessment Test - I

| Sub | b: Embedded System Design Code                                                     |                         |              |            |                |          | le: BEC60 |        | 01   |         |     |     |

|-----|------------------------------------------------------------------------------------|-------------------------|--------------|------------|----------------|----------|-----------|--------|------|---------|-----|-----|

| Da  | ite:                                                                               | 24/03/2025              | Duration:    | 90 mins    | Max Marks:     | 50       | Sem:      | 6th    | Brai | nch:    | ECE |     |

|     | Answer Any FIVE FULL Questions                                                     |                         |              |            |                |          |           |        |      |         |     |     |

|     |                                                                                    |                         |              |            |                |          |           | Marks  | OE   | BE      |     |     |

|     |                                                                                    |                         |              |            |                |          |           |        |      | IVIGIES | CO  | RBT |

| 1.  | 1. What are embedded systems? List out the major applications of embedded systems. |                         |              |            |                |          | [10]      | CO1    | L1   |         |     |     |

| 2.  | Ех                                                                                 | xplain with the help    | of neat diag | ram static | RAM and dy     | namic R  | AM op     | eratio | n.   | [10]    | CO1 | L2  |

| 3.  | Di                                                                                 | ifferentiate the follow | wing:        |            |                |          |           |        |      | [10]    | CO1 | L2  |

|     | a.                                                                                 | Von-Neumann             | architecture | and Harv   | ard architectu | re       |           |        |      |         |     |     |

|     | b. Big-endian and Little endian processors                                         |                         |              |            |                |          |           |        |      |         |     |     |

| 4.  | Ex                                                                                 | plain the following     | on-board coi | nmunicat   | ion interfaces | with the | help o    | f a ne | at   | [10]    | CO1 | L2  |

|     | diaş                                                                               | gram: a. UART b. 1      | -wire        |            |                |          |           |        |      |         |     |     |

| 5.  | Wi                                                                                 | th the help of a neat   | diagram, ex  | plain the  | ARM bus tecl   | nnology  | used in   | embe   | dded | [10]    | CO4 | L2  |

|     | syst                                                                               | tems.                   |              |            |                |          |           |        |      |         |     |     |

| 6.  | With the help of a neat diagram, explain the ARM core data flow model.             |                         |              |            |                |          |           | [10]   | CO4  | L2      |     |     |

| 7.  | Discuss various processor modes of ARM core.                                       |                         |              |            |                |          |           | [10]   | CO4  | L2      |     |     |

1.

## 1.1 WHAT IS AN EMBEDDED SYSTEM?

LO 1 Know what an embedded system is An embedded system is an electronic/electro-mechanical system designed to perform a specific function and is a combination of both hardware and firmware (software).

Every embedded system is unique, and the hardware as well as the firmware is highly specialised to the application domain. Embedded systems are becoming an

inevitable part of any product or equipment in all fields including household appliances, telecommunications, medical equipment, industrial control, consumer products, etc.

## 1.5 MAJOR APPLICATION AREAS OF EMBEDDED SYSTEMS

LO 5 Explain the domains and areas of applications of embedded systems We are living in a world where embedded systems play a vital role in our dayto-day life, starting from home to the computer industry, where most of the people find their job for a livelihood. Embedded technology has acquired a new dimension from its first generation model, the Apollo guidance computer, to the latest radio navigation system combined with in-car entertainment technology and the wearable computing devices (Apple watch, Microsoft Band, Fitbit fitness

trackers etc.). The application areas and the products in the embedded domain are countless. A few of the important domains and products are listed below:

- (1) Consumer electronics: Camcorders, cameras, etc.

- (2) Household appliances: Television, DVD players, washing machine, fridge, microwave oven, etc.

- (3) Home automation and security systems: Air conditioners, sprinklers, intruder detection alarms, closed circuit television cameras, fire alarms, etc.

- (4) Automotive industry: Anti-lock breaking systems (ABS), engine control, ignition systems, automatic navigation systems, etc.

- Telecom: Cellular telephones, telephone switches, handset multimedia applications, etc.

- (6) Computer peripherals: Printers, scanners, fax machines, etc.

- (7) Computer networking systems: Network routers, switches, hubs, firewalls, etc.

- (8) Healthcare: Different kinds of scanners, EEG, ECG machines etc.

- (9) Measurement & Instrumentation: Digital multimeters, digital CROs, logic analysers PLC systems, etc.

- (10) Banking & Retail: Automatic teller machines (ATM) and currency counters, point of sales (POS)

- (11) Card Readers: Barcode, smart card readers, hand held devices, etc.

- (12) Wearable Devices: Health and Fitness Trackers, Smartphone Screen extension for notifications, etc.

- (13) Cloud Computing and Internet of Things (IOT)

2.

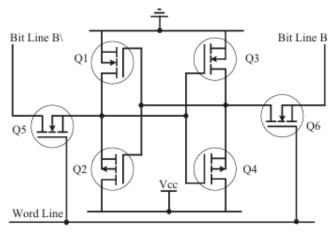

**2.2.2.1 Static RAM (SRAM)** Static RAM stores data in the form of voltage. They are made up of flip-flops. Static RAM is the fastest form of RAM available. In typical implementation, an SRAM cell (bit) is realised using six transistors (or 6 MOSFETs). Four of the transistors are used for building the latch (flip-flop) part of the memory cell and two for controlling the access. SRAM is fast in operation due to its resistive networking and switching capabilities. In its simplest representation an SRAM cell can be visualised as shown in Fig. 2.10.

Fig. 2.10 SRAM cell implementation

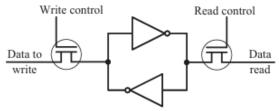

This implementation in its simpler form can be visualised as two-cross coupled inverters with read/write control through transistors. The four transistors in the middle form the cross-coupled inverters. This can be visualised as shown in Fig. 2.11.

From the SRAM implementation diagram, it is clear that access to the memory cell is controlled by the line Word Line, which controls the access transistors (MOSFETs) Q5 and Q6. The access transistors control the connection to bit lines B & B\. In order to write a value to the memory cell, apply the desired value to the bit control lines (For writing 1, make B = 1 and B\=0; For writing 0, make B = 0 and B\=1) and assert the Word Line (Make Word line

Fig. 2.11 Visualisation of SRAM cell

high). This operation latches the bit written in the flip-flop. For reading the content of the memory cell, assert both B and B\ bit lines to 1 and set the Word line to 1.

The major limitations of SRAM are low capacity and high cost. Since a minimum of six transistors are required to build a single memory cell, imagine how many memory cells we can fabricate on a silicon wafer.

2.2.2.2 Dynamic RAM (DRAM) Dynamic RAM stores data in the form of charge. They are made up of MOS transistor gates. The advantages of DRAM are its high density and low cost compared to SRAM. The disadvantage is that since the information is stored as charge it gets leaked off with time and to prevent this they need to be refreshed periodically. Special circuits called DRAM controllers are used for the refreshing operation. The refresh operation is done periodically in milliseconds interval. Figure 2.12 illustrates the typical implementation of a DRAM cell.

The MOSFET acts as the gate for the incoming and outgoing data whereas the capacitor acts as the bit storage unit. Table given below summarises the relative merits and demerits of SRAM and DRAM technology.

Fig. 2.12 DRAM cell implementation

| SRAM cell                                      | DRAM cell                                                                                                                     |  |  |  |  |

|------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Made up of 6 CMOS transistors (MOSFET)         | Made up of a MOSFET and a capacitor                                                                                           |  |  |  |  |

| Doesn't require refreshing                     | Requires refreshing                                                                                                           |  |  |  |  |

| Low capacity (Less dense)                      | High capacity (Highly dense)                                                                                                  |  |  |  |  |

| More expensive                                 | Less expensive                                                                                                                |  |  |  |  |

| Fast in operation. Typical access time is 10ns | Slow in operation due to refresh requirements. Typical access<br>time is 60ns. Write operation is faster than read operation. |  |  |  |  |

3.

| Harvard Architecture                                    | Von-Neumann Architecture                                                                                                               |

|---------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| Separate buses for instruction and data fetching        | Single shared bus for instruction and data fetching                                                                                    |

| Easier to pipeline, so high performance can be achieved | Low performance compared to Harvard architecture                                                                                       |

| Comparatively high cost                                 | Cheaper                                                                                                                                |

| No memory alignment problems                            | Allows self modifying codes*                                                                                                           |

|                                                         | Since data memory and program memory are stored<br>physically in the same chip, chances for accidental<br>corruption of program memory |

- **2.1.1.8 Big-Endian vs. Little-Endian Processors/Controllers** Endianness specifies the order in which the data is stored in the memory by processor operations in a multibyte system (Processors whose word size is greater than one byte). Suppose the word length is two byte then data can be stored in memory in two different ways:

- Higher order of data byte at the higher memory and lower order of data byte at location just below the higher memory.

- (2) Lower order of data byte at the higher memory and higher order of data byte at location just below the higher memory.

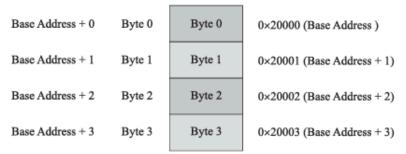

**Little-endian** (Fig. 2.3) means the lower-order byte of the data is stored in memory at the lowest address, and the higher-order byte at the highest address. (The little end comes first.) For example, a 4 byte long integer **Byte3 Byte2 Byte1 Byte0** will be stored in the memory as shown below:

Fig. 2.3 Little-Endian operation

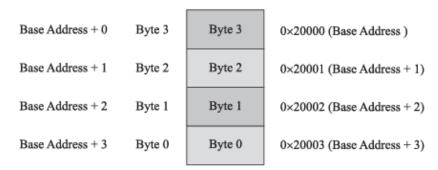

**Big-endian** (Fig. 2.4) means the higher-order byte of the data is stored in memory at the lowest address, and the lower-order byte at the highest address. (The big end comes first.) For example, a 4 byte long integer **Byte3 Byte2 Byte1 Byte0** will be stored in the memory as follows:

Fig. 2.4 Big-Endian operation

**2.4.1.3 Universal Asynchronous Receiver Transmitter (UART)** Universal Asynchronous Receiver Transmitter (UART) based data transmission is an asynchronous form of serial data transmission. UART based serial data transmission doesn't require a clock signal to synchronise the transmitting end and receiving end for transmission. Instead it relies upon the pre-defined agreement between the transmitting device and receiving device. The serial communication settings (Baudrate, number of bits per byte, parity, number of start bits and stop bit and flow control) for both transmitter and receiver should be set as identical. The start and stop of communication is indicated through inserting special bits in the data stream. While sending a byte of data, a start bit is added first and a stop bit is added at the end of the bit stream. The least significant bit of the data byte follows the 'start' bit.

The 'start' bit informs the receiver that a data byte is about to arrive. The receiver device starts polling its 'receive line' as per the baudrate settings. If the baudrate is 'x' bits per second, the time slot available for one bit is 1/x seconds. The receiver unit polls the receiver line at exactly half of the time slot available for the bit. If parity is enabled for communication, the UART of the transmitting device adds a parity bit (bit value is 1 for odd number of 1s in the transmitted bit stream and 0 for even number of 1s). The UART of the receiving device calculates the parity of the bits received and compares it with the received parity bit for error checking. The UART of the receiving device discards the 'Start', 'Stop' and 'Parity' bit from the received bit stream and converts the received serial bit data to a word (In the case of 8 bits/byte, the byte is formed with the received 8 bits with the first received bit as the LSB and last received data bit as MSB).

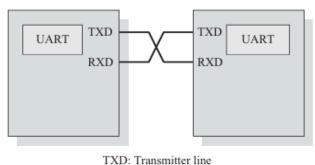

For proper communication, the 'Transmit line' of the sending device should be connected to the 'Receive line' of the receiving device. Figure 2.28 illustrates the same.

RXD: Receiver line

Fig. 2.28 UART Interfacing

In addition to the serial data transmission function, UART provides hardware handshaking signal support for controlling the serial data flow. UART chips are available from different semiconductor manufacturers. National Semiconductor's 8250 UART chip is considered as the standard setting UART. It was used in the original IBM PC.

Nowadays most of the microprocessors/controllers are available with integrated UART functionality and they provide built-in instruction support for serial data transmission and reception.

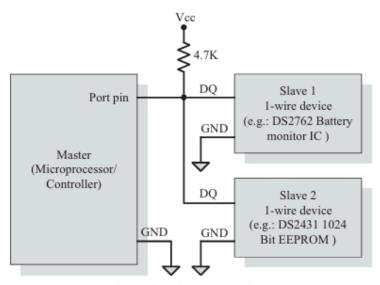

**2.4.1.4 1-Wire Interface** 1-wire interface is an asynchronous half-duplex communication protocol developed by Maxim Dallas Semiconductor (<a href="http://www.maxim-ic.com">http://www.maxim-ic.com</a>). It is also known as **Dallas 1-Wire® protocol**. It makes use of only a single signal line (wire) called DQ for communication and follows the master-slave communication model. One of the key feature of 1-wire bus is that it allows power to be sent along the signal wire as well. The 1-Wire slave devices incorporate internal capacitor (typically of the order of 800 pF) to power the device from the signal line. The 1-wire interface supports a single master and one or more slave devices on the bus. The bus interface diagram shown in Fig. 2.29 illustrates the connection of master and slave devices on the 1-wire bus.

Fig. 2.29 1-Wire Interface bus

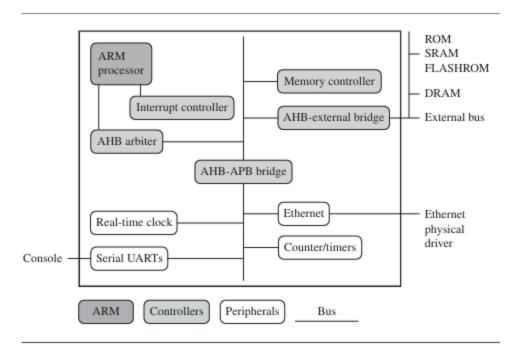

Figure 1.2 An example of an ARM-based embedded device, a microcontroller.

Figure 1.2 shows a typical embedded device based on an ARM core. Each box represents a feature or function. The lines connecting the boxes are the buses carrying data. We can separate the device into four main hardware components:

- The ARM processor controls the embedded device. Different versions of the ARM processor are available to suit the desired operating characteristics. An ARM processor comprises a core (the execution engine that processes instructions and manipulates data) plus the surrounding components that interface it with a bus. These components can include memory management and caches.

- Controllers coordinate important functional blocks of the system. Two commonly found controllers are interrupt and memory controllers.

- The peripherals provide all the input-output capability external to the chip and are responsible for the uniqueness of the embedded device.

- A bus is used to communicate between different parts of the device.

#### 1.3.1 ARM BUS TECHNOLOGY

Embedded systems use different bus technologies than those designed for x86 PCs. The most common PC bus technology, the Peripheral Component Interconnect (PCI) bus, connects such devices as video cards and hard disk controllers to the x86 processor bus. This type of technology is external or off-chip (i.e., the bus is designed to connect mechanically and electrically to devices external to the chip) and is built into the motherboard of a PC.

In contrast, embedded devices use an on-chip bus that is internal to the chip and that allows different peripheral devices to be interconnected with an ARM core.

There are two different classes of devices attached to the bus. The ARM processor core is a bus master—a logical device capable of initiating a data transfer with another device across the same bus. Peripherals tend to be bus slaves—logical devices capable only of responding to a transfer request from a bus master device.

A bus has two architecture levels. The first is a physical level that covers the electrical characteristics and bus width (16, 32, or 64 bits). The second level deals with protocol—the logical rules that govern the communication between the processor and a peripheral.

ARM is primarily a design company. It seldom implements the electrical characteristics of the bus, but it routinely specifies the bus protocol.

#### 1.3.2 AMBA BUS PROTOCOL

The Advanced Microcontroller Bus Architecture (AMBA) was introduced in 1996 and has been widely adopted as the on-chip bus architecture used for ARM processors. The first AMBA buses introduced were the ARM System Bus (ASB) and the ARM Peripheral Bus (APB). Later ARM introduced another bus design, called the ARM High Performance Bus (AHB). Using AMBA, peripheral designers can reuse the same design on multiple projects. Because there are a large number of peripherals developed with an AMBA interface, hardware designers have a wide choice of tested and proven peripherals for use in a device. A peripheral can simply be bolted onto the on-chip bus without having to redesign an interface for each different processor architecture. This plug-and-play interface for hardware developers improves availability and time to market.

AHB provides higher data throughput than ASB because it is based on a centralized multiplexed bus scheme rather than the ASB bidirectional bus design. This change allows the AHB bus to run at higher clock speeds and to be the first ARM bus to support widths of 64 and 128 bits. ARM has introduced two variations on the AHB bus: Multi-layer AHB and AHB-Lite. In contrast to the original AHB, which allows a single bus master to be active on the bus at any time, the Multi-layer AHB bus allows multiple active bus masters. AHB-Lite is a subset of the AHB bus and it is limited to a single bus master. This bus was developed for designs that do not require the full features of the standard AHB bus.

AHB and Multi-layer AHB support the same protocol for master and slave but have different interconnects. The new interconnects in Multi-layer AHB are good for systems with multiple processors. They permit operations to occur in parallel and allow for higher throughput rates.

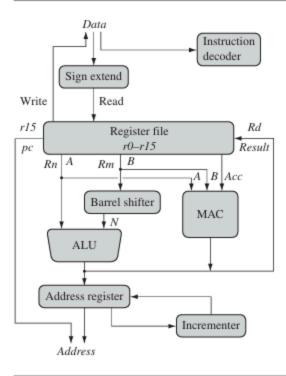

Figure 2.1 ARM core dataflow model.

Data enters the processor core through the *Data* bus. The data may be an instruction to execute or a data item. Figure 2.1 shows a Von Neumann implementation of the ARM—data items and instructions share the same bus. In contrast, Harvard implementations of the ARM use two different buses.

The instruction decoder translates instructions before they are executed. Each instruction executed belongs to a particular instruction set.

The ARM processor, like all RISC processors, uses a *load-store architecture*. This means it has two instruction types for transferring data in and out of the processor: load instructions copy data from memory to registers in the core, and conversely the store

instructions copy data from registers to memory. There are no data processing instructions that directly manipulate data in memory. Thus, data processing is carried out solely in registers.

Data items are placed in the register file—a storage bank made up of 32-bit registers. Since the ARM core is a 32-bit processor, most instructions treat the registers as holding signed or unsigned 32-bit values. The sign extend hardware converts signed 8-bit and 16-bit numbers to 32-bit values as they are read from memory and placed in a register.

ARM instructions typically have two source registers, Rn and Rm, and a single result or destination register, Rd. Source operands are read from the register file using the internal buses A and B, respectively.

The ALU (arithmetic logic unit) or MAC (multiply-accumulate unit) takes the register values Rn and Rm from the A and B buses and computes a result. Data processing instructions write the result in Rd directly to the register file. Load and store instructions use the ALU to generate an address to be held in the address register and broadcast on the Address bus. One important feature of the ARM is that register Rm alternatively can be preprocessed in the barrel shifter before it enters the ALU. Together the barrel shifter and ALU can calculate a wide range of expressions and addresses.

After passing through the functional units, the result in Rd is written back to the register file using the Result bus. For load and store instructions the incrementer updates the address register before the core reads or writes the next register value from or to the next sequential memory location. The processor continues executing instructions until an exception or interrupt changes the normal execution flow.

Now that you have an overview of the processor core we'll take a more detailed look at some of the key components of the processor: the registers, the current program status register (cpsr), and the pipeline.

7.

### PROCESSOR MODES

The processor mode determines which registers are active and the access rights to the *cpsr* register itself. Each processor mode is either privileged or nonprivileged: A privileged mode allows full read-write access to the *cpsr*. Conversely, a nonprivileged mode only allows read access to the control field in the *cpsr* but still allows read-write access to the condition flags.

There are seven processor modes in total: six privileged modes (abort, fast interrupt request, interrupt request, supervisor, system, and undefined) and one nonprivileged mode (user).

The processor enters abort mode when there is a failed attempt to access memory. Fast interrupt request and interrupt request modes correspond to the two interrupt levels available on the ARM processor. Supervisor mode is the mode that the processor is in after reset and is generally the mode that an operating system kernel operates in. System mode is a special version of user mode that allows full read-write access to the cpsr. Undefined mode is used when the processor encounters an instruction that is undefined or not supported by the implementation. User mode is used for programs and applications.

### Processor mode.

| Mode                   | Abbreviation | Privileged | Mode[4:0] |

|------------------------|--------------|------------|-----------|

| Abort                  | abt          | yes        | 10111     |

| Fast interrupt request | fiq          | yes        | 10001     |

| Interrupt request      | irq          | yes        | 10010     |

| Supervisor             | svc          | yes        | 10011     |

| System                 | sys          | yes        | 11111     |

| Undefined              | und          | yes        | 11011     |

| User                   | usr          | no         | 10000     |