| USN |  |  |  |  |  |

|-----|--|--|--|--|--|

**Internal Assessment Test 1 – May 2025**

| Sub:  | Basic Electron                                                                                                        | nics                                                                         |                                                                |                                                       |       | Code:          | BBEE203                             | Branch | EC  |     |

|-------|-----------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|----------------------------------------------------------------|-------------------------------------------------------|-------|----------------|-------------------------------------|--------|-----|-----|

| Date: | 06/05/2025                                                                                                            | Duration:                                                                    | 90 min's                                                       | Max<br>Marks:                                         | 50    | Sem/Sec:       | 2 <sup>nd</sup> Sem (Secs: M,N,O,P) |        | O   | BE  |

|       |                                                                                                                       | Answer a                                                                     | any FIVI                                                       | E FULL Que                                            | stion | <u>1S</u>      |                                     | Marks  | СО  | RBT |

| 1.    | germanium dioc<br>b. Draw th<br>and plot the pos<br>$I_F$ $R_1$ $+$<br>$100 \Omega$ $D_1$ $+$<br>de-resistor series c | de. de de load line sition of Q-Poi $I_{ m F}$ $I_{ m F}$ $V_{ m F}$ direuit | for the cir<br>int.<br>(mA)<br>50<br>40<br>30<br>20<br>10<br>0 | Cuit in Fig. on  Diode characteris 2 3 V <sub>F</sub> | tic 4 | diode forward  | characteristic  (V)                 | 5+5    | CO1 | L3  |

| 2.    | and $r_a = 0$ . Then $ \frac{E}{1.5 \text{ V}} = \frac{I_F}{I_F} $ (a) Diode                                          | recalculate th $R_1$ $10 \Omega$ $D_1$                                       | e current t                                                    | in Fig. assumaking $r_a = 0.25$                       | 5Ω.   |                |                                     | 6+4    | CO1 | L2  |

| 3.    | a) Discuss the                                                                                                        | e working of                                                                 | the Bridg                                                      | e rectifier wi                                        | th ne | at circuit dia | grams.                              | 7+3    | CO1 | L3  |

|       | b) Determine the peak output voltage and current for a bridge rectifier circuit when the secondary RMS voltage is 30V, $R_L$ =300 $\Omega$ and the diode forward drop is 0.7V.                                                                                                                      |               |     |    |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-----|----|

| 4.    | Illustrate RC-π filter in detail.                                                                                                                                                                                                                                                                   | 10            | CO1 | L2 |

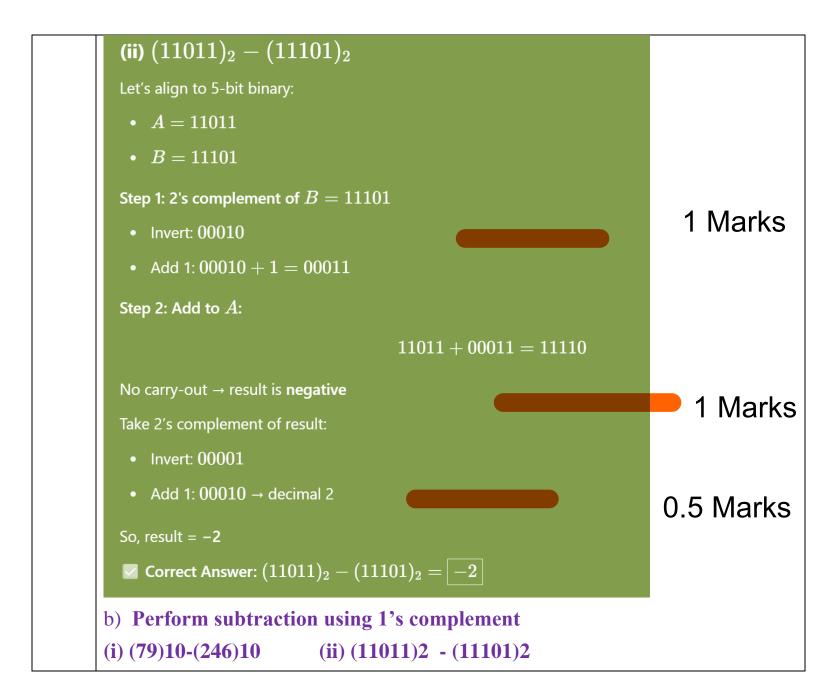

| 5. a) | Perform subtraction using 2's complement (i) (51)10-(24)10 (ii) (11011)2 - (11101)2                                                                                                                                                                                                                 | 06<br>+<br>04 | CO3 | L3 |

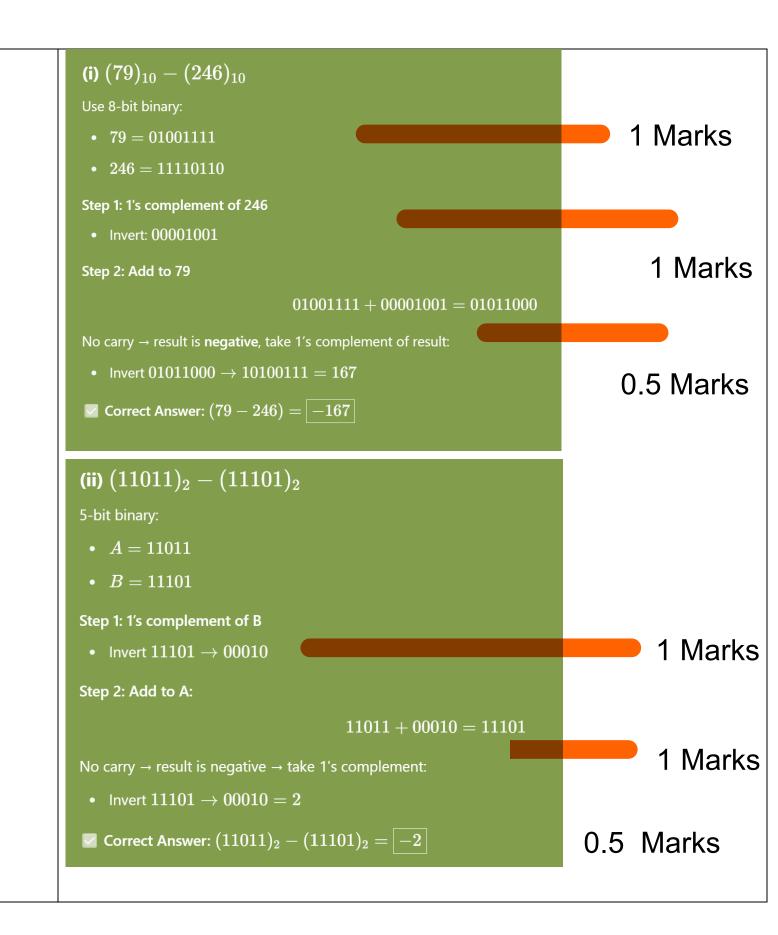

| b)    | Perform subtraction using 1's complement (i) (79)10-(246)10 (ii) (11011)2 - (11101)2                                                                                                                                                                                                                |               |     |    |

| 6.    | <ul> <li>a. Build the equation Y=AB+CD+E to realize using NAND Gates</li> <li>b. Express the Boolean expression F=X'Y+XZ'+(X+Y+Z')' using</li> <li>• Sum of Minterms (SOP)</li> <li>• Product of Maxterms (POS)</li> </ul>                                                                          | 4+6           | CO3 | L3 |

| 7.    | Design a full adder and implement using basic logic gates.                                                                                                                                                                                                                                          | 10            | CO3 | L3 |

| 8.    | State and prove De Morgan's Law for a function of three variables.                                                                                                                                                                                                                                  | 10            | CO3 | L2 |

| 9.    | A 5V zener diode has a maximum rated power dissipation of 500 mW. If the diode is to be used in a simple regulator circuit to supply a regulated 5V to a load having a resistance of 500 $\Omega$ , determine a suitable value of series resistor for operation in conjunction with a supply of 9V. | 10            | CO1 | L3 |

## Solution and Scheme of IAT-1 for Basic Electronics

a) Explain the forward and reverse characteristics of a silicon diode and germanium diode.

## **Solution:**

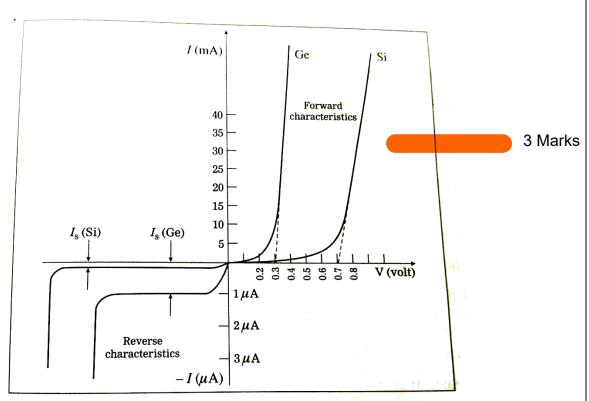

Junction diode characteristics, Ge and Si

2 Marks

PN- Junction diode characteristics, Ge and Si Explanation:

- (1) Forward bias characteristics: There is forward current only after the barrier potential of the pn-junction is overcome. Then there is an exponential rise in the current beyond the knee region. The forward bias voltage required to reach the region of upward swing is called the threshold voltage VT or cut in voltage. When rounded off to the nearest, the threshold voltage is 0.3 V for a germanium diode and 0.7 V for a silicon diode.

- (2) Reverse bias characteristics: In the reverse bias, the potential barrier at the junction is large and the current due to majority carriers in each region is zero. However, minority charge carriers are able to cross the junction and constitute a very small current in the reverse direction. This reverse current quickly reaches its maximum or saturation value and remains fairly constant with increase in the reverse bias voltage. It is called the reverse saturation current Is, which is typically a few nanoamperes for a silicon diode and a few microamperes for a germanium diode. Too high a negative voltage results in a sharp change in the reverse bias characteristics. At a certain characteristic negative voltage, called the peak inverse voltage (PIV) or

breakdown voltage, the current in the reverse direction increases very rapidly. In general, a silicon diode has a higher PIV rating (~1000V) than a germanium diode (~400V).

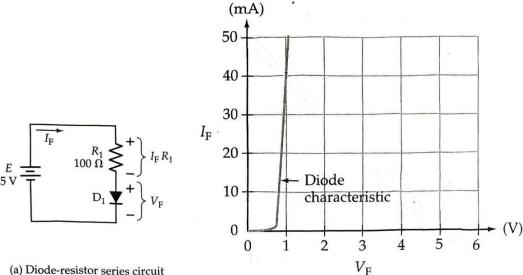

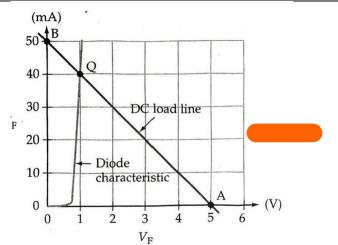

b) Draw the dc load line for the circuit in Fig. on the diode forward characteristic and plot the position of Q-Point.

#### Solution

Substitute

$$I_F = 0$$

into  $E = (I_F R_1) + V_F$  (2-3)

$$E = (I_F R_1) + V_F = 0 + V_F$$

or

$$V_F = E = 5 \text{ V}$$

1 Marks

Plot point A on the diode characteristic at

$$I_{\rm F} = 0$$

and  $V_{\rm F} = 5$  V

Now substitute  $V_F = 0$  into Eq. 2-3,

$$E = (I_F R_1) + 0$$

$I_F = \frac{E}{R_1} = \frac{5 \text{ V}}{100 \Omega}$

$= 50 \text{ mA}$

2 Marks

giving

Plot point B on the diode characteristic at

$$I_{\rm F} = 50$$

mA and  $V_{\rm F} = 0$

Draw the dc load line through points A and B.

2 Marks , Q (1V,40mA)

(b) Plotting the dc load line on the diode characteristics

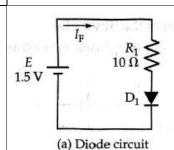

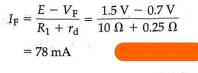

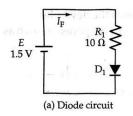

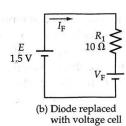

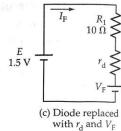

a) Calculate  $I_F$  for the diode circuit in Fig. assuming that the diode has  $V_F=0.7~V$  and  $r_d=0.$  Then recalculate the current taking  $r_d=0.25\Omega.$

#### Solution

Substituting  $V_{\rm F}$  as the diode equivalent circuit (Fig. 2-12b),

$$I_{\rm F} = \frac{E - V_{\rm F}}{R_{\rm 1}} = \frac{1.5 \,\mathrm{V} - 0.7 \,\mathrm{V}}{10 \,\Omega}$$

Substituting  $V_{\rm F}$  and  $r_{\rm d}$  as the diode equivalent circuit (Fig. 2-12c),

2 Marks

3 Marks

Figure 2-12 Diode circuits for Ex. 2-5.

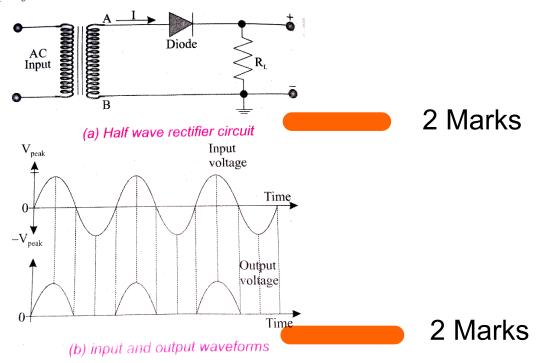

## b) Write short notes on Half wave rectifier with circuit diagrams and waveforms

**Solution:** Rectification is the process of converting alternating current into direct current is called rectification. In half wave rectifier circuit, either a positive half of the negative half of the AC input is passed through while the other half is blocked. Only one half of the input wave reaches the output. A p-n junction can be used as half wave rectifier.

When the positive half cycle of the AC input signal passes through the circuit , terminal A become positive with respect to terminal B. The diode is forward biased and hence it conducts. The current flows through the load resistance RL and AC voltage developed across RL constitutes the output voltage V0 and the wavelength of the diode is shown in the fig (b) When the negative half cycle of the AC input signal passes through the circuit , terminal a is negative with respect to terminal B . Now the diode is reverse biased and does not conduct and hence no current passes through RL . The reverse saturation current in a diode is negligible. Since there is no voltage drop across RL , the negative half cycle of AC supply is suppressed at the output . The output of the half wave rectifier is not a steady DC voltage but a pulsating wave . The efficient of half wave rectifier is 40.6% .

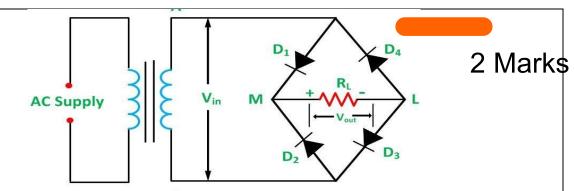

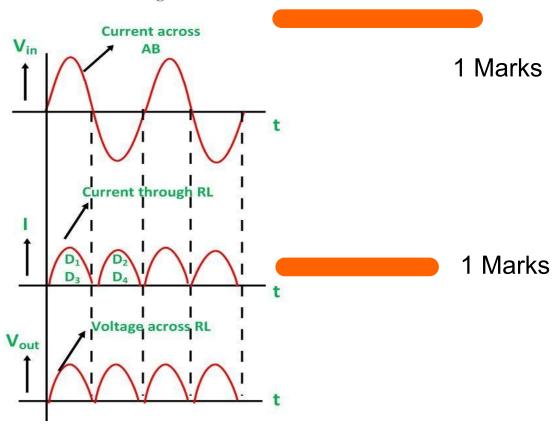

## a) Discuss the working of the Bridge rectifier with neat circuit diagrams.

**Solution:** In Full Wave Bridge Rectifier, an ordinary transformer is used in place of a center-tapped transformer. The circuit forms a bridge connecting the four diodes  $D_1$ ,  $D_2$ ,  $D_3$ , and  $D_4$ . The circuit diagram of the Full Wave Bridge Rectifier is shown below.

The AC supply which is to be rectified is applied diagonally to the opposite ends of the bridge. Whereas, the load resistor  $R_L$  is connected across the remaining two diagonals of the opposite ends of the bridge.

**Operation of Full Wave Bridge Rectifier**

When an AC supply is switched ON, the alternating voltage V<sub>in</sub> appears across the terminals AB of the secondary winding of the transformer which needs rectification. During the positive half cycle of the secondary voltage, end A becomes positive, and end B becomes negative as shown in the figure below.

The diodes  $D_1$  and  $D_3$  are forward biased and the diodes  $D_2$  and  $D_4$  are reversed biased. Therefore, diode  $D_1$  and  $D_3$  conduct, and diode  $D_2$  and  $D_4$  do not conduct. The current (i) flows through diode  $D_1$ , load resistor  $R_L$  (from M to L), diode  $D_3$ , and the transformer secondary. The waveform of the full-wave bridge rectifier is shown below.

b) Determine the peak output voltage and current for a bridge rectifier circuit when the secondary RMS voltage is 30V,  $R_L$ =300 $\Omega$  and the diode forward drop is 0.7V.

To determine the **peak output voltage** and **peak output current** for a **bridge rectifier** with the following specifications:

- ullet Secondary RMS Voltage,  $V_{

m RMS}=30~{

m V}$

- ullet Load Resistance,  $R_L=300~\Omega$

- ullet Diode Forward Voltage Drop (each diode),  $V_D=0.7~

m V$

## Step 1: Convert RMS to Peak Voltage

For a sinusoidal AC voltage:

$$V_{

m peak} = V_{

m RMS} imes \sqrt{2} = 30 imes 1.414 = 42.43 ~

m V$$

1 Marks

**Step 2: Account for Diode Drops**

In a bridge rectifier, two diodes conduct in each half-cycle. So, the total forward voltage drop is:

$$V_{

m drop} = 2 imes 0.7 = 1.4 \

m V$$

Step 3: Calculate Peak Output Voltage

2 Marks

$$V_{

m out,\,peak} = V_{

m peak} - V_{

m drop} = 42.43 - 1.4 = 41.03~{

m V}$$

**Step 4: Calculate Peak Output Current**

2 Marks

$$I_{

m peak} = rac{V_{

m out, \, peak}}{R_L} = rac{41.03}{300} pprox 0.1368 \ {

m A} = 136.8 \ {

m mA}$$

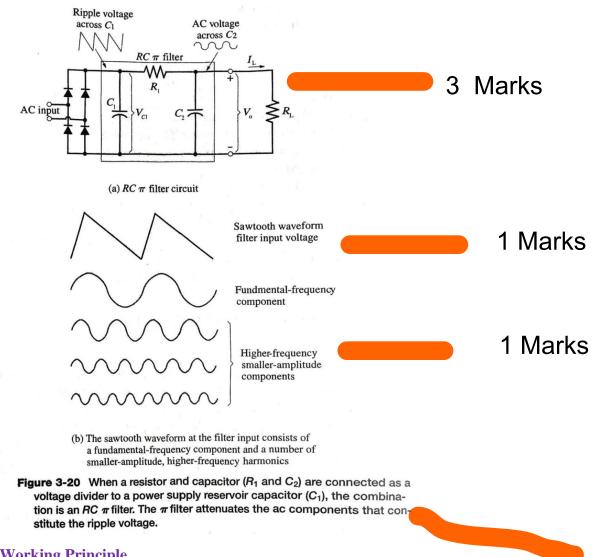

## Illustrate RC- $\pi$ filter in detail.

#### **Solution:**

An RC- $\pi$  filter is a low-pass filter commonly used in power supply circuits, particularly in voltage regulators and ripple filters. The name " $\pi$ " comes from its topology, which resembles the Greek letter  $\pi$ . It uses resistors (R) and capacitors (C) in a specific configuration to reduce AC ripple and allow DC to pass through.

4

RC-π Filter Overview

An RC- $\pi$  filter typically consists of:

Two capacitors (C1 and C2) connected from the input and output lines to ground.

One resistor (R) in between the two capacitors and in series with the line.

It looks like this in a circuit diagram:

## **Working Principle**

The first capacitor (C1) shunts high-frequency AC (like ripple) to ground.

The resistor (R) then limits the remaining AC component by forming an RC time constant with C1 and C2.

The second capacitor (C2) further filters any residual AC signal, providing a smoother DC at the output.

## 1 Marks

This cascade of shunting and series impedance effectively attenuates unwanted frequencies.

It determines how much high-frequency noise is filtered out.

## 1 Marks

#### **Ripple Reduction:**

The more the capacitance and resistance (within reasonable values), the greater the attenuation of ripple voltage.

## 2 Marks

#### **Load Consideration:**

Too large a resistor may reduce the DC output due to voltage drop, so it's a balance between filtering and

| Applications  Power supply filters (after rec Audio equipment to eliminate Analog circuits needing clean                                                      | e high-frequency hum                                                                                        |           |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|-----------|

|                                                                                                                                                               | using 2's complement (ii) (11011)2 - (11101)2                                                               |           |

| (i) $(51)_{10} - (24)_{10}$<br>Step 1: Convert to 8-bit<br>• $51_{10} = 00110011$<br>• $24_{10} = 00011000$<br>Step 2: 2's complement<br>• Invert: $11100111$ | binary  of 24                                                                                               | 1 Marks   |

| • Add 1: 11100111 -                                                                                                                                           | 00110011 + 11101000 = 10011011                                                                              | 1 Marks   |

| This gives a carry out (si                                                                                                                                    | ince result is 9 bits), discard carry: $10011011 \Rightarrow \boxed{0011011} = 27_{10} \ -24) = \boxed{27}$ | 0.5 Marks |

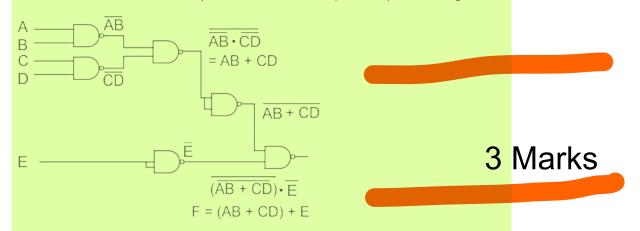

6. a) Build the equation Y=AB+CD+E to realize using NAND Gates

### **Solution**

Given, F = AB + CD + E

To implement it with the minimum number of NAND gates

## Concept

Bubbled input AND gate = NOR gate

Bubbled input OR gate = NAND gate

Let us observe the function implementation with help of 2-input NAND gates

We can observe that a minimum of 6 two-input NAND gates are required to implement the function

2 Marks

2 Marks

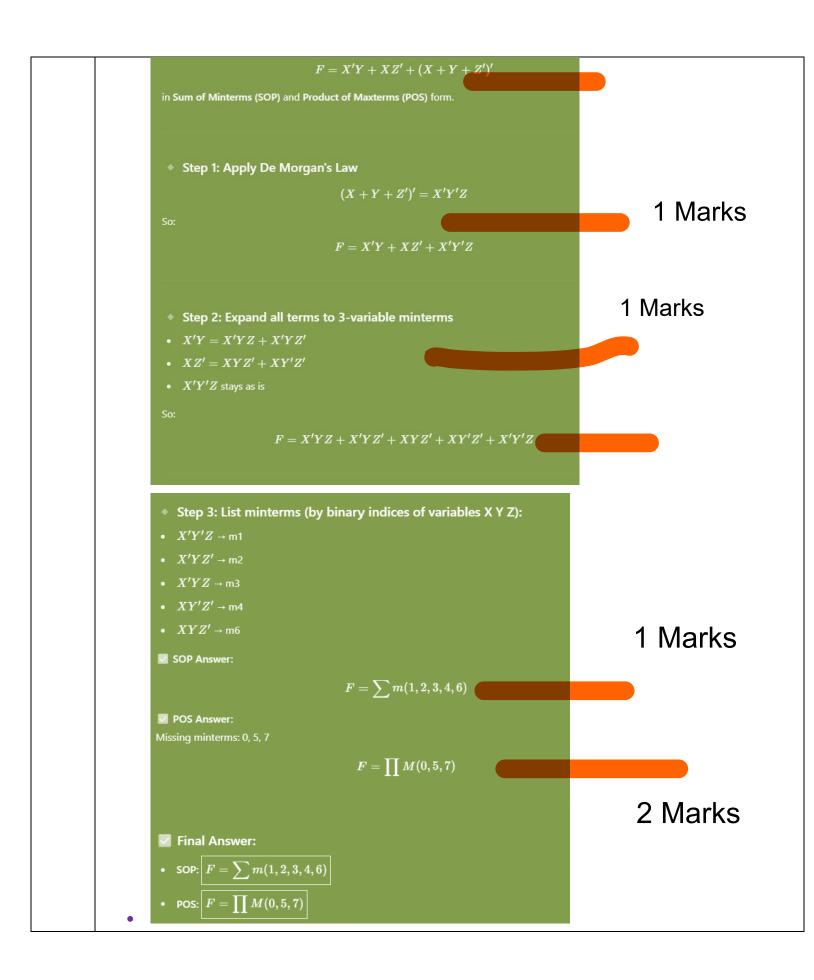

- b) Express the Boolean expression F=X'Y+XZ'+(X+Y+Z')' using

- Sum of Minterms (SOP)

- Product of Maxterms (POS)

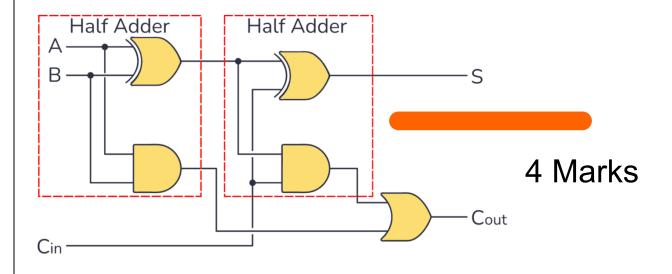

| 7. | Design | a full | adder | and i | nplement | าเรเทอ | hasic  | logic | gates |

|----|--------|--------|-------|-------|----------|--------|--------|-------|-------|

|    | Design | a Iuii | auuti | anu n | mbiemem  | using  | vasic. | iogic | gaics |

|   | Input |      | 0   | utput |

|---|-------|------|-----|-------|

| A | В     | C_in | Sum | C_out |

| 0 | 0     | 0    | 0   | 0     |

| 0 | 0     | 1    | 1   | 0     |

| 0 | 1     | 0    | 1   | 0     |

| 0 | 1     | 1    | 0   | 1     |

| 1 | 0     | 0    | 1   | 0     |

| 1 | 0     | 1    | 0   | 1     |

| 1 | 1     | 0    | 0   | 1     |

| 1 | 1     | 1    | 1   | 1     |

|   |       |      |     | -     |

Solution: L

$s=A \oplus B \oplus C_{in}$

3 Marks

Cout= AB+AC<sub>in</sub>+BC<sub>in</sub>

3 Marks

8. State and prove De Morgan's Law for a function of three variables.

De Morgan's Laws are fundamental rules in Boolean algebra and digital logic design. They express the relationship between the complement of logical operations (AND, OR) and can be extended to any number of variables.

## 2 Marks

#### De Morgan's Laws for Three Variables

Let A,B, and C be three Boolean variables. De Morgan's laws for three variables are:

1. First Law

$$\overline{A\cdot B\cdot C}=\overline{A}+\overline{B}+\overline{C}$$

2. Second Law:

$\overline{A+B+C} = \overline{A} \cdot \overline{B} \cdot \overline{C}$

2 Marks

|   | <b>Proof Using Truth Ta</b> |  |

|---|-----------------------------|--|

| ᆂ |                             |  |

Let's prove both laws using a truth table.

**Solution:**

| - |   |  |                     |                              |                |                |                   |                                              |       |                    |                                                    |

|---|---|--|---------------------|------------------------------|----------------|----------------|-------------------|----------------------------------------------|-------|--------------------|----------------------------------------------------|

|   | A |  | $A \cdot B \cdot C$ | $\overline{A\cdot B\cdot C}$ | $\overline{A}$ | $\overline{B}$ | $\overline{m{c}}$ | $\overline{A} + \overline{B} + \overline{C}$ | A+B+C | $\overline{A+B+C}$ | $\overline{A}\cdot \overline{B}\cdot \overline{C}$ |

|   | 0 |  |                     |                              |                |                |                   |                                              |       |                    |                                                    |

|   | 0 |  |                     |                              |                |                |                   |                                              |       |                    |                                                    |

|   | 0 |  |                     |                              |                |                |                   |                                              |       |                    |                                                    |

|   | 0 |  |                     |                              |                |                |                   |                                              |       |                    |                                                    |

|   | 1 |  |                     |                              |                |                |                   |                                              |       |                    |                                                    |

|   | 1 |  |                     |                              |                |                |                   |                                              |       |                    |                                                    |

|   | 1 |  |                     |                              |                |                |                   |                                              |       |                    |                                                    |

|   | 1 |  |                     |                              |                |                |                   |                                              |       |                    |                                                    |

From the table, you can observe:

- Column 5  $\overline{A \cdot B \cdot C}$  = Column 9  $\overline{A} + \overline{B} + \overline{C}$

- Column 12  $\overline{A+B+C}$  = Column 13  $\overline{A}\cdot\overline{B}\cdot\overline{C}$

Hence, **De Morgan's Laws for three variables are proven true**.

6 Marks

9

A 5V zener diode has a maximum rated power dissipation of 500 mW. If the diode is to be used in a simple regulator circuit to supply a regulated 5V to a load having a resistance of 500  $\Omega$ , determine a suitable value of series resistor for operation in conjunction with a supply of 9V.

### Step 1: RS (max)

At the threshold of regulation, all current from the source goes only to the load:

$$R_{S_{max}}=rac{V_{in}-V_{Z}}{I_{L}}=rac{4}{0.01}=400\,\Omega_{c}$$

### Step 2: RS (min)

As before (when all current goes to the zener):

$$R_{S_{min}} = rac{V_{in} - V_{Z}}{I_{Zmax}} = rac{4}{0.1} = 40\,\Omega$$

### Step 3: RS (midpoint)

$$R_{S_{mid}} = rac{R_{S_{min}} + R_{S_{max}}}{2} = rac{40 + 400}{2} = 220\,\Omega$$

## 4 Marks

# 4 MArks

# 2Marks