Sixth-Semester B.E./B.Tech. Degree Examination, June/July 2025 **VLSI Design and Testing**

Max. Marks: 100

21EC63

Note: Answer any FIVE full questions, choosing ONE full question from each module.

Module-1

- Describe the working of n type MOSFET with neat diagrams. Derive the equations for (10 Marks) drain current.

- b. Realize the CMOS gate for the following function:

Y = (A + B)C + DE.

(03 Marks)

c. Implement 2:1 multiplexes using transmission gate and explain its operation with necessary (07 Marks) timing diagram.

- 2 a. Explain the operation of CMOS inverter with help of transfer characteristics. Explain (07 Marks) various region of operation.

- b. With necessary circuit diagram operation of tristate inverter, and realize 2:1 multiplexer (10 Marks) with tristate inverter.

- c. Realize 3 i/p NOR gate using CMOS logic.

(03 Marks)

(06 Marks)

(04 Marks)

Module-2

- Explain the steps fabrication of CMOS n well process with neat sketches. (10 Marks)

- What is  $\lambda$  based design rules? Write design rules for following layers :

- iii) n<sub>+</sub> & P<sub>+</sub> diffusion iv) N well. i) Polysilicon ii) Metal

- c. Draw the layout diagram for 2 input NAND Gate.

- Define term "Logical effort". Describe the estimation of logic effort by using example.

- (06 Marks)

- b. Estimate parasitic delay of 2 input NAND gate with PMOS width of 2 NMOS width of 2. (04 Marks)

- c. Draw stick diagram for 3 input NAND gate and estimate the number of tracks and (10 Marks) dimensions.

Module-3

- Write the classification of semiconductor memories and explain typical memory organization of RAM memory with neat diagram. (10 Marks)

- Explain operation of full CMOS SRAM cell with necessary topology.

OR

1 of 2

Differentiate between DRAM and SRAM.

(04 Marks)

(10 Marks)

Explain the operation of 4 × 4 NOR based ROM array with necessary circuit diagram.

(06 Marks)

- c. Write short notes on:

- i) Flash memory cell

- ii) Ferro electric RAM.

(10 Marks)

Module-4

Describe the different types of bridging faults with example.

(06 Marks) (04 Marks)

Describe temporary faults in VLSI.

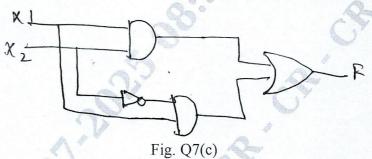

For the logic model shown below in Fig. Q7(c), find the Boolean difference with respect to  $X_2$ .

(10 Marks)

OR

a. Describe the following term of D algorithm with example.

i) Singular cover

ii) Propagation and D – cubes

iii) Primitive D - cubes and fault.

(10 Marks)

b. What is fault diagnosis? Explain one dimensional path sensitization technique for combinational circuits with an example. (10 Marks)

## Module-5

9 a. Define following with example:

i) Controllability ii) Observability. (08 Marks)

b. Describe any two Adhoc design rules for improving testability.

(06 Marks)

For state table – 1, find i) Homing sequence ii) Distinguish sequence and

iii) Response of machine in homing sequence.

(06 Marks)

| I/P       |       |       |

|-----------|-------|-------|

| P - state | X = 0 | X = 1 |

| Α         | B.0   |       |

| B         | A.0   | B.0   |

| C         | D.1   | A.0   |

| D         | D.1   | C.0   |

ORCMRIT LIBRARY

a. List LSSD design rules.

BANGALORE - 560 03"

(10 Marks)

b. Explain list generation based on functional fault models.

(10 Marks)