# Internal Assesment Test 2-OCT. 2018- Scheme and Solution

| Sub:     | COMPUTER O                      | RGANIZAT                |                 |                                           |            | Sub Code:  | 17CS34  | Branch: CSE |     |     |

|----------|---------------------------------|-------------------------|-----------------|-------------------------------------------|------------|------------|---------|-------------|-----|-----|

| Date:    | / 10 / 2018                     | Duration:               | 90 mins         | Max Marks                                 | : 50       | Sem / Sec: | 3(A,B,C | C)          | O   | BE  |

| <u>A</u> | nswer <b>FIVE</b> FUL           |                         |                 |                                           |            |            |         | MARKS       | СО  | RBT |

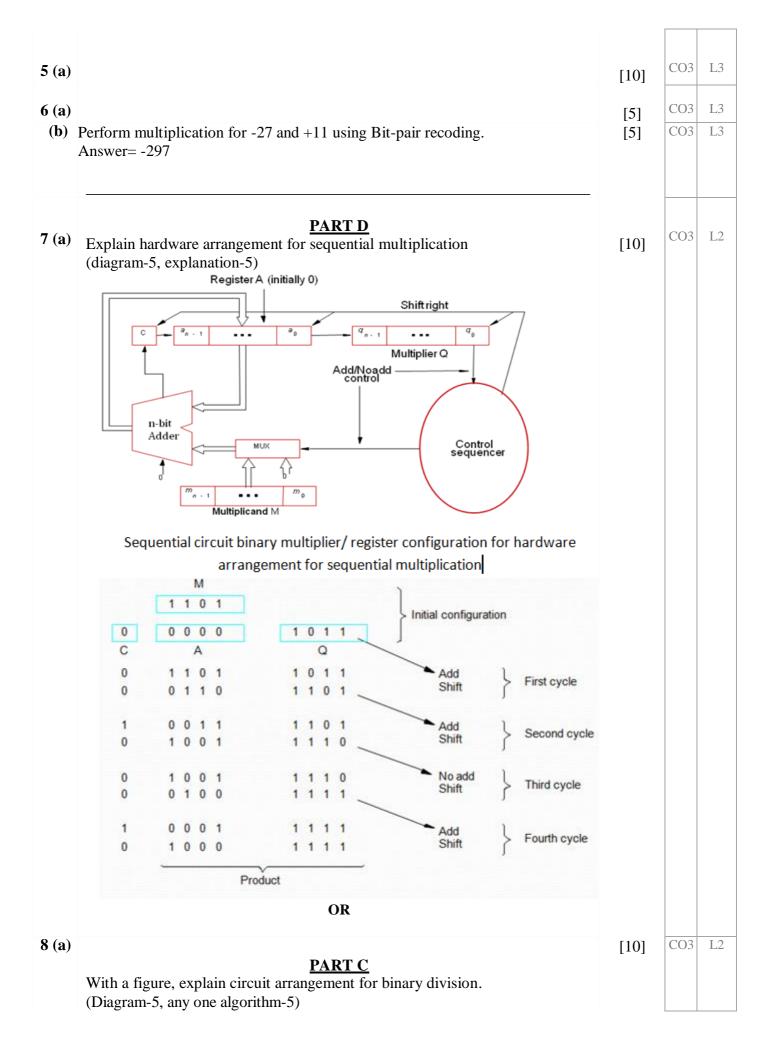

| 1 (a)    | With a neat dia (diagram -5 exp | gram, exp<br>planation- | lain gene<br>5) | PART A<br>eral 8-bit Pa                   | rallel int | erface.    |         | [10]        | CO2 | L2  |

|          |                                 |                         |                 |                                           |            |            | 3       | 5           |     |     |

|          | D7 —                            |                         |                 |                                           |            |            | > P7    |             |     |     |

|          | - ToBus.                        |                         |                 |                                           | DATAIR     | )          | : der   | °Ce         |     |     |

|          | Do T                            |                         |                 | 4 42                                      |            |            | PO      |             |     |     |

|          | 3                               |                         |                 |                                           |            |            |         | x -         |     |     |

|          | 3                               |                         |                 |                                           | ,          |            |         |             |     |     |

|          | 3                               | DATA                    | 1001            |                                           |            |            |         |             |     |     |

|          | 3                               |                         |                 |                                           |            |            |         |             |     |     |

|          |                                 | Dat                     |                 |                                           |            |            |         |             |     |     |

|          |                                 | 1000                    | ister.          |                                           |            |            |         |             |     |     |

|          |                                 | 7                       | 3,              | 1.2                                       |            |            |         |             |     |     |

|          | 3                               |                         |                 |                                           |            |            |         |             |     |     |

|          | 3                               | - 11                    | y 175 .         |                                           |            |            |         |             |     |     |

|          | My-address                      |                         |                 | de la |            |            | -2      |             |     |     |

|          | RSQ<br>RSI                      | 7                       | Register        | 1 1 1 1 1 1                               |            | Status     | (       |             |     |     |

|          | RSO                             |                         | Sueal           |                                           |            | Control    | ) 2     |             |     |     |

|          | RIW _                           |                         | Jan S. Franker  |                                           |            |            |         |             |     |     |

|          | - Ready                         |                         |                 |                                           |            |            |         |             |     |     |

|          | Accept «                        |                         |                 | 4 2 4 2 1                                 |            |            |         |             |     |     |

|          | INTR                            |                         |                 |                                           | 47 .       |            |         |             |     |     |

|          |                                 |                         | 101             | 21 - 10                                   | l interf   |            |         |             |     |     |

|          | an .                            | 1/ H gene               | al 8-6          | it paulle                                 | x interf   | ace        |         |             |     |     |

|          |                                 |                         |                 |                                           | 1.00       |            |         |             |     |     |

|          |                                 |                         |                 |                                           |            |            |         |             |     |     |

|          |                                 |                         |                 |                                           |            |            | •       | 16          |     | L   |

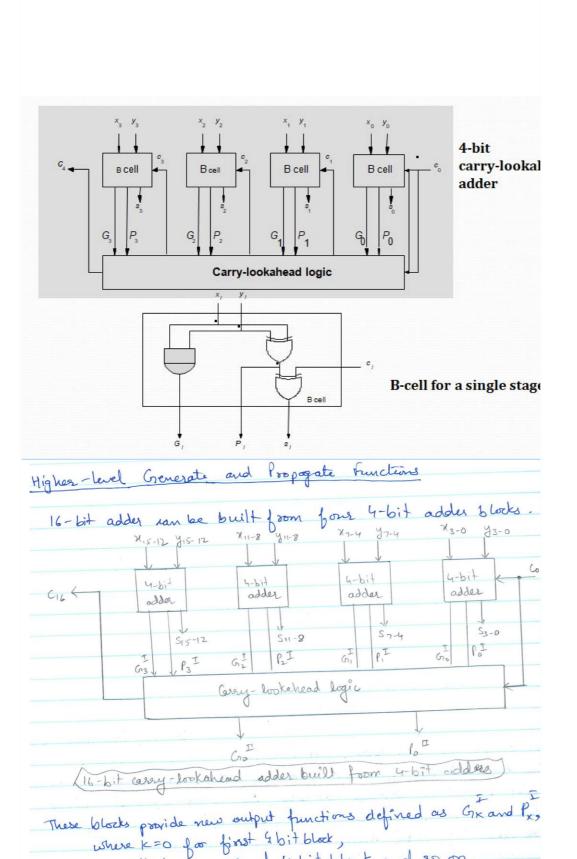

| Data lines Po to Po can be used for either input                                                                      |      |      |

|-----------------------------------------------------------------------------------------------------------------------|------|------|

| or output purposes.                                                                                                   |      |      |

| for increased flexibility,                                                                                            |      |      |

| some lives can be used as inputs, and                                                                                 |      |      |

| -> some lives can be used as outputs.                                                                                 |      |      |

| The DATAOUT register is connected to data lines via                                                                   |      |      |

| 3-state drivers that are untrolled by DDR (Data Direction Register).                                                  | _    |      |

| The processor can write any 8-bit pattern into DDR.                                                                   |      |      |

| DDR =1,                                                                                                               |      |      |

| Then, dat line acts as an output line;                                                                                |      |      |

| Two lines, C, and C, are used to control the interact                                                                 |      |      |

|                                                                                                                       | -    |      |

| ion between interface - circuit and i/o device.                                                                       |      |      |

| These two lines are programmable                                                                                      |      |      |

| signaling, including the handshake.                                                                                   |      |      |

| The Ready and Accept lines are the handshake control                                                                  |      |      |

| lines on the processor - bus side. Hence, the Ready                                                                   |      |      |

| and Accept lives can be connected to the output of                                                                    |      |      |

| Master-ready and Slave-ready.                                                                                         |      |      |

| The input signal My-address should be immeeted                                                                        |      |      |

| to the output of an address decoder. The address                                                                      |      |      |

| decoder recognizes the address assigned to the interface.                                                             |      |      |

| There are 3 register select lines: RSO-RSQ.                                                                           |      |      |

| Three register select lais allow up to eight registers                                                                |      |      |

| Y Y As                                                                                                                |      |      |

| An interrupt-request INTR is also provided. It should                                                                 |      |      |

| be connected to the interrust request line on the                                                                     |      |      |

| An interrupt-request INTR is also provided. It should be connected to the interrupt-request line on the computer bus. |      |      |

|                                                                                                                       |      |      |

|                                                                                                                       |      |      |

|                                                                                                                       |      |      |

|                                                                                                                       |      |      |

|                                                                                                                       |      |      |

|                                                                                                                       |      |      |

|                                                                                                                       |      |      |

| OR                                                                                                                    |      |      |

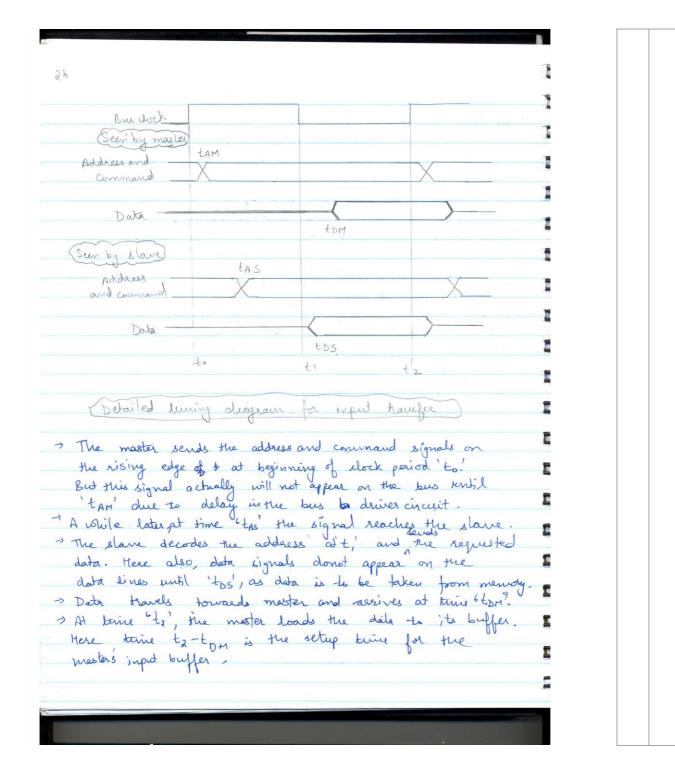

| With neat timing diagrams, evaluin evachronous hus                                                                    | [10] | CO2  |

| With neat timing diagrams, explain synchronous bus.                                                                   | [10] | 1002 |

| the doto transfer period to suit to the needs of the participating devices. A high frequency clock signal is used and that a complete data transfer eycle would span servical clock cycles. No. of clock cycles medical can vary from one device to another.  In the figure on previous page, during clock cycle 1, the master serves address and command to the bus requesting a lead operation.  At the beginning of clock cycles, the slave makes the decision to respond and begins access to the sequested data.  At clock cycle 3, slave places acknowledgement on the requested data on the bus.  The master strobes the data on the bus at the end of the 3nd cycle, and stores in buffer.  The bus transfer operation is more complete and processor may start with new data transfer operation.  Cock  Address  Command  Dota  Slave-ready                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | the data knill                                    | rake it po  | ossible to  | ansfer ope<br>adjust the                  | e duration    | of        |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|-------------|-------------|-------------------------------------------|---------------|-----------|--|

| such that a conflote data traveller syste would span several clook cycle. No. of clock cycles involved can vary from one device to another.  In the figure on previous page, during clock cycle 1, the master sends address and command to the bus, requesting a 'Read' operation.  At the beginning of clock cycles, the slave mates the decision to respond and begins access to the requested olate.  At clock cycle 3, slave places acknowledgement for the requested alote. The master strobes the data from the bus.  The master strobes the data from the bus at the end of the 3rd cycle, and stores in buffer.  The bus traveler operation is more complete and processor may start with new data traveler operation.  Clock  Address  Command  Dota                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                   |             |             |                                           |               |           |  |

| from one device to another.  In the figure on previous page, during clock cycle I, the master sends address and command to the bus, requesting a lead operation.  At the beginning of clock cycles, the slave makes the decision to respond and begins access to the requested data.  At clock cycle 3, blane places acknowledgement I on the requested data on the bus.  The master Strobes the data from the bus at the end of the 3rd cycle, and stores in buffer.  The bus transfer operation is now complete and processor may start with new data transfer operation.  Clock  Address  Command  Data  Slave-ready                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | such that a                                       | complete    | data tran   | efer ayde                                 | Lould         | span      |  |

| the figure on previous page, during clock cycle 1, the master sends address and command to the bus, requesting a kead operation.  At the beginning of clock cycle 2, the slave makes the decision to respond and begins access to the requested clote.  At clock cycle 3, slave places acknowledgement 1 on the request and the requested data on the bus.  The master Strobes the dada from the bus at the end of the 3rd cycle, and stores in buffer.  The bus traveler operation is now complete and provessor may start with new clata transfer operation.  Clock  Address  Command  Dota  Slave-ready                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | several clock                                     | yeles. No   | . of clock  | cycles in                                 | olved an      | Vary      |  |

| sequesting a Read operation.  At the beginning of clock cycles, the slave makes the decision to respond and begins access to the requested clate.  At clock cycle 3, slave places acknowledgement for the request and the requested data on the bus.  The master strobes the date from the bus at the end of the 3rd cycle, and stores in buffer.  The bus transfer operation is now complete and processor may start with new data transfer operation.  Clock  Address  Command  Data  Slave-resdy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0                                                 |             |             | ما درونده                                 | ) = 16 = = 0. | 1         |  |

| At the beginning of clock cycles, the slave makes the decision to respond and begins access to the requested clots.  At clock cycle 3, slave places acknowledgement of the requested data on the bus.  The master strobes the data from the bus at the end of the 3rd cycle, and stores in buffer.  The bus travefur operation is now complete and processor may start with new data travefur operation.  Clock  Address  Slave-ready  Slave-ready                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | the master of                                     | ends adds   | ress and    | command                                   | to the        | bus,      |  |

| At the beginning of clock cycle?, the slave makes the decision to respond and begins access to the requested clota.  At clock cycle 3, slave places acknowledgement of the requested data on the bus.  The master strobes the data from the bus at the end of the 3rd cycle, and stores in buffer.  The bus travelar operation is now complete and processor may start with new data travelar operation.  Clock  Address  Slave-ready  Slave-ready                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | requesting a 's                                   | lead' opera | ition.      |                                           |               |           |  |

| At clock cycle 3, slave places acknowledgement for the request and the requested data on the bus.  The master Strobes the data from the bus at the end of the 3rd cycle, and stores in buffer.  The bus travefor operation is now complete and provesoor may start with new data transfer operation.  Clock  Address  Command  Data  Slave-ready                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | At the beginn                                     | ing of d    | ock cycle & | , the sla                                 | we mak        | es the    |  |

| At clock cycle 3, slave places acknowledgement I on the request and the requested data on the bus.  The master strobes the data from the bus at the end of the 3rd cycle, and stores in buffer.  The bus transfer operation is now complete and processor may start with new data transfer operation.  Clock  Address  Command  Data  Slave-ready                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | decision to 8                                     | espond an   | nd begins   | access to                                 | the Regi      | rested    |  |

| The master Strobes the dodg from the bus at the end of the 3rd cycle, and stores in buffer. The bus travefer operation is now complete and provenous may start with new data transfer operation.  Clock  Command  Data  Slave-ready.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                   | 2 1/2       | alaca, auto | 0 . 1                                     | d 1           | 11.0      |  |

| The master Strobes the dodg from the bus at the end of the 3rd cycle, and stores in buffer.  The bus travefer operation is now complete and provesoor may start with new data transfer operation.  Clock  Address  Command  Data  Slave-ready                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | somest and                                        | the source  | ted data    | on the                                    | hud           | the       |  |

| end of the 3rd cycle, and stores in buffer. The bus transfer operation is now complete and provision may start with new data transfer operation.  Clock  Address  Command  Data  Slave-ready                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | The mester                                        | Strobes to  | 10 date     | from the                                  | bus at        | the       |  |

| Clock  Command  Dota  Slave-ready                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | end of the                                        | 3rd cycl    | e and       | stores in                                 | buffer        |           |  |

| Clock  Address  Command  Data  Slave-ready                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | The bus trave                                     | efer opera  | tion is m   | no cample                                 | ete and       | processor |  |

| Command  Dota  Slave-ready                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                   | 1,0         | data les    | males in                                  | sation.       |           |  |

| Address  Command  Data  Slave-ready                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | may start we                                      | the new     | charge The  | unsfer of                                 | 0 10.1        |           |  |

| Command  Data  Slave-ready.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | may start we                                      | m new       | chang The   | inster offe                               |               |           |  |

| Command  Data  Slave-ready.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | may start we                                      | the new     |             | inger ofe                                 |               |           |  |

| Dota  Slave-ready                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | may start we                                      | the new     |             | majer ope                                 |               |           |  |

| Dota  Slave-ready  *                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | may start we                                      | th new      |             | anger spe                                 |               |           |  |

| Slave-resdy_                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | may start we                                      | th new      |             | miger ope                                 | X             |           |  |

| Slave-resdy_                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | May start we ClockAddress                         | the new     |             | miger ope                                 |               |           |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | May Start we Clock  Address  Command              | The new     |             | miger spe                                 |               |           |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | May Start we Clock  Address  Command              | The new     |             | anger spe                                 |               |           |  |

| An input transfer using multiple clock cycles,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | May start we Clock  Address  Command  Data        | th new      |             | anger spe                                 |               |           |  |

| An input transfer using multiple clock cycles,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | May start we Clock  Address  Command  Data        | the new     |             | anger spe                                 |               |           |  |

| An input Kanefer using multiple clock cycles,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | May start we Clock  Address  Command  Data        | the new     |             | miger spe                                 |               |           |  |

| An input transfer using multiple clock cycles,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | May start we Clock  Address  Command  Data        | the new     |             |                                           |               |           |  |

| I Am mout Kaneger using multiple close yours,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | May start we Clock  Address  Command  Data        | th new      |             | La |               |           |  |

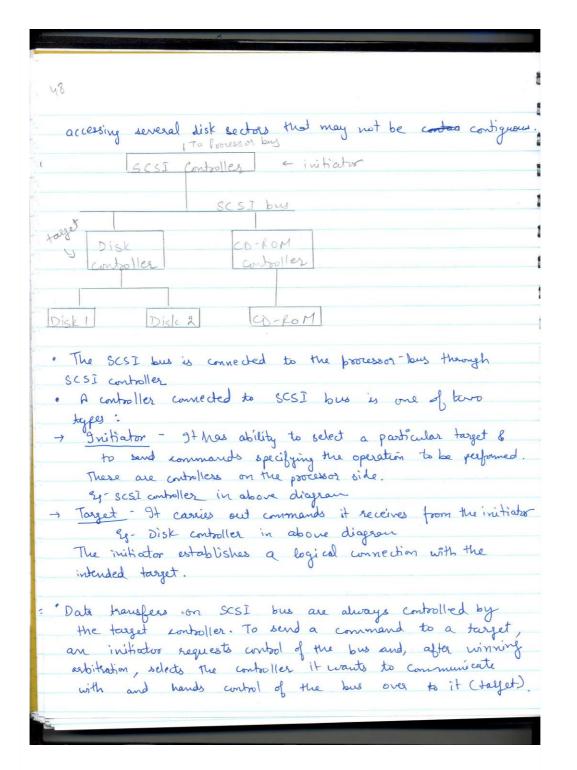

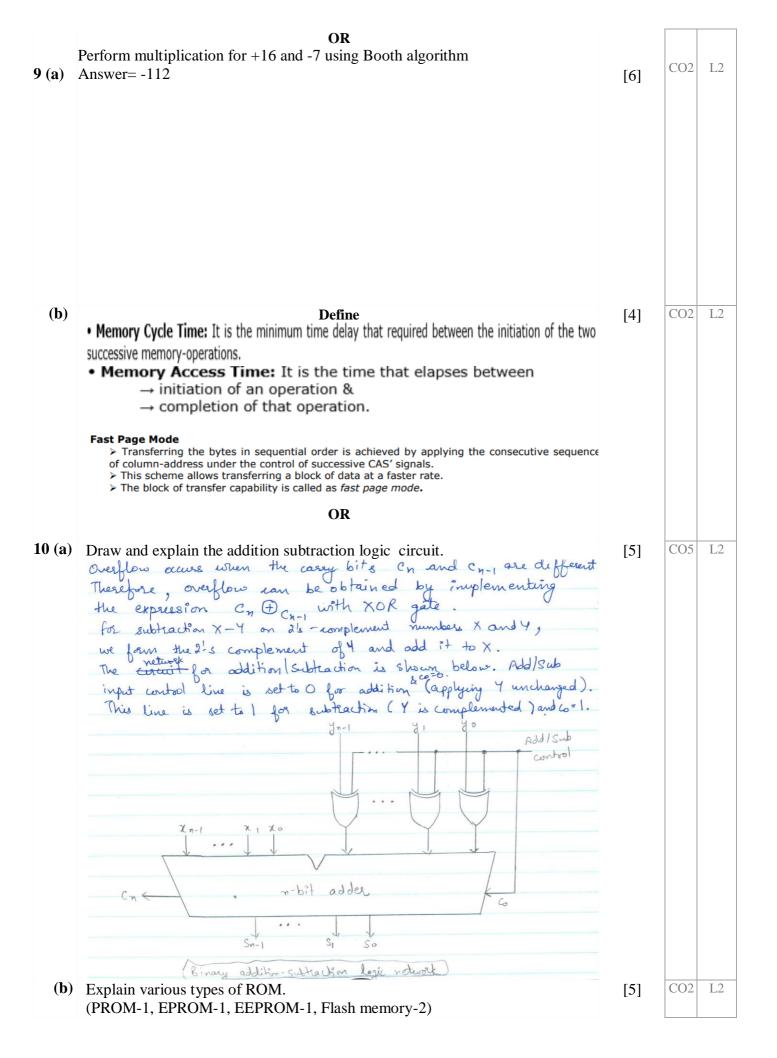

| The second secon | Clock  Clock  Address  Command  Data  Slave-ready |             | 1           |                                           |               | release 1 |  |