| USN |  |  |  |  |  |

|-----|--|--|--|--|--|

Improvement Test - Nov. 2018

| G 1   | G O                                                               |                                                                                 | 1111           | ordeniem re                           | <u>st 1</u> |                | 170004   | D 1     | GGE |     |     |

|-------|-------------------------------------------------------------------|---------------------------------------------------------------------------------|----------------|---------------------------------------|-------------|----------------|----------|---------|-----|-----|-----|

| Sub:  | Computer O                                                        |                                                                                 |                |                                       |             | Sub Code:      | 17CS34   | Branch: | CSE |     |     |

| Date: |                                                                   | 22/11/2018   Duration:   90 mins   Max Marks:   50   Sem/Sec:   3 (A,B,C)       |                |                                       |             |                |          | OE      |     |     |     |

|       | Answer FOUR                                                       | FULL question:                                                                  | s selecting A  | AT LEAST ONE                          | questi      | on FROM E      | ACH PART | MA      | RKS | СО  | RBT |

| 1 (a) | following ins                                                     | tructions:                                                                      | -              | PART A equired for sin on whose addre |             |                |          |         | 10] |     |     |

|       | 2. Zout, PCin,<br>3. MDRout, II<br>4. PCout, MA<br>5. Zout, PCin, | Rin<br>Rin, Read, Se<br>WMFC<br>MARin, Read,<br>MARin, Read<br>WMFC<br>Add, Zin | lect4, Add     |                                       |             |                |          |         |     | CO3 | L3  |

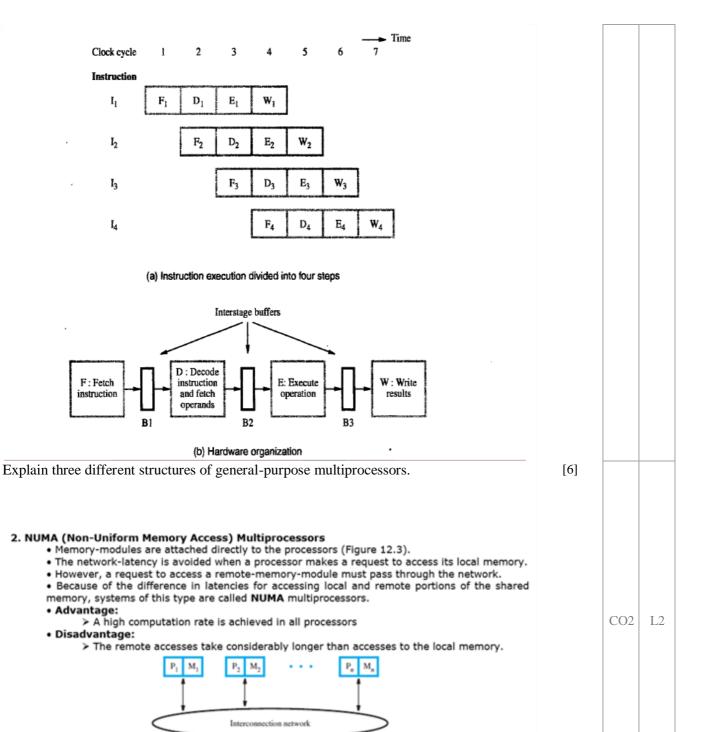

| 2 (a) | Brief note on                                                     | basic concept                                                                   | I <sub>1</sub> | Interstage                            | execution   | Execution unit | Time     |         | [4] | CO4 | L2  |

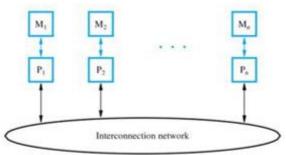

Figure 12.3 A NUMA multiprocessor.

(b)

# 1. UMA (Uniform Memory Access) Multiprocessor

- An interconnection-network permits n processors to access k memories (Figure 12.2).

- Thus, any of the processors can access any of the memories.

- The interconnection-network may introduce network-delay between

- 1) Processor &

- 2) Memory.

- A system which has the same network-latency for all accesses from the processors to the memory-modules is called a UMA Multiprocessor.

- · Although the latency is uniform, it may be large for a network that connects

- → many processors &

- → many memory-modules.

- For better performance, it is desirable to place a memory-module close to each processor.

- Disadvantage:

- > Interconnection-networks with very short delays are costly and complex to implement.

Figure 12.2 A UMA multiprocessor.

# 3. Distributed Memory Systems

- All memory-modules serve as private memories for processors that are directly connected to them.

- A processor cannot access a remote-memory without the cooperation of the remote processor.

- This cooperation takes place in the form of messages exchanged by the processors.

- Such systems are often called Distributed-Memory Systems (Figure 12.4).

Figure 12.4 A distributed memory system.

# PART B

3 (a) With a figure, explain single bus organization of datapath inside a processor.

[10]

CO3 L2

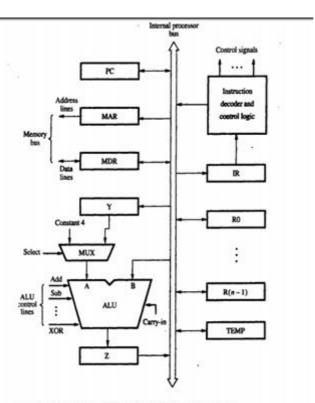

Figure 7.1 Single-bus organization of the datapath inside a processor.

### SINGLE BUS ORGANIZATION

- . ALU and all the registers are interconnected via a Single Common Bus (Figure 7.1).

- . Data & address lines of the external memory-bus is connected to the internal processor-bus via MDI & MAR respectively. (MDR $\rightarrow$  Memory Data Register, MAR  $\rightarrow$  Memory Address Register).

- . MDR has 2 inputs and 2 outputs. Data may be loaded

- → into MDR either from memory-bus (external) or

- → from processor-bus (internal).

- . MAR's input is connected to internal-bus;

MAR's output is connected to external-bus.

- . Instruction Decoder & Control Unit is responsible for

- → issuing the control-signals to all the units inside the processor.

- → implementing the actions specified by the instruction (loaded in the IR).

- Register R0 through R(n-1) are the Processor Registers.

The programmer can access these registers for general-purpose use.

- . Only processor can access 3 registers Y, Z & Temp for temporary storage during program-execution The programmer cannot access these 3 registers.

- 1) 'A' input gets the operand from the output of the multiplexer (MUX). · In ALU,

- 2) 'B' input gets the operand directly from the processor-bus.

- . There are 2 options provided for 'A' input of the ALU.

- . MUX is used to select one of the 2 inputs.

- · MUX selects either

- → output of Y or

- → constant-value 4( which is used to increment PC content).

- · An instruction is executed by performing one or more of the following operations:

- 1) Transfer a word of data from one register to another or to the ALU.

- 2) Perform arithmetic or a logic operation and store the result in a register.

- Fetch the contents of a given memory-location and load them into a register.

- 4) Store a word of data from a register into a given memory-location.

- . Disadvantage: Only one data-word can be transferred over the bus in a clock cycle. Solution: Provide multiple internal-paths. Multiple paths allow several data-transfers to take place in parallel.

OR

4 (a) Explain the differences between Hardwired and Micro-programmed control with neat [10] diagram.

CO3 L2

| Attribute                                                        | Hardwired Control                                                                                                                                    | Microprogrammed Control                                                                                                                                      |  |  |  |  |  |

|------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Definition                                                       | Hardwired control is a control<br>mechanism to generate control-<br>signals by using gates, flip-<br>flops, decoders, and other<br>digital circuits. | Micro programmed control is a control mechanism to generate control-signals by using a memory called control store (CS), which contains the control-signals. |  |  |  |  |  |

| Speed                                                            | Fast                                                                                                                                                 | Slow                                                                                                                                                         |  |  |  |  |  |

| Control functions                                                | Implemented in hardware.                                                                                                                             | Implemented in software.                                                                                                                                     |  |  |  |  |  |

| Flexibility                                                      | Not flexible to accommodate<br>new system specifications or<br>new instructions.                                                                     | More flexible, to accommodate new<br>system specification or new instructions<br>redesign is required.                                                       |  |  |  |  |  |

| Ability to handle large<br>or complex instruction<br>sets        | Difficult.                                                                                                                                           | Easier.                                                                                                                                                      |  |  |  |  |  |

| Ability to support<br>operating systems &<br>diagnostic features | Very difficult.                                                                                                                                      | Easy.                                                                                                                                                        |  |  |  |  |  |

| Design process                                                   | Complicated.                                                                                                                                         | Orderly and systematic.                                                                                                                                      |  |  |  |  |  |

| Applications                                                     | Mostly RISC microprocessors.                                                                                                                         | Mainframes, some microprocessors.                                                                                                                            |  |  |  |  |  |

| Instructionset size                                              | Usually under 100 instructions.                                                                                                                      | Usually over 100 instructions.                                                                                                                               |  |  |  |  |  |

| ROM size                                                         | -                                                                                                                                                    | 2K to 10K by 20-400 bit microinstructions.                                                                                                                   |  |  |  |  |  |

| Chip area efficiency                                             | Uses least area.                                                                                                                                     | Uses more area.                                                                                                                                              |  |  |  |  |  |

$\frac{\textbf{PART C}}{\textbf{5 (a)}} \quad \text{Explain the organization of Microwave oven with a neat block diagram}.$

[10]

CO4 L2

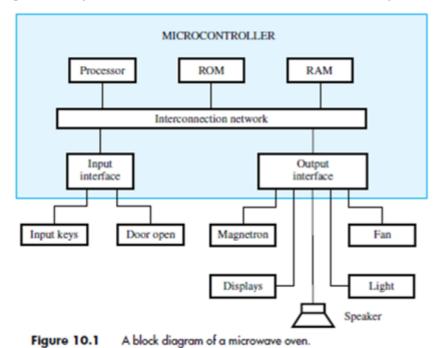

### MICROWAVE OVEN

- Microwave-oven is one of the examples of embedded-system.

- · This appliance is based on magnetron power-unit that generates the microwaves used to heat food

- . When turned-on, the magnetron generates its maximum power-output.

Lower power-levels can be obtained by turning the magnetron on & off for controlled time-interval:

- Cooking Options include:

- → Manual selection of the power-level and cooking-time.

- → Manual selection of the sequence of different cooking-steps.

- → Automatic melting of food by specifying the weight.

- . Display (or Monitor) can show following information:

- · Time-of-day clock.

- → Decrementing clock-timer while cooking.

- → Information-messages to the user.

- I/O Capabilities include:

- → Input-keys that comprise a 0 to 9 number pad.

- → Function-keys such as Start, Stop, Reset, Power-level etc.

- → Visual output in the form of a LCD.

- -> Small speaker that produces the beep-tone.

- Computational Tasks executed are:

- → Maintaining the time-of-day clock.

- → Determining the actions needed for the various cooking-options.

- → Generating the control-signals needed to turn on/off devices.

- → Generating display information.

- Non-volatile ROM is used to store the program required to implement the desired actions. So, the program will not be lost when the power is turned off (Figure 10.1).

- · Most important requirement: The microcontroller must have sufficient I/O capability.

Parallel I/O Ports are used for dealing with the external I/O signals.

Basic I/O Interfaces are used to connect to the rest of the system.

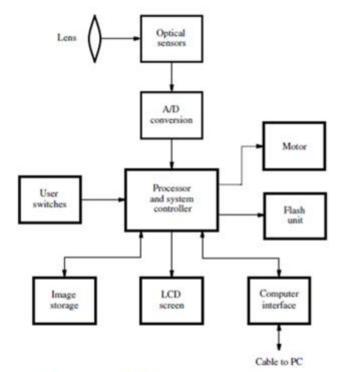

[10] 6 (a) Briefly block diagram of digital explain the camera.

Figure 10.2 A simplified block diagram of a digital camera.

- Digital Camera is one of the examples of embedded system.

- An array of Optical Sensors is used to capture images (Figure 10.2).

- The optical-sensors convert light into electrical charge.

CO4

L2

· Each sensing-element generates a charge that corresponds to one pixel.

One pixel is one point of a pictorial image.

- The number of pixels determines the quality of pictures that can be recorded & displayed.

- ADC is used to convert the charge which is an analog quantity into a digital representation.

- Processor

- → manages the operation of the camera.

- → processes the raw image-data obtained from the ADCs to generate images.

- The images are represented in standard-formats, so that they are suitable for use in computers.

- · Two standard-formats are:

- 1) TIFF is used for uncompressed images &

- 2) JPEG is used for compressed images.

- The processed-images are stored in a larger storage-device. For ex: Flash memory cards.

- A captured & processed image can be displayed on a LCD screen of camera.

- The number of saved-images depends on the size of the storage-unit.

- Typically, USB Cable is used for transferring the images from camera to the computer.

- . System Controller generates the signals needed to control the operation of

- i) Focusing mechanism and

- ii) Flash unit.

(ADC → Analog-to-digital converter, LCD → liquid-crystal display)

(TIFF → Tagged Image File Format, JPEG → Joint Photographic Experts Group)

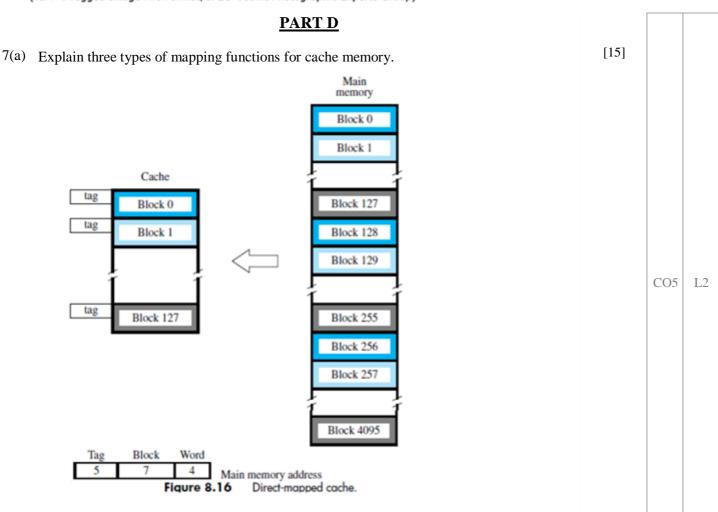

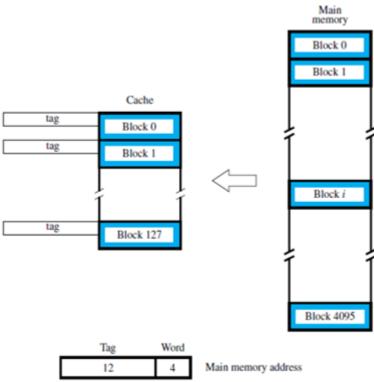

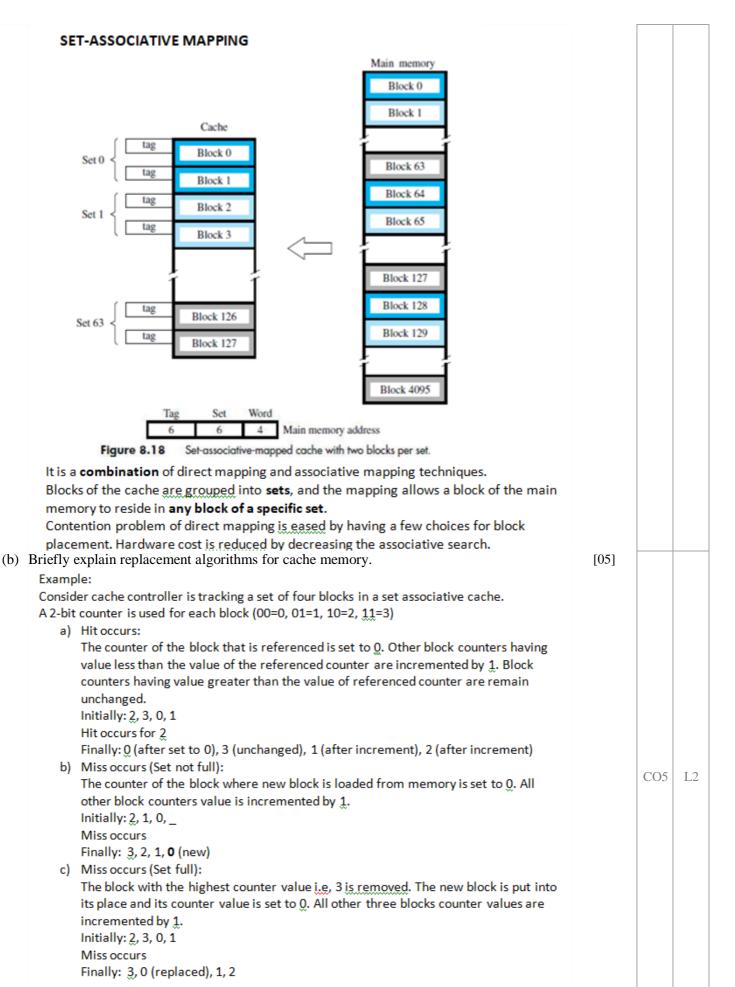

# **DIRECT MAPPING**

This technique is easy to implement but not very flexible.

Block j of the main memory maps onto j modulo 128 of the cache. For example, whenever **one of** the main memory blocks 0, 128, 256, .... Is loaded in the cache, it is stored in cache block 0. Main memory blocks 1, 129, 257, .... are stored in cache block 1 (one at a time), and so on. Contention may occur for a single cache block required by multiple memory blocks. E.g when for program execution both memory block 1 and 129 are required but cache block 1 can only store one memory block. To resolve this, new blocks are allowed to overwrite the currently resident block.

From example,

4096 memory blocks need to be mapped to 128 cache blocks. i.e, each cache block identified 32 memory blocks (4096/128).

# Main memory address is divided into three parts:

Tag (5 bits): identify which memory block (out of 32 in this case) is currently resident in the cache

Block (7 bits): cache block position where the new memory block must be stored

**Word** (4 bits): selects one of the words of the memory block (out of 16 words per block in this case)

## ASSOCIATIVE MAPPING

Figure 8.17 Associative-mapped cache.

- It is more flexible than direct mapping technique but more expensive. Main memory block can be placed into any cache block position.

- Memory address is divided into two fields:

- Low order 4 bits identify the memory word within a block.

- High order 12 bits or tag bits identify a memory block when residing in the cache.

- · Flexible, and uses cache space efficiently.

- Replacement algorithms can be used to replace an existing block in the cache when the cache is full.

- Cost is higher than direct-mapped cache because of the need to search all 128

patterns to determine whether a given block is in the cache.

OR

[12]

Techniques that automatically move program and data between main memory and secondary storage when they are required for execution are called virtual-memory techniques.

binary addresses generated by processor are called logical or virtual addresses.

The virtual-address is translated into physical-address by MMU (Memory Management Unit).

• During every memory-cycle, MMU determines whether the addressed-word is in the memory. If the word is in memory.

Then, the word is accessed and execution proceeds.

Otherwise, a page containing desired word is transferred from disk to memory.

• Using DMA scheme, transfer of data between disk and memory is performed.

Figure 8.24 Virtual memory organization.

Program and data are composed of fixed-length units called pages.

A page consists of a block of words that occupy contiguous locations in the main memory.

Each virtual or logical address generated by a processor is interpreted as a virtual page number (high-order bits) plus an offset (low-order bits) that specifies the location of a particular byte within that page.

Information about the main memory location of each page is kept in the page table.

Main memory address where the page is stored.

Current status of the page.

Area of the main memory that can hold a page is called as page frame.

Starting address of the page table is kept in a page table base register.

Virtual page number generated by the processor is added to the contents of the page table base register.

This provides the address of the corresponding entry in the page table.

The contents of this location in the page table give the starting address of the page if the page is currently in the main memory.

Page table entry for a page also includes some control bits which describe the status of the page while it is in the main memory.

One bit indicates the validity of the page.

One bit indicates whether the page has been modified during its residency in the main memory.

Other control bits for various other types of restrictions that may be imposed.

CO<sub>2</sub> L2

Figure 8.25 Virtual-memory address translation.

The Page-table is placed in the memory but a copy of small portion of the page-table is located within MMU. This small portion is called TLB (Translation LookAside Buffer).

TLB consists of the page-table entries that corresponds to the most recently accessed pages.

TLB also contains the virtual-address of the entry.

High-order bits of the virtual address generated by the processor select the virtual page.

These bits are compared to the virtual page numbers in the TLB.

If there is a match, a hit occurs and the corresponding address of the page frame is read.

If there is no match, a miss occurs and the page table within the main memory must be consulted.

If a program generates an access to a page that is not in the main memory, In this case, a page fault is said to occur.

Upon detecting a page fault by the MMU, following actions occur:

MMU asks the operating system to intervene by raising an exception.

Processing of the active task which caused the page fault is interrupted.

Control is transferred to the operating system.

Operating system copies the requested page from secondary storage to the main memory.

Once the page is copied, control is returned to the task which was interrupted.

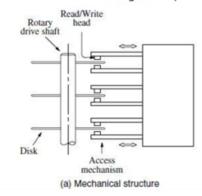

(b) Explain secondary storage of magnetic disk.

[8]

CO2 L2

- Magnetic Disk system consists of one or more disk mounted on a common spindle.

- A thin magnetic film is deposited on each disk (Figure 8.27).

- Disk is placed in a rotary-drive so that magnetized surfaces move in close proximity to R/W heads.

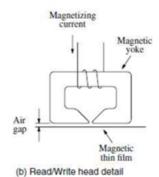

- Each R/W head consists of 1) Magnetic Yoke & 2) Magnetizing-Coil.

- Digital information is stored on magnetic film by applying current pulse to the magnetizing-coil.

- Only changes in the magnetic field under the head can be sensed during the Read-operation.

- Therefore, if the binary states 0 & 1 are represented by two opposite states,

then a voltage is induced in the head only at 0-1 and at 1-0 transition in the bit stream.

- A consecutive of 0's & 1's are determined by using the clock.

- . Manchester Encoding technique is used to combine the clocking information with data.