## Internal Assessment Test 1 – Oct. 2018

| Sub:  | Mechatronics                   |              |                            |                |        | Sub Code:  | 15ME754        | Branch: | ME  |     |     |

|-------|--------------------------------|--------------|----------------------------|----------------|--------|------------|----------------|---------|-----|-----|-----|

| Date: | 16/10/2018                     | Duration:    | 90 min's                   | Max Marks:     | 50     | Sem / Sec: | VII            | A&B     |     | OF  | BE  |

|       |                                | <u>A</u>     | nswer any FI               | VE FULL Questi | ons    |            |                | MA      | RKS | СО  | RBT |

|       | Explain the fo                 | Č            | hnology rel<br>. Address b | 1              |        |            |                | [       | 10] | CO3 | L2  |

|       | I. KAWI II.                    | ALU III      | . Address b                | us IV. Peter   | L CyC. | ic.        |                |         |     |     |     |

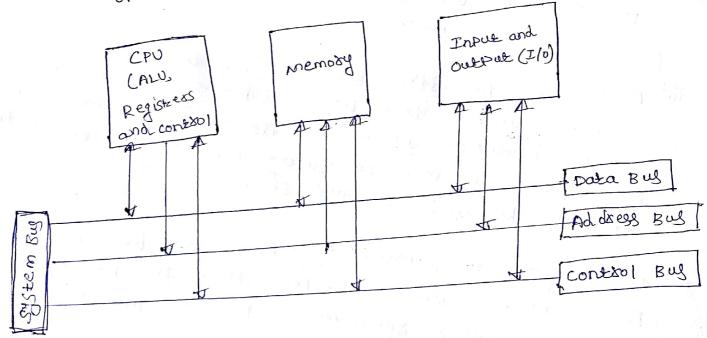

| 2     | With the help the functions of |              | 1                          |                |        | a micropro | cessor and sta | ite [   | 10] | CO3 | L2  |

| 3     | Write i. shor                  | t notes on r | egisters use               | ed in 8085 mic | ropr   | ocessor.   |                | [       | 10] | CO3 | L2  |

|       | ii. diffe                      | rence betwe  | een micropi                | cocessor and n | nicro  | controller |                |         |     |     |     |

| USN | 1 | C | R | M | Е |  |  |  |

|-----|---|---|---|---|---|--|--|--|

## Internal Assessment Test 2 – Oct. 2018

| Sub:                                                                                                                                    | Mechatronics                                                   |             |              |                |       | Sub Code:  | 15ME754 | Bran | ch: | ME  |     |     |

|-----------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|-------------|--------------|----------------|-------|------------|---------|------|-----|-----|-----|-----|

| Date:                                                                                                                                   | 16/10/2018                                                     | Duration:   | 90 min's     | Max Marks:     | 50    | Sem / Sec: | VII     | A&B  |     |     | OE  | BE  |

|                                                                                                                                         |                                                                | <u>A</u>    | nswer any FI | VE FULL Questi | ions  |            |         |      | MA  | RKS | СО  | RBT |

| 1                                                                                                                                       | Explain the fo                                                 | llowing tec | hnology rel  | ated micropro  | cesso | or:        |         |      | [1  | .0] | CO3 | L2  |

|                                                                                                                                         | i. RAM ii.                                                     | ALU iii     | . Address b  | us iv. Fetch   | cyc]  | le.        |         |      |     |     |     |     |

| With the help of neat sketch explain the architecture of a microprocessor and state the functions of each element of the microprocessor |                                                                |             |              |                | ite   | [1         | 0]      | CO3  | L2  |     |     |     |

| 3                                                                                                                                       | Write i. short notes on registers used in 8085 microprocessor. |             |              |                |       |            |         | [1   | 0]  | CO3 | L2  |     |

| ii. difference between microprocessor and microcontroller                                                                               |                                                                |             |              |                |       |            |         |      |     |     |     |     |

| USN | 1 | C | R | M | Е |  |  |  |

|-----|---|---|---|---|---|--|--|--|

## Internal Assessment Test 2 – Oct. 2018

| Sub:  | Mechatronics                      |              |              |                |       | Sub Code:  | 15ME754        | Branch: | ME   |     |      |

|-------|-----------------------------------|--------------|--------------|----------------|-------|------------|----------------|---------|------|-----|------|

| Date: | 16/10/2018                        | Duration:    | 90 min's     | Max Marks:     | 50    | Sem / Sec: | VII            | A&B     |      | OF  | BE . |

|       |                                   | <u>A</u>     | nswer any FI | VE FULL Questi | ons   |            |                | MA      | ARKS | CO  | RBT  |

| 1     | Explain the fo                    | llowing tec  | hnology rel  | ated micropro  | cesso | or:        |                | I       | [10] | CO3 | L2   |

|       | i. RAM ii.                        | ALU iii      | . Address b  | ous iv. Fetch  | cyc   | le.        |                |         |      |     |      |

| 2     | With the help<br>the functions of |              | -            |                |       | a micropro | cessor and sta | ite [   | 10]  | CO3 | L2   |

| 3     | Write i. shor                     | t notes on 1 | egisters use | ed in 8085 mic | ropr  | ocessor.   |                | [       | 10]  | CO3 | L2   |

|       | ii. differ                        | ence betwe   | en micropr   | ocessor and m  | icroc | controller |                |         |      |     |      |

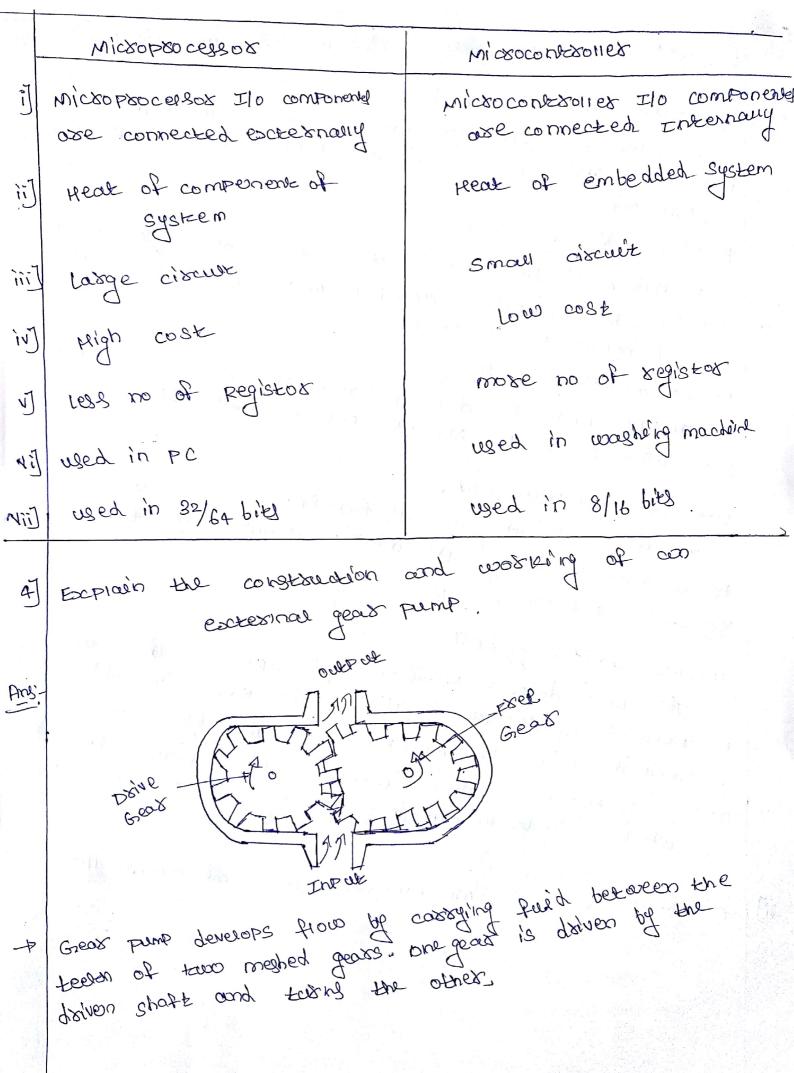

| 4 | Explain the construction and working of an external gear pump.                                  | [10] | CO4 | L2 |  |

|---|-------------------------------------------------------------------------------------------------|------|-----|----|--|

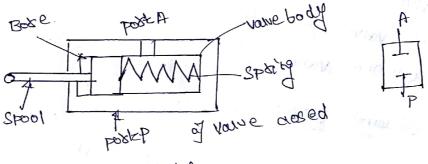

| 5 | List the types of pressure control valve and explain pressure reducing valve with neat diagram. | [10] | CO4 | L2 |  |

| 6 | Sketch and explain types of sliding spool valve.                                                | [10] | CO4 | L2 |  |

| 7 | Design a hydraulic circuit for controlling a double acting hydraulic cylinder.                  | [10] | CO4 | L3 |  |

CI CCI HOD

| 4 | Explain the construction and working of an external gear pump.                                  | [10] | CO4 | L2 |  |

|---|-------------------------------------------------------------------------------------------------|------|-----|----|--|

| 5 | List the types of pressure control valve and explain pressure reducing valve with neat diagram. | [10] | CO4 | L2 |  |

| 6 | Sketch and explain types of sliding spool valve.                                                | [10] | CO4 | L2 |  |

| 7 | Design a hydraulic circuit for controlling a double acting hydraulic cylinder.                  | [10] | CO4 | L3 |  |

CI CCI HOD

| 4 | Explain the construction and working of an external gear pump.                                  | [10] | CO4 | L2 |

|---|-------------------------------------------------------------------------------------------------|------|-----|----|

| 5 | List the types of pressure control valve and explain pressure reducing valve with neat diagram. | [10] | CO4 | L2 |

| 6 | Sketch and explain types of sliding spool valve.                                                | [10] | CO4 | L2 |

| 7 | Design a hydraulic circuit for controlling a double acting hydraulic cylinder.                  | [10] | CO4 | L3 |

CI CCI HOD

RAM: Random - access memory is a form of computer data storage that stores data and machine code currently being used. A random - access memory device allows data items to be read or written in almost the sand amount of the irrespective of the physical pocation of data inside the memory.

ALU :- Axithmetic rogic unit is a combinational digital electronic circuit that pexforms axithmetic and biturise operations on integer binary numbers. This is in contract to a froating-point unit, which operates on floating points numbers.

Address Bus: An address bus is a computer bus architecture used to transfer data between devices that are identified by the hordware address of the physical memory, which is storied in the form of binary numbers to enable the data bus to access memory storage.

Fetch cycle: The instruction cycle is the basic operational process of a computer system. It is the process by which a computer retrievel, a program instruction from its memory.

o microprocessor and State the functions of each exemplation of each exemplations of the microprocessor.

il 16-bit program counter which contains the memory address ii) The 16-bit Stack pointer to maintain a pughdown stack and

iii) six 8-bit registers designated as B, c, D, E, 14& L which can be used individually or in pairs. The permitted pairs are

iv] 8- bit accumulator register in which asways one of the

v) rive 1-bit flags namely coxisy (cy), zero (z), sign (s), pasity(x) and Auxiliary cassy (Ac)

vi) Two temposary xegisters which are not program addressable and are used only for interinde executain of instauctions

il short notes on registers used in 8085 micro processor.

أأ

Immediate addressing mode

In this mode, the 8/16-bit data is specified in the instruction itself as one of its operand for example;

Registed addressing mode

In the's mode the data is copied from one register to another. For example: MOV K, B: means daka is register B is copied to registeric.

In this mode the data is discording copied from the Disect addressing mode given address to the register. For example LDB socole;

In this mode, the data is thankt exed from one register Indisect addsessing mode to another by using the address pointed by the REDISTER LOR EXC: WON K

This mode doesn't seawise any operand; the data Implied add selsing mode is specified by the opcode itself. Here effectaive address is calculated by the milestopsocossos. This type of addressing rearrisses several accesses to retrieve the data which is to be roaded into the register for ex; CMP.

Difference between microprocessor and micro antroller.

The second type of value is Pressure reducing value. This type of value (which of normally open) is used to maintain the reduced programes in specified locations of hydramic system. It is actuated by downstream pressure and tends to chose as i'th pressure reacher the arm tends to chose as i'th pressure reacher the value setting. Schematic diagram of pressure reducery have setting. Schematic diagram of pressure reducery

A pressure reducing value uses a spring loaded spool to contratol the downstream pressure if the downstream pressure is below the value secting. The fluid is flow press are is below the value output.

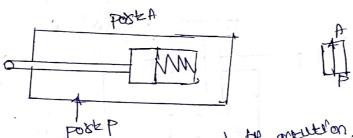

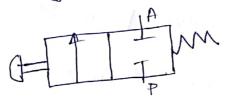

sicerch and explain types of suiding spool valve

[3

Arg:

The simplet spool type of directional control value is chear value with is two way value because it control to two open value because it control is two way value because it control is two way value because it control to two pasts. This value are also called , two way value with its value are also called , two walls. Value are always closed values. Value are usually actuated by Priot (thy drawle they are usually actuated by Priot (thy drawle actuated in manual as the value is an isolonoid actuated.

which is free. The pumping chambers formed between the gear teeth are enclosed by the purity housing and the side plates. A 1000 pressure region is areaked at the intel as the gear teeth separate. As a regult quid proces in and is cassied asound by the goals. As the teeth megh again at the outlet high pressare is created and the finish is forced out. shows the constanction of a typical external gear pump. The types of pressure control value are: 5 pressure reducing value II variabling value countesbalance voive Pressure seavence valve 间 Toi pressure Reducing valve; B Programe E Down Spool + constant beginne ant - conexol signal

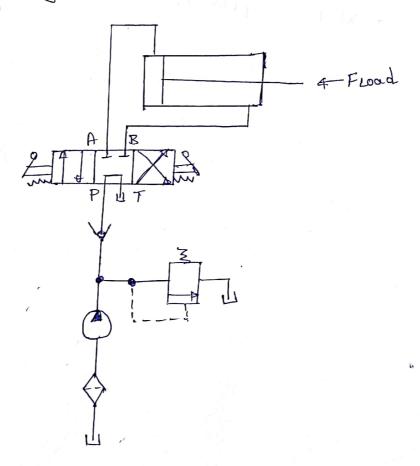

Design a hydraunic circuit for controlling a doubt e

the cylinder is highsaulically locked and the pump is unloaded back to the tank.

Is unloaded back to the tank.

When the 4/3 valve is actuated into the flow path the cylinder is extended against its load as oil the cylinder is extended against its load as oil in the sod end flows from port P through port A. oil in the sod end flows from port P through port A. oil in the sod end through the cylinder is free to flow back to the tank of the cylinder is free to flow back to through through the footh.

Through the flow way valve from port B through from configuration, the cylinder setroacts as oil flows from port P through port B. oil in the bloome end is port P through port B. oil in the bloome end is port P through port B. oil in the bloom path from seturned to the tank Via the flow Poth from