Internal Assessment Test 1 – Sept. 2018 Solution

|  |           |          |            |    | Sub Code:  | V   | Branch: | ECE | A,B |

|--|-----------|----------|------------|----|------------|-----|---------|-----|-----|

|  | Duration: | 90 min's | Max Marks: | 50 | Sem / Sec: | A,B |         | OBE |     |

# 1. Explain briefly the design flow for design VLSI circuits. [10]

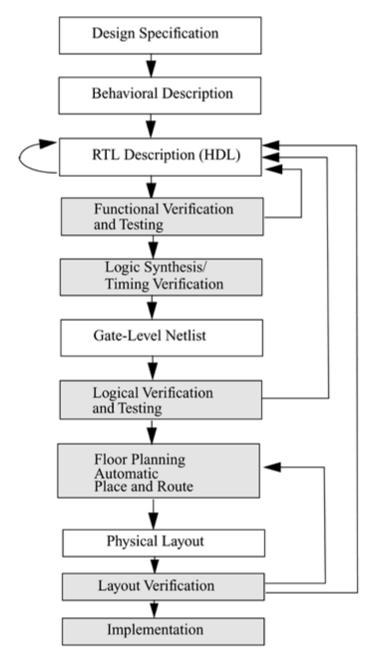

The design flow shown in Figure 1-1 is typically used by designers who use HDLs. In any design, specifications are written first. Specifications describe abstractly the functionality, interface, and overall architecture of the digital circuit to be designed. At this point, the architects do not need to think about how they will implement this circuit. A behavioral description is then created to analyze the design in terms of functionality, performance, compliance to standards, and other high-level issues. Behavioral descriptions are often written with HDLs. New EDA tools have emerged to simulate behavioral descriptions of circuits. These tools combine the powerful concepts from HDLs and object oriented languages such as C++. These tools can be used instead of writing behavioral

descriptions in Verilog HDL. The behavioral description is manually converted to an RTL description in an HDL. The designer has to describe the data flow that will implement the desired digital circuit. From this point onward, the design process is done with the assistance of EDA tools. Logic synthesis tools convert the RTL description to a gate-level netlist. A gate-level netlist is a description of the circuit in terms of gates and connections between them. Logic synthesis tools ensure that the gate-level netlist meets timing, area, and power specifications. The gate-level netlist is input to an Automatic Place and Route tool, which creates a layout. The layout is verified and then fabricated on a chip. Thus, most digital design activity is concentrated on manually optimizing the RTL description of the circuit. After the RTL description is frozen, EDA tools are available to assist the designer in further processes. Designing at the RTL level has shrunk the design cycle times from years to a few months. It is also possible to do many design iterations in a short period of time. Behavioral synthesis tools have begun to emerge recently. These tools can create RTL descriptions from a behavioral or algorithmic description of the circuit. As these tools mature, digital circuit design will become similar to high-level computer programming. Designers will simply implement the algorithm in an HDL at a very abstract level. EDA tools will help the designer convert the behavioral description to a final IC chip. It is important to note that, although EDA tools are available to automate the processes and cut design cycle times, the designer is still the person who controls how the tool will perform. EDA tools are also susceptible to the "GIGO: Garbage In Garbage Out" phenomenon. If used improperly, EDA tools will lead to inefficient designs. Thus, the designer still needs to understand the nuances of design methodologies, using EDA tools to obtain an optimized design.

# 2 (a) Explain the 4bit ripple carry counter with block diagram using top down design hierarchy.

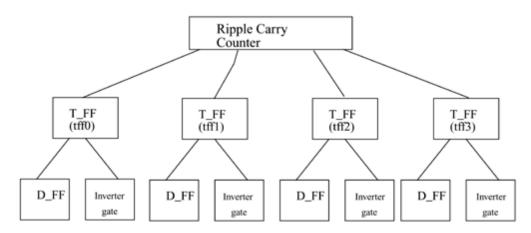

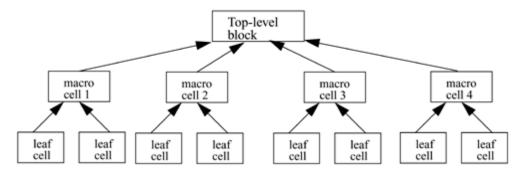

There are two basic types of digital design methodologies: a top-down design methodology and a bottom-up design methodology. In a top-down design methodology, we define the top-level block and identify the sub-blocks necessary to build the top-level block. We further subdivide the sub-blocks until we come to leaf cells, which are the cells that cannot further be divided. Above figureshows the top-down design process.

| reset | $q_n$ | q <sub>n+1</sub> |

|-------|-------|------------------|

| 1     | 1     | 0                |

| 1     | 0     | 0                |

| 0     | 0     | 1                |

| 0     | 1     | 0                |

| 0     | 0     | 0                |

|       |       |                  |

## 3 (a) What is instance? Explain module instantiation with an example.

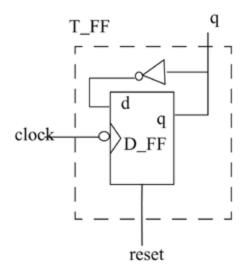

A module provides a template from which you can create actual objects. When a module is invoked, Verilog creates a unique object from the template. Each object has its own name, variables, parameters, and I/O interface. The process of creating objects from a module template is called instantiation, and the objects are called instances. In yhe following example, the top-level block creates four instances from the T-flipflop (T\_FF) template. Each T\_FF instantiates a D\_FF and an inverter gate. Each instance must be given a unique name. Note that // is used to denote single-line comments.

```

module ripple_carry_counter(q, clk, reset);

output [3:0] q; //I/O signals and vector declarations

//will be explained later.

input clk, reset; //I/O signals will be explained later.

//Four instances of the module T_FF are created. Each has a unique

//name.Each instance is passed a set of signals. Notice, that

//each instance is a copy of the module T_FF.

T_FF tff0(q[0],clk, reset);

T_FF tff1(q[1],q[0], reset);

T_FF tff2(q[2],q[1], reset);

T_FF tff3(q[3],q[2], reset);

endmodule

```

3(b) The speed and complexity of digital circuits have increased rapidly. Designers have responded by designing at higher levels of abstraction. Designers have to think only in terms of functionality. EDA tools take care of the implementation details. With designer assistance, EDA tools have become sophisticated enough to achieve a close-to-optimum implementation.

The most popular trend currently is to design in HDL at an RTL level, because logic synthesis tools can create gate-level netlists from RTL level design. Behavioral synthesis allowed engineers to design directly in terms of algorithms and the behavior of the circuit, and then use EDA tools to do the translation and optimization in each phase of the design. However, behavioral synthesis did not gain widespread acceptance. Today, RTL design continues to be very popular. Verilog HDL is also being constantly enhanced to meet the needs of new verification methodologies.

Formal verification and assertion checking techniques have emerged. Formal verification applies formal mathematical techniques to verify the correctness of Verilog HDL descriptions and to establish equivalency between RTL and gate-level netlists. However,

the need to describe a design in Verilog HDL will not go away. Assertion checkers allow checking to be embedded in the RTL code. This is a convenient way to do checking in the most important parts of a design.

New verification languages have also gained rapid acceptance. These languages combine the parallelism and hardware constructs from HDLs with the object oriented nature of C++. These languages also provide support for automatic stimulus creation, checking, and coverage. However, these languages do not replace Verilog HDL. They simply boost the productivity of the verification process. Verilog HDL is still needed to describe the design.

For very high-speed and timing-critical circuits like microprocessors, the gate-level netlist provided by logic synthesis tools is not optimal. In such cases, designers often mix gate-level description directly into the RTL description to achieve optimum results. This practice is opposite to the high-level design paradigm, yet it is frequently used for highspeed designs because designers need to squeeze the last bit of timing out of circuits, and EDA tools sometimes prove to be insufficient to achieve the desired results.

4)

7(a)Explain lexical conventions used in Verilog.

# Whitespace

Blank spaces (\b), tabs (\t) and newlines (\n) comprise the whitespace. Whitespace is ignored by Verilog except when it separates tokens. Whitespace is not ignored in strings. 42

# 3.1.2 Comments

Comments can be inserted in the code for readability and documentation. There are two ways to write comments. A one-line comment starts with "//". Verilog skips from that point to the end of line. A multiple-line comment starts with "/\*" and ends with "\*/". Multiple-line comments cannot be nested. However, one-line comments can be embedded in multiple-line comments.

```

a = b && c; // This is a one-line comment

/* This is a multiple line

comment */

/* This is /* an illegal */ comment */

/* This is //a legal comment */

```

## 3.1.3 Operators

Operators are of three types: unary, binary, and ternary. Unary operators precede the operand. Binary operators appear between two operands. Ternary operators have two separate operators that separate three operands.

```

a = \sim b; // \sim is a unary operator. b is the operand a = b \&\& c; // \&\& is a binary operator. b and c are operands a = b? c : d; //?: is a ternary operator. b, c and d are operands

```

# **3.1.4 Number Specification**

There are two types of number specification in Verilog: sized and unsized. **Sized numbers**

Sized numbers are represented as <size> '<base format> <number>.

<size> is written only in decimal and specifies the number of bits in the number. Legal base formats are decimal ('d or 'D), hexadecimal ('h or 'H), binary ('b or 'B) and octal ('o or 'O). The number is specified as consecutive digits from 0, 1, 2, 3, 4, 5, 6, 7, 8, 9, a, b, c, d, e, f. Only a subset of these digits is legal for a particular base. Uppercase letters are legal for number specification.

```

4'b1111 // This is a 4-bit binary number 12'habc // This is a 12-bit hexadecimal number 16'd255 // This is a 16-bit decimal number. 43

```

#### **Unsized numbers**

Numbers that are specified without a <base format> specification are decimal numbers by default. Numbers that are written without a <size> specification have a default number of bits that is simulator- and machine-specific (must be at least 32).

```

23456 // This is a 32-bit decimal number by default 'hc3 // This is a 32-bit hexadecimal number 'o21 // This is a 32-bit octal number

```

#### X or Z values

Verilog has two symbols for unknown and high impedance values. These values are very important for modeling real circuits. An unknown value is denoted by an x. A high impedance value is denoted by z.

```

12'h13x // This is a 12-bit hex number; 4 least significant bits unknown 6'hx // This is a 6-bit hex number 32'bz // This is a 32-bit high impedance number

```

An x or z sets four bits for a number in the hexadecimal base, three bits for a number in the octal base, and one bit for a number in the binary base. If the most significant bit of a number is 0, x, or z, the number is automatically extended to fill the most significant bits, respectively, with 0, x, or z. This makes it easy to assign x or z to whole vector. If the most significant digit is 1, then it is also zero extended.

### **Negative numbers**

Negative numbers can be specified by putting a minus sign before the size for a constant number. Size constants are always positive. It is illegal to have a minus sign between <br/>base format> and <number>. An optional signed specifier can be added for signed arithmetic.

```

-6'd3 // 8-bit negative number stored as 2's complement of 3 -6'sd3 // Used for performing signed integer math 4'd-2 // Illegal specification

```

#### **Underscore characters and question marks**

An underscore character "\_" is allowed anywhere in a number except the first character. Underscore characters are allowed only to improve readability of numbers and are ignored by Verilog.

7(b)Explain following data types

i)Register ii)Nets iii)Vectors

## Nets

Nets represent connections between hardware elements. Just as in real circuits, nets have values continuously driven on them by the outputs of devices that they are connected to. In Figure 3-1 net a is connected to the output of and gate g1. Net a will continuously assume the value computed at the output of gate g1, which is b & c.

### Figure 3-1. Example of Nets

Nets are declared primarily with the keyword wire. Nets are one-bit values by default unless they are declared explicitly as vectors. The terms wire and net are often used

interchangeably. The default value of a net is z (except the trireg net, which defaults to x ). Nets get the output value of their drivers. If a net has no driver, it gets the value z.

```

wire a; // Declare net a for the above circuit

wire b,c; // Declare two wires b,c for the above circuit

wire d = 1'b0; // Net d is fixed to logic value 0 at declaration.

```

Note that net is not a keyword but represents a class of data types such as wire, wand, wor, tri, triand, trior, trireg, etc.

# 3.2.3 Registers

Registers represent data storage elements. Registers retain value until another value is placed onto them. Do not confuse the term registers in Verilog with hardware registers built from edge-triggered flipflops in real circuits. In Verilog, the term register merely 47

means a variable that can hold a value. Unlike a net, a register does not need a driver. Verilog registers do not need a clock as hardware registers do. Values of registers can be changed anytime in a simulation by assigning a new value to the register.

Register data types are commonly declared by the keyword reg. .

# **Example 3-1 Example of Register**

```

reg reset; // declare a variable reset that can hold its value

initial // this construct will be discussed later

begin

reset = 1'b1; //initialize reset to 1 to reset the digital circuit.

#100 reset = 1'b0; // after 100 time units reset is deasserted.

end

```

Registers can also be declared as signed variables. Such registers can be used for signed arithmetic.reg signed [63:0] m; // 64 bit signed value integer i; // 32 bit signed value

#### 3.2.4 Vectors

Nets or reg data types can be declared as vectors (multiple bit widths). If bit width is not specified, the default is scalar (1-bit).

```

wire a; // scalar net variable, default

wire [7:0] bus; // 8-bit bus

wire [31:0] busA,busB,busC; // 3 buses of 32-bit width.

reg clock; // scalar register, default

reg [0:40] virtual_addr; // Vector register, virtual address 41 bits

wide

```

Vectors can be declared at [high#: low#] or [low#: high#], but the left number in the squared brackets is always the most significant bit of the vector. In the example shown above, bit 0 is the most significant bit of vector virtual addr

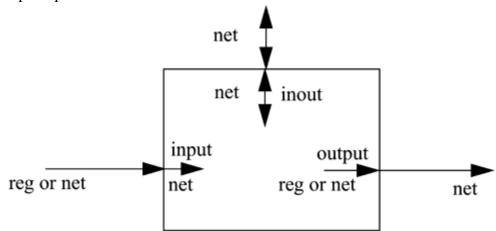

### 6a) Explain with a neat diagram components of module

A module definition always begins with the keyword module. The module name, port list, port declarations, and optional parameters must come first in a module definition. Port list and port declarations are present only if the module has any ports to interact with the external environment. The five components within a module are: variable declarations, dataflow statements, instantiation of lower modules, behavioral blocks, and tasks or functions. These components can be in any order and at any place in the module definition. The endmodule statement must always come last in a module definition. All components except module, module name, and endmodule are optional and can be mixed and matched as per design needs. Verilog allows multiple modules to be defined in a single file. The modules can be defined in any order in the file..

# 6 (b) Explain port connection rules.

One can visualize a port as consisting of two units, one unit that is internal to the module and another that is external to the module. The internal and external units are connected. There are rules governing port connections when modules are instantiated within other modules. The Verilog simulator complains if any port connection rules are violated.

connected to a variable which is a reg or a net.

## **Outputs**

Internally, outputs ports can be of the type reg or net. Externally, outputs must always be connected to a net. They cannot be connected to a reg.

#### **Inouts**

Internally, inout ports must always be of the type net. Externally, inout ports must always be connected to a net.

### Width matching

It is legal to connect internal and external items of different sizes when making intermodule port connections. However, a warning is typically issued that the widths do not match.

# **Unconnected ports**

Verilog allows ports to remain unconnected. For example, certain output ports might be simply for debugging, and you might not be interested in connecting them to the external signals. You can let a port remain unconnected by instantiating a module as shown below.

fulladd4 fa0(SUM, , A, B, C\_IN); // Output port c\_out is unconnected

```

5 (a) Write test bench program for 4bit Ripple carry counter.

```

```

module ripple_carry_counter(q, clk, reset);

output [3:0] q; //I/O signals and vector declarations

//will be explained later.

input clk, reset; //I/O signals will be explained later.

//Four instances of the module T FF are created. Each has a unique

//name.Each instance is passed a set of signals. Notice, that

//each instance is a copy of the module T FF.

T FF tff0(q[0],clk, reset);

T FF tff1(q[1],q[0], reset);

T_FF tff2(q[2],q[1], reset);

T_FF tff3(q[3],q[2], reset);

endmodule

// Define the module T FF. It instantiates a D-flipflop. We assumed

// that module D-flipflop is defined elsewhere in the design. Refer

// to Figure 2-4 for interconnections.

module T_FF(q, clk, reset);

//Declarations to be explained later

output q;

input clk, reset;

wire d;

D FF dff0(q, d, clk, reset); // Instantiate D FF. Call it dff0.

not n1(d, q); // not gate is a Verilog primitive. Explained later.

endmodule

```

## 5(b)Explain bottom up design hierarchy.

In a bottom-up design methodology, we first identify the building blocks that are available to us. We build bigger cells, using these building blocks. These cells are then used for higher-level blocks until we build the top-level block in the design.