Micro Controller is a Chip used in embedded Systems, Programmed for Specific applications. Its a byproduct of micro processor. So it has all the features of micro processor and added features such as memory, slo posts, counters of clock circuits.

1M

i)

| i)         | RISC                                        | 1,22 | CISC ·                                                          |

|------------|---------------------------------------------|------|-----------------------------------------------------------------|

| *          | Reduced Instruction Set<br>computing chip.  | *    | Complex Instruction Set Comput-ing chip.                        |

| *          | Simple Anstructions                         | *    | Ability to execute multi-step operations within one instruction |

| *          | No- of instructions per<br>program is high. | *    | No of unstructions per program is less.                         |

|            | Memory needed is high.                      | 1    | Less Memory needed                                              |

| <b>*</b> 1 | Ex: Apple, Microcontrollers                 | *    | Ex: Intel, Microprocessors, IBM                                 |

3M

ii )

|   | Missopoocessox            | Micro controlles            |

|---|---------------------------|-----------------------------|

| 7 |                           |                             |

|   | Heart of Computes Syctem  | · Heast of Embedded Systems |

|   | Its just a processor.     | · Mc has processor along    |

|   | Memory 4 I/o Components   | with internal memory        |

|   | have to be Connected      | & the components.           |

|   | externally                |                             |

|   | cimit becomes large       | · Compact                   |

|   | Porses Consumption is     | · Ilcs have power Baving    |

|   | ligh                      | modes like idle mode        |

|   | 3                         | 4 Power Saving made So      |

|   |                           | proves Consumption is low   |

| • | Since memory & I/o        | · Since Components are      |

|   | Components are all        | internal, speed is          |

|   | enternal each instruct    | fast -                      |

|   | will need enternal operat |                             |

|   | ion hence it is relati-   |                             |

|   | Vely Slower.              |                             |

| • | MP have less no a regist  | · Mer have more in a        |

| • | ers, hence more operation | - Registers hence           |

|   | ons are memory based      |                             |

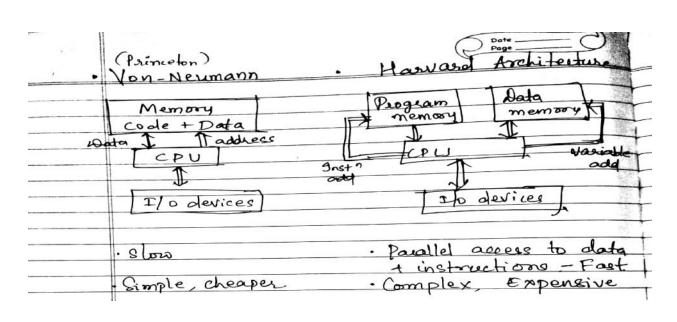

| • | Mps based on von-         | · Mc based on Hasilasd      |

|   | neumann model where       | architectuse where          |

|   | peogram 4 data are stored | program 4 data memory       |

| _ | in Same memory module.    | program 4 data memory.      |

|   |                           |                             |

|   | Page                                        |

|---|---------------------------------------------|

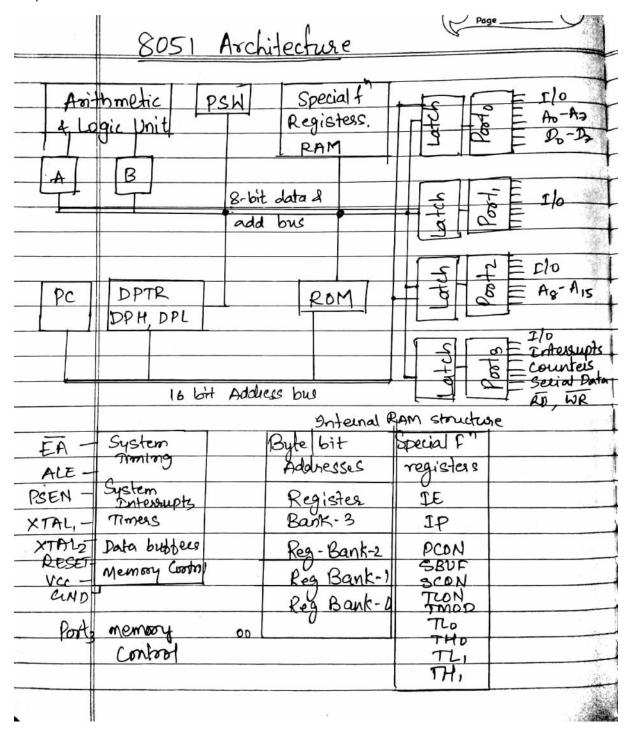

|   | Specific features of 8051 Architecture.     |

| • | Eight bit CPU with registers A (Accumulator |

|   | and B.                                      |

|   | Sinteen-bit program Counter (PC) of data    |

|   | pointes (DPTR)                              |

|   | Eight bit Stack pointer (SP)                |

| • | Internal ROM or EPROM (4K)                  |

|   | Internal RAM of 128 bytes.                  |

|   | · Four segistes banks cach containing       |

|   | 8 legisters.                                |

|   | · 16 bytes, whice can be addressed at       |

|   | the bit level.                              |

|   | · 80 loytes of general purpose data memos   |

|   | 32 i/o pins assanged as 4-8 bit poots       |

|   | Po - P3.                                    |

|   | Two 16-bit Times [counters: To and Ti       |

|   | Full duplex Social data receives/transmit   |

|   | Her : SBUF.                                 |

| A | Control registers. TON, TMOD SCON, PLON, FP |

|   | a It.                                       |

|   | Two enternal and three internal intersupt   |

|   | Sources.                                    |

| • | Oscillator 4 clock circuits.                |

|   | 3 3 4 1 Com 4 1 Com (3.                     |

|   |                                             |

|   | 286/30                                      |

|   | <b>A</b>                                                       |

|---|----------------------------------------------------------------|

|   | Program Counter                                                |

|   | + 16 bit Register hold the address of inst'                    |

|   | which u to be executed.                                        |

|   | * Pe is automatically incremented after                        |

|   | every instruction byte is fetched a may                        |

|   | also be altered by certain instruction.                        |

|   | * PC is the only register that does not have                   |

|   | an internal address.                                           |

|   |                                                                |

|   | OPTR (data pointer)                                            |

|   | , 16 bit register made rep 9 two 8-bit                         |

|   | registers DPH of DPL, points to add in Ent My                  |

|   | * Exteenal memory access.                                      |

| - | CD11 100'cto1                                                  |

|   | A & B CPU registers  Total 34 general-prupose working register |

|   | A, B 4 32 Registers în Bank.                                   |

|   | * A & B , holds regult after many operations.                  |

|   | 1. Addition Subtraction, multo 4 div"                          |

|   | 2: Boolean bit manipulation.                                   |

|   | 3. Data transfers between the 80114                            |

|   | enternal memory.                                               |

|   | 0                                                              |

|     |                                        | 5    |

|-----|----------------------------------------|------|

|     | Ports                                  |      |

| 10. | Ao post.                               |      |

|     | * Atternate functions.                 | - 3  |

|     |                                        |      |

|     | Pin Atternate use SFR                  |      |

|     | P37-RXD Social Data Pront SBUF         |      |

|     | D-TXD Serial data output SBVF          |      |

|     | Ros - INTO External intersupt . I CON. | 1    |

|     | Parterna Interscept, TCO               | 1.3  |

|     | D - To External times input TN         | 10 D |

|     | Follows times input TI                 | MO1) |

|     | 13.5 - WR Enternal memory write pulse  |      |

|     | Pa - RD Exteenal memosy read "         |      |

|     | 137                                    |      |

For listing the names of the pins - 2 M

Explain briefly about each pin. 2 M

36.

a. XCHD A, @ Po > Exchanges the lower nibbles of A's content and content of the memory location pointed by Ro. Indirect adolessing made.

1 byte memory required

b. Move A, @A+DPTR => Reading from Code memory

The content of A and DPTR are added to make the

complete address, from where data is read into A.

4 Andirect addressing mode, \* 1 byte required.

4 ADDC A, @Ro => Add content of A 4 Content of memory

cocation pointed by Ro along with C.

4 Andirect addressing mode, 1 byte required

Operation explaination - 1M

Addressing mode - 0.5 M

Number of bytes - 0.5M

total 2M for each instruction.

2\*3=6

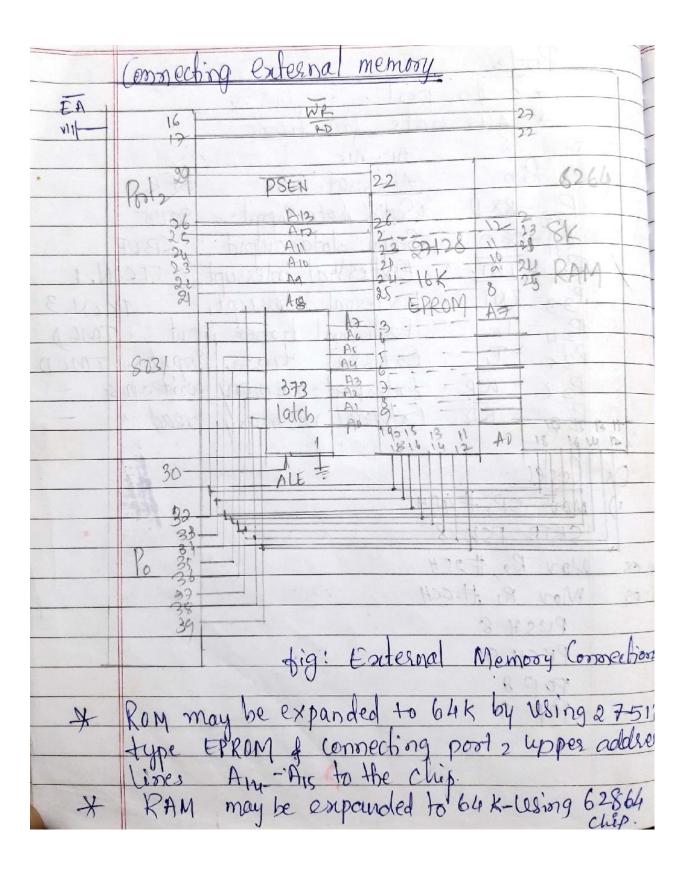

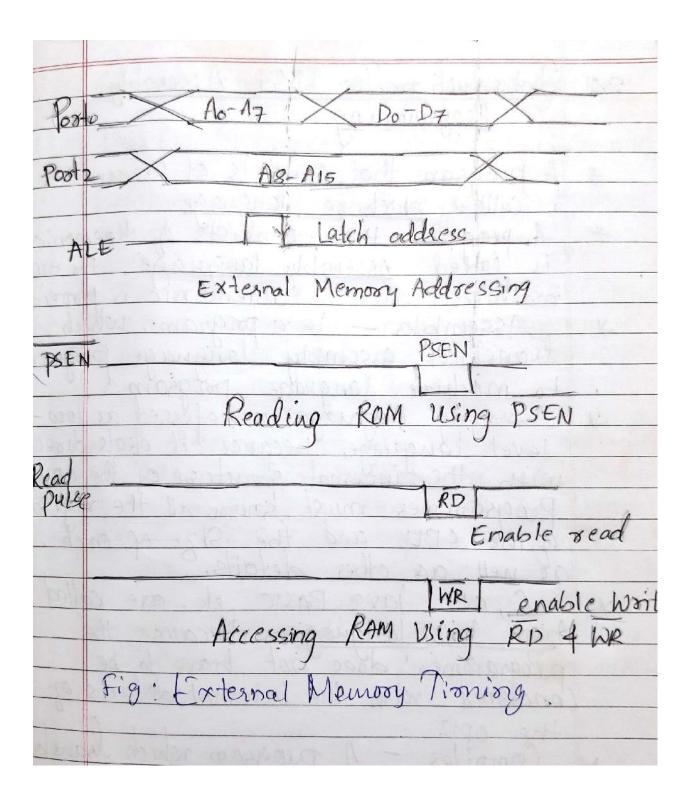

4. Explain how to interface 8K ROM and 4K RAM memory to 8051.

Soln: Diagram of connection -4M

Timing diagram-2M

Explaination - 4M

Note: The following diagram shows connecting 16k ROM and 8k RAM, but in exam its asked for 8k ROM and 4K RAM. For connecting 8K ROM memory 13 (A0-A12) address bits are required and for 4k RAM memory 11 (A0-A11) address bits are required.

Explanation

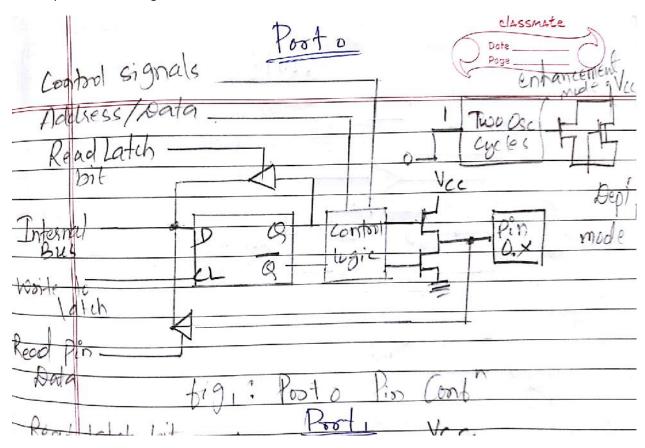

|       | By default all one i/p profs                                                                          |

|-------|-------------------------------------------------------------------------------------------------------|

| a     | losto, as in i/p - 1 is worthen to                                                                    |

|       | the latch. So but moesete are off.                                                                    |

|       | Hence critput pins have floats.                                                                       |

|       | hence whatever data written on pin is directly & read by read pin                                     |

|       | is directly so read by read pro.                                                                      |

| 16.   | Posto as an old post - output post                                                                    |

|       | Posto as an ofp post -> output post  . If we count to write I on pin of                               |

|       | Posto, i's written to the latch                                                                       |

|       | which turns of the lovoes FE?                                                                         |

|       | * o' control signal trune off upper FET                                                               |

|       | So we get floating value St to<br>convert that I loating value into<br>lugic I be need to connect the |

| -     | convert that Coating Value into                                                                       |

|       | lugic 1 we need to connect The                                                                        |

|       | pull up resistor pasallel to upper<br>FET. Its done only when Port o initialized                      |

|       | ons outplat Port.                                                                                     |

| - 5   | The we want to write o on Pin                                                                         |

|       | of ports when p is written to                                                                         |

| 1000  | the latch the pin is pulled down                                                                      |

|       | by the lower CET thence ofp                                                                           |

| -, Co | becomes zero                                                                                          |

| a a   | old/data -> (ontool is 1, add/data love Conton)                                                       |

| the   | output driver FETC.                                                                                   |

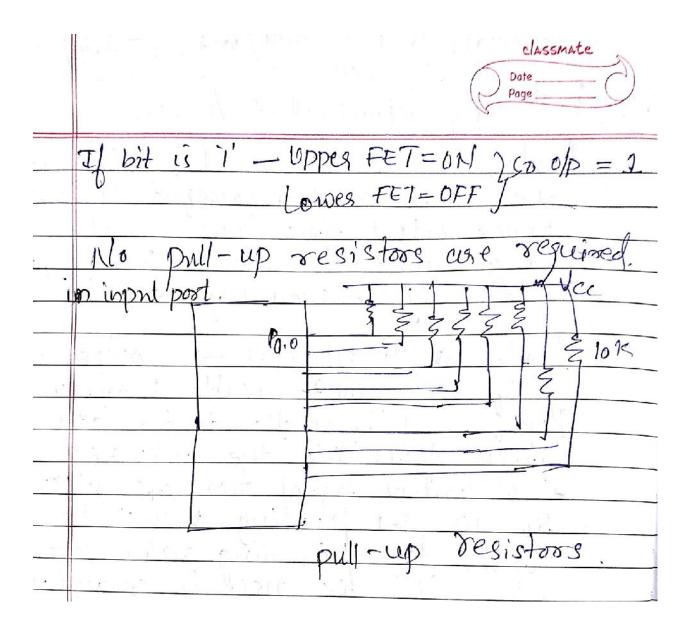

| I     | bit is 0 -> Upper FET IS OFF TOP                                                                      |

|       | Scanned by CamScanner                                                                                 |

5. b What is stack memory. Explain PUSH and POP instructions in stack memory.

Soln= Definition of stack memory - 1M

Push and Pop- 2M each

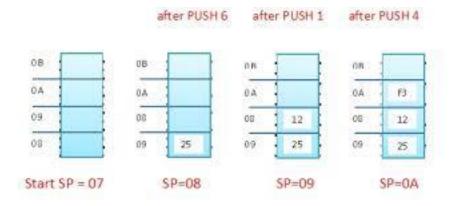

## PUSH and POP operation of stack memory in microcontroller

it s part of RAM in which data will store temporary during execution of program.

STACK work on last in first out principal.to store and retrieve data during program execution in stack push and pop instruction work for it.

#### **PUSH:**

its used to store data into stack.

#### POP:

to retrieve data from stack.

#### SP:

stack pointer is 8 bit register which store value of top of the stack.

by default stack pointer contain 07h.

#### **PUSH AND POP OPERATION:**

#### **PUSH:**

using push operation stack pointer increased first and then content of register or memory will store on that stack location which stored in SP.

here SP contain =07h

**PUSH R6**;SP increased by one and contain of R6 store into 08 location.

**PUSH R1**;SP increased again by one and contain of R1 stored into 09 location.

**PUSH R4**;SP increased again by one and contain of R4 stored into 0A location.

### POP:

In this retrieve data first and then stack pointer decreased by one.

if we write

**POP 20h;** then content at 0Ah location will copy into 20h then stack pointer decrease by 1.

**POP 21h**; then content at 09h location will copy into 21h then stack pointer decrease by 1.

6. a Explain the data types and assembly directives in 8051

06 marks

| ρυ  |                                              |

|-----|----------------------------------------------|

|     | 8051 Data Types and Directives               |

|     |                                              |

|     | Datatype                                     |

|     | Datatype  8051 has only one data type. It is |

|     | 8 bits.                                      |

|     |                                              |

|     | Directives                                   |

| 0%  | Assembles directives give directions to      |

| ,   | TISSENTORY CURRENTS GIVE CONSECTIONS TO      |

| -   | the assembler. The machine codes are not     |

|     | generated for assembler directives in        |

|     | porgram                                      |

| _   |                                              |

|     | 1. DB (define byte)                          |

|     | It is used to define the 8 bit data          |

| • * | When DB is used to define data, the          |

|     | numbers can be in decimal, binary, hex       |

|     | or Asc11 formats.                            |

|     | ORG 500H                                     |

|     | DATA1: DB 28: Il decional                    |

|     | DATA: DB 00/10/10/ Bionasa                   |

|     | DATAS: DB 39 H NHEX                          |

| 1   | DATAL : DB 2959" 11 ASCERN                   |

|     | DRG 5184                                     |

| 1   | DATA: pp "My Name is Joe" Unscor             |

|     | character                                    |

| 1   |                                              |

|     | [ MOV DOTR, # DATA, 7 classmate                                      |

|-----|----------------------------------------------------------------------|

|     | MOVE A, @ A+ DOTE.                                                   |

|     | le.                                                                  |

|     | + The DB directive is the only directive                             |

|     | that can be used to define Ascar Strings larger than two characters. |

|     | larger than two characters.                                          |

|     | used around ASCII strings.                                           |

|     | used around ASCII Smage.                                             |

|     | a BPC ( mining)                                                      |

|     | 2. ORG (origin) The ORG dissective is used to indic-                 |

|     | ate the beginning of the address. The                                |

|     | number that comes after ORG can be either                            |

|     | in hex or in decimal. If number is not                               |

| (2) | Involved by H. it is decimal and the asser                           |

|     | holes will convert it to hex                                         |

|     | Some assembless use. ". org" instead                                 |

|     | of " org " for the origin directive.                                 |

| 27  | La talenta (                                                         |

|     | 3. EQU (cquate)                                                      |

|     | without constant                                                     |

| 1 1 | The EQU directive does not set aside                                 |

|     | Storage for a data Hem but associates                                |

|     | a constant value with a data label so that                           |

|     | I along the label appears in the program                             |

|     | its constant value will be substituted                               |

|     | for the label.                                                       |

|     |                                                                      |

EQU 25 COUNT R3 + COUNT MOY When executions the instruction 1' Mov R3, # count, the registes no programmer wants to change the Count value, by the use of Ego, he change it once & assembles will change all of its occurances, mather LEND directive. This indicates to the assembles the Source file. Its the in the Source code anything after the END directive is ignored by the assemb & Some assemblers use END "END"

6. b . Calculate the time required for executing a 2 machine cycle instruction if frequency is

a. 12Mhz b. 11.0592m

solution-

Time for 2 machine cycle = Time for 2 machine cycle \*2

= (1/frequency )\*12d \*2

a. 12Mhz.

=(1/12Mhz)\*12\*2=2 micro sec

b. 11.0592 MHz

=(1/11.0592Mhz)\*12\*2= 2.17micro sec

7. a)

To. Show the stack contents, sp contents and contents of any register affected after each step of the following sequences of operation.

ADD A, Rs

$$\rightarrow$$

A = A+Rs=74H

$$POP 4$$

$\Rightarrow O4H = 30H \text{ or } R_{4} = 30H.$   $SP = 71H.$

7. b Explain the PSW in 8051 micro controller

2 marks - PSW Structure

2 marks - Explaination

# Flags and the Program Status Word (PSW)

Flags are 1-bit registers provided to store the results of certain program instructions. Other instructions can test the condition of the flags and make decisions based on the flag states. In order that the flags may be conveniently addressed, they are grouped inside the program status word (PSW) and the power control (PCON) registers.

The 8051 has four math flags that respond automatically to the outcomes of math operations and three general-purpose user flags that can be set to 1 or cleared to 0 by the programmer as desired. The math flags include Carry (C), Auxiliary Carry (AC), Overflow (OV), and Parity (P). User flags are named F0, GF0, and GF1; they are general-purpose flags that may be used by the programmer to record some event in the program. Note that all of the flags can be set and cleared by the programmer at will. The math flags, however, are also affected by math operations.

The program status word is shown in Figure 3.4. The PSW contains the math flags, user program flag F0, and the register select bits that identify which of the four general-purpose register banks is currently in use by the program. The remaining two user flags, GF0 and GF1, are stored in PCON, which is shown in Figure 3.13.

Detailed descriptions of the math flag operations will be discussed in chapters that cover the opcodes that affect the flags. The user flags can be set or cleared using data move instructions covered in Chapter 5.

SECTION 3.1 • 8051 Microcontroller Hardware

| 7  | 6  | 5  | 4   | 3   | 2  | 1 | 0 |

|----|----|----|-----|-----|----|---|---|

| CY | AC | F0 | RS1 | RS0 | OV | _ | Р |

# The Program Status Word (PSW) Special Function Register

| Bit | Symbol | Functi                                                                 | on                                            |                                        |  |  |  |  |

|-----|--------|------------------------------------------------------------------------|-----------------------------------------------|----------------------------------------|--|--|--|--|

| 7   | CY     | Carry flag; used in arithmetic, jump, rotate, and Boolean instructions |                                               |                                        |  |  |  |  |

| 6   | AC     | Auxilia                                                                | Auxiliary Carry flag; used for BCD arithmetic |                                        |  |  |  |  |

| 5   | FO     | User flag 0                                                            |                                               |                                        |  |  |  |  |

| 4   | RS1    | Registe                                                                | er bank se                                    | elect bit 1                            |  |  |  |  |

| . 3 | RS0    | Registe                                                                | elect bit 0                                   |                                        |  |  |  |  |

|     |        | RS1                                                                    | RS0                                           |                                        |  |  |  |  |

|     |        | 0                                                                      | 0                                             | Select register bank 0                 |  |  |  |  |

|     |        | 0                                                                      | 1                                             | Select register bank 1                 |  |  |  |  |

|     |        | 1                                                                      | 0                                             | Select register bank 2                 |  |  |  |  |

|     |        | 1                                                                      | 1                                             | Select register bank 3                 |  |  |  |  |

| 2   | OV     | Overflo                                                                | w flag; us                                    | sed in arithmetic instructions         |  |  |  |  |

| 1   |        | Reserved for future use                                                |                                               |                                        |  |  |  |  |

| 0   | Р      | Parity fl                                                              | ag; show                                      | s parity of register A: 1 = Odd Parity |  |  |  |  |

|     |        | Bit addr                                                               | essable a                                     | as PSW.0 to PSW.7                      |  |  |  |  |

|     |        |                                                                        |                                               |                                        |  |  |  |  |

FIGURE 3.4 • PSW Program Status Word Register

69

8. a) Exchange the contents of R5 and R6 register contents with any four different methods.

2.5 M for each method.

2.5 \*4 =10M

1. Method: Using Temposary Reg Ri MOV A, RS MOV R4, A // R4 - R5 MOV A, RE  $|| R_s \leftarrow R_\ell$ MOV RS, A MOV A, Ry 11 R6 ← Ry MOV RE, A

Methods: Using Direct addressing mode, using 104 Temporary memory location.

MOV 10H, 05 H

MOV 05H, 06H

MOV 06H, 10H

Methods - Using Stack memory

Push 06H SP=08= R6 content

PUSH OSH Sp=09 = Re content

POP OBH

06 H = Rz Loontent, SP=08 H 05 H = R6 Lontent, SP=07 H

POP OSH

THE REAL PROPERTY.

Methody - Using exchange instruction. XCH A, R6 Mov A, R6

- tall and a

XCH A) RS OR XCH A, RS

XCH A, Re

MOY RE, A