1.

# Improvement test

| Sub:                                                                                                            | Sub: DIGITAL SYSTEM DESIGN Code |                 |             |                    |           |           |                 |             |       | 15EE | 35  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------|---------------------------------|-----------------|-------------|--------------------|-----------|-----------|-----------------|-------------|-------|------|-----|--|--|--|

| Date:                                                                                                           | 17/ 11/ 2017                    | Duration:       | 90 mins     | Max Marks:         | 50        | Sem:      | 3 <sup>RD</sup> | Branch: EEE |       |      |     |  |  |  |

|                                                                                                                 | Answer Any FIVE FULL Questions  |                 |             |                    |           |           |                 |             |       |      |     |  |  |  |

|                                                                                                                 |                                 |                 |             |                    |           |           |                 |             | Marks |      |     |  |  |  |

|                                                                                                                 |                                 |                 |             |                    |           |           |                 |             | With  | CO   | RBT |  |  |  |

| Simplify the expression using Quine- McCluskey method(i) $F(A,B,C,D) = \sum m(0,1,2,6,7,9,10,12) + \sum d(3,5)$ |                                 |                 |             |                    |           |           |                 | 10          | CO1   | L3   |     |  |  |  |

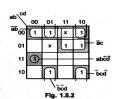

| 2 Simplify f(a,b,c,d)=∑m(1,5,7,10,11)+dc(2,3,6,13) taking least significant bit as map entered variable.        |                                 |                 |             |                    |           |           |                 | 10          | CO1   | L3   |     |  |  |  |

| 3 Design a synchronous Mod-7 counter using T flip flop                                                          |                                 |                 |             |                    |           |           |                 | 10          | CO3   | L3   |     |  |  |  |

| 4 Convert SR flip flop in to JK and T flip flop and represent symbolically.                                     |                                 |                 |             |                    |           |           |                 | 10          | CO4   | L2   |     |  |  |  |

| 5 Explain behavioral and data flow type of description of VHDL with the example of half adder.                  |                                 |                 |             |                    |           |           |                 | ler.        | 10    | CO5  | L2  |  |  |  |

| 6                                                                                                               | Compare VHDL and Ve             | erilog. Explain | how data ty | pes are classified | in Verilo | og with e | xampl           | e           | 10    | CO5  | L2  |  |  |  |

| Minterm         | Binary represenation | Minterm           | Binary representation |

|-----------------|----------------------|-------------------|-----------------------|

| m <sub>0</sub>  | 0000                 | m₀✓               | 0000                  |

| m <sub>1</sub>  | 0001                 | m <sub>1</sub> ✓  | 0001                  |

| m <sub>2</sub>  | 0010                 | m <sub>2</sub> √  | 0010                  |

| m <sub>6</sub>  | 0110                 | dm₃✓              | 0011                  |

| m <sub>7</sub>  | 0111                 | dm <sub>5</sub> √ | 0101                  |

| m <sub>9</sub>  | 1001                 | m <sub>6</sub> √  | 0110                  |

| m <sub>10</sub> | 1010                 | m <sub>9</sub> ✓  | 1001                  |

| m <sub>12</sub> | 1100                 | m <sub>10</sub> √ | 1010                  |

| dm <sub>3</sub> | 0011                 | m <sub>12</sub> √ | 1100                  |

| dm <sub>5</sub> | 0101                 | m <sub>7</sub> √  | 0111                  |

| Minterm | Binary representation | Minterm    | Binary representation |

|---------|-----------------------|------------|-----------------------|

| 0, 1✓   | 000-                  | 0, 1, 2, 3 | 00                    |

| 0, 2✓   | 00-0                  | 1, 3, 5, 7 | 0 1                   |

| 1,3✓    | 00-1                  | 2, 3, 6, 7 | 0-1-                  |

| Minterms   | Binary representation                                   |

|------------|---------------------------------------------------------|

| 0, 1, 2, 3 | 00                                                      |

| 1, 3, 5, 7 | 01                                                      |

| 2, 3, 6, 7 | 0-1-                                                    |

| 1, 9       | -001                                                    |

| 2, 10      | -010                                                    |

| 12         | 1100                                                    |

|            | 0, 1, 2, 3<br>1, 3, 5, 7<br>2, 3, 6, 7<br>1, 9<br>2, 10 |

| Prime<br>implicants | m <sub>o</sub> | m, | m <sub>2</sub> | dm <sub>3</sub> | dm <sub>6</sub> | m <sub>e</sub> | m <sub>7</sub> | m <sub>9</sub> | m <sub>10</sub> | m, |

|---------------------|----------------|----|----------------|-----------------|-----------------|----------------|----------------|----------------|-----------------|----|

| ãБ 0, 1, 2, 3       | 0              | 0  | 0              | 0               |                 |                |                |                |                 |    |

| ãd 1, 3, 5, 7       |                |    |                | •               |                 |                | 98 . J         |                |                 |    |

| āc 2, 3, 6, 7       |                |    | 0              | 0               |                 | 0              | 0              |                |                 |    |

| bcd 1,9             |                | 0  |                |                 |                 |                |                | 0              |                 |    |

| b c d 2, 10         | 1918-0 E       |    | 0              |                 |                 |                |                |                | 0               |    |

| abcd 12             |                |    |                |                 |                 | e sala         |                |                |                 | 0  |

$f(a, b, c, d) = \bar{a}\bar{b} + \bar{a}c + \bar{b}\bar{c}d + \bar{b}c\bar{d} + ab\bar{c}\bar{d}$

| Minterns<br>in decimal | Minterms in binary |   |   |        |   |  |

|------------------------|--------------------|---|---|--------|---|--|

|                        | w                  | × | у | z(MEV) |   |  |

| 0 0                    | 0                  | 0 | 0 | 0      | 0 |  |

| 1                      | 0                  | 0 | 0 | 1      | 1 |  |

| 1 2 3                  | 0                  | 0 | 1 | 0      | x |  |

| [3                     | 0                  | 0 | 1 | 1      | x |  |

| 2 4 5                  | 0                  | 1 | 0 | 0      | 0 |  |

| 7(5                    | 0                  | 1 | 0 | 1      | 0 |  |

| 3 6 7                  | 0                  | 1 | 1 | 0      | x |  |

| 7 7                    | 0                  | 1 | 1 | 1      | î |  |

| 4 8 9                  | 1                  | 0 | 0 | 0      | 0 |  |

| *\9                    | 1                  | 0 | 0 | 1      | 0 |  |

| _ [10                  | 1                  | 0 | 1 | 0      | 1 |  |

| 5 11                   | 1                  | 0 | 1 | 1      | 1 |  |

| _ [ 12                 | 1                  | 1 | 0 | 0      | 0 |  |

| 6 { 12<br>13           | 1                  | 1 | 0 | 1      | × |  |

| (14                    | 1                  | 1 | 1 | 0      | 0 |  |

| 7 14<br>15             | i                  | 1 |   | 1      | C |  |

4.

| Ing | Inputs |     |                  |   | Next<br>state | Flip-flop inputs |  |  |

|-----|--------|-----|------------------|---|---------------|------------------|--|--|

| J   | K      | Qn  | Q <sub>n+1</sub> | S | R             |                  |  |  |

| 0   | 0      |     | 0                | 0 | x             |                  |  |  |

| 0   | 0      | 1 1 | 1 1              | x | 0             |                  |  |  |

| 0   | 1      | 0   | 0                | 0 | x             |                  |  |  |

| 0   | 1      | 1   | 0                | 0 | 1             |                  |  |  |

| 1   | 0      | 0   | 1                | 1 | 0             |                  |  |  |

| 1   | 0      | 1   | 1                | x | 0             |                  |  |  |

| 1   | 1      | 0   | 1                | 1 | 0             |                  |  |  |

| 1   | 1      | 1   | 0                | 0 | 1             |                  |  |  |

# 3.11.3 SR Filp-Flop to T Filp-Flop

| Input | Present state  | Next state               | Flip-flo                                        | p inputs                                              |

|-------|----------------|--------------------------|-------------------------------------------------|-------------------------------------------------------|

| T     | Q <sub>n</sub> | Qn + 1                   | S                                               | R                                                     |

| 0     | 0              | 0                        | 0                                               | x                                                     |

| 0     | 1              | 1                        | x                                               | 0                                                     |

| 1     | 0              | 1                        | 1                                               | 0                                                     |

| 1     | 1              | 0                        | 0                                               | 71 T                                                  |

|       | T 0            | T Q <sub>n</sub> 0 0 0 1 | T Q <sub>n</sub> Q <sub>n+1</sub> 0 0 0 0 0 1 1 | T Q <sub>n</sub> Q <sub>n+1</sub> S 0 0 0 0 0 0 1 1 X |

|     | Fo  |   | Fe    | or R |   |

|-----|-----|---|-------|------|---|

| 19  | 0   | 1 | 10    | 0    | 1 |

| 0   | 0   | x | 0     | x    | 0 |

| - 1 | 1   | 0 | - 1   | 0    | 1 |

|     | S = |   | R = 1 | r Q, |   |

## **Behavioral Descriptions**

A behavioral description models the system as to how the outputs behave with the inputs. The definition of behavioral description is one where the architecture (VHDL) or the module (Verilog) includes the predefined word process (VHDL) or always (Verilog) or initial (Verilog). The description is considered pure behavioral if it does not contain any other features from other styles or descriptions (

### Data-Flow Descriptions

Data flow describes how the system's signals flow from the inputs to the outputs. Usually, the description is done by writing the Boolean function of the outputs. The data-flow statements are concurrent; their execution is controlled by events.

### **VHDL Behavioral**

```

entity half_add

port (I1, I2

in bit; 01, 02 : out bit);

end half_add;

architecture

of half_add is

-- The archi

consists of a process construct

begin

process (I1, I2)

-- The above

is process statement

begin

01 <= I1

I2 after 10 ns;

02 <= I1

I2 after 10 ns;

end process;

behave

```

#### **VHDL Data-Flow Description**

```

entity halfadder is

port (

a : in bit;

b : in bit;

s : out bit;

c : out bit);

end halfadder;

architecture HA_DtFl of halfadder is

--The architecture has no process, component, cmos,

--tranifO, tran, or tranifO

begin

s <= a xor b;

c <= a and b;

end HA_DtFl;</pre>

```

#### Data Types

VHDL: Definitely a type-oriented language, VHDL types are built in, or the user can create and define them. User-defined types give the user a tool to write the code effectively; these types also support flexible coding, VHDL can handle objects with multidimensional array types. Another data type that VHDL supports is the physical type; the physical type supports more synthesizable or targeted design code.

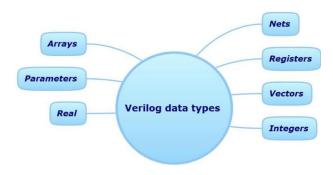

Verilog: Compared to VHDL, Verilog data types are very simple and easy to use. All types are defined by the language. There are no user-defined types. Some beginners may consider these simple data types as an advantage over VHDL. Verilog, however, cannot handle objects with multidimensional array types.

#### ■ Ease of Learning

VHDL: For beginners, VHDL may seem hard to learn because of its rigid type requirements. Advanced users, however, may find these rigid type requirements easier to handle.

Verilog: Easy to learn, Verilog users just write the module without worrying about what Library or package should be attached. Many of the statements in the language are very similar to those in C language.

#### Libraries and Packages

VHDL: Libraries and packages can be attached to the standard VHDL package. Packages can include procedures and functions, and the package can be made available to any module that needs to use it. Packages are used to target a certain design. For example, if the system modeled/designed includes arithmetic functions, a package can be used that includes those functions.

Verilog: There is no concept of Libraries or packages in Verilog.

#### Operators

VHDL: An extensive set of operators is available in VHDL, but it does not have predefined unary operators.

Verilog: An extensive set of operators is also available in Verilog. It also has predefined unary operators (see Section 1.4).

Procedures and Tasks: Procedures (VHDL) and tasks (Verilog) are implemented to simplify the writing of HDL code for complex systems.

### Data types in Verilog