## Internal Assesment Test - I

| Sub:  | Analog Electronics | 3         |          |               |          |      |     | Code:   | 15EC32  |

|-------|--------------------|-----------|----------|---------------|----------|------|-----|---------|---------|

| Date: | 18 / 09 / 2017     | Duration: | 90 mins  | Max Marks:    | 50       | Sem: | 3rd | Branch: | ECE (C) |

|       |                    | A         | nswer An | y FIVE FULL ( | )uestion | S    |     |         |         |

|                                                                                                                                                               | Manle           | OBE |     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----|-----|

|                                                                                                                                                               | Marks           | CO  | RBT |

| 1 (a) Analyze the Common base configuration with a circuit diagram.                                                                                           | [05]            | CO1 | L4  |

| (b) Obtain $Z_i$ , $Z_0$ , $A_v$ and $A_i$ for CB configuration using h-parameters.                                                                           | [05]            | CO1 | L4  |

| Apply the complete hybrid equivalent model, to determine the input impedar impedance, voltage gain and current gain of transistor amplifier in terparameters. |                 | CO1 | L3  |

| Explain the BJT amplifier transistor modeling in detail.                                                                                                      | [10]            | CO1 | L4  |

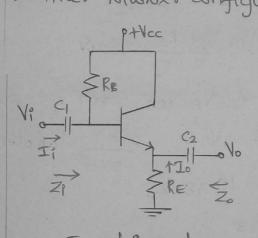

| Draw the emitter follower configuration. Derive its input impedance, output in voltage gain and current gain using h-parameters.                              | mpedance, [10]  | CO1 | L3  |

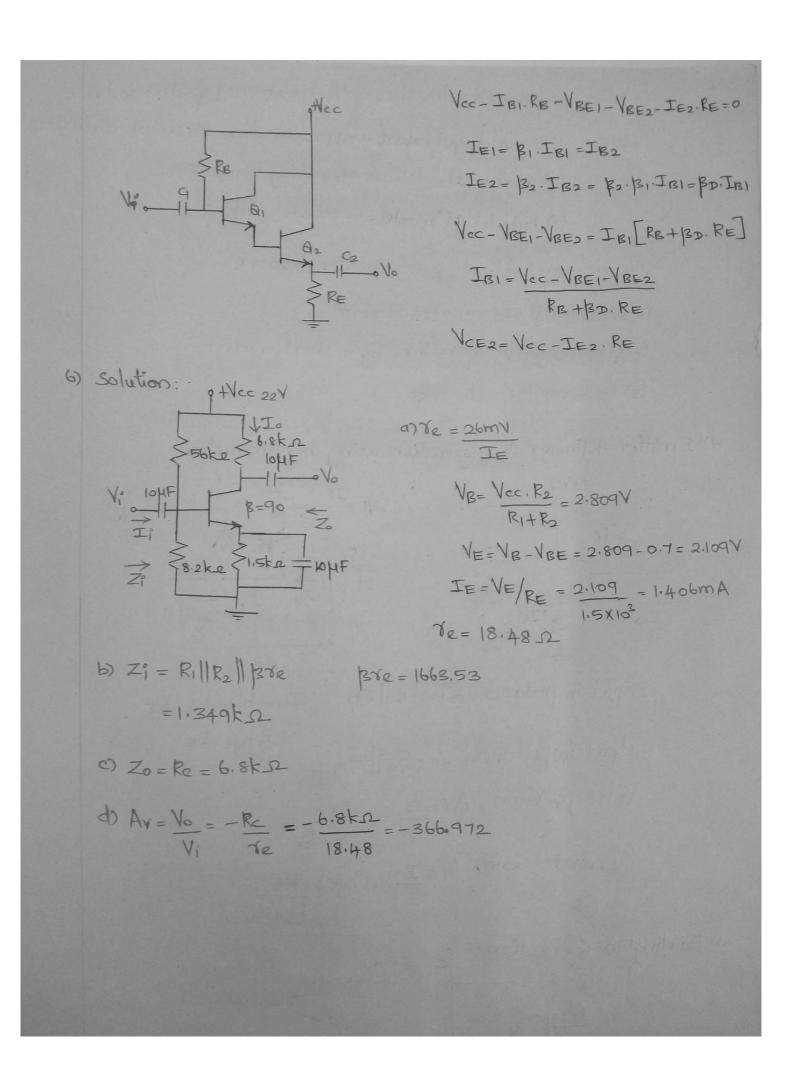

| 5 Explain the Darlington Connection with a neat diagram. Analyze the l                                                                                        | Darlington [10] | CO1 | L4  |

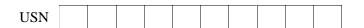

For the network shown in the figure, calculate  $r_{e_i}$   $Z_{i_i}$   $Z_{0}$   $(r_{0}=$  ) and  $A_{v_i}$   $(r_{0}=$  .).

connection DC bias condition using emitter follower configuration.

| [10] | CO1 | L3 |  |  |

|------|-----|----|--|--|

|      |     |    |  |  |

|      |     |    |  |  |

|      |     |    |  |  |

|      |     |    |  |  |

|      |     |    |  |  |

|      |     |    |  |  |

|      |     |    |  |  |

|      |     |    |  |  |

IAT-1 (Analog Electronics)

Solutions

1)

Common-Base Configuration:

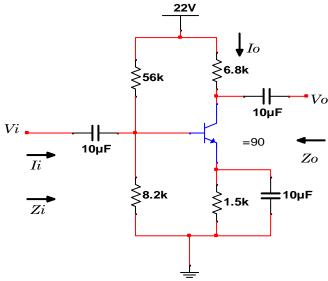

(b) CB configuration using b-parameters:

Input împedance, Zi = Rellhib

Out put impedance, Zo = Re 11/hob = Re

2) Complete Hybrid Equivalent Model:

current gain,  $Ai = \underline{I_o}$  Apply kcl to the deatput  $I_o = hf \cdot I_b + I$   $I_o = hf \cdot I_b - ho \cdot I_o \cdot R_L$   $Ai = \underline{I_o} = hfe$   $I_i = hf \cdot R_L$

Modeling-approximates the actual behavior of semiconductor.

3 types (1) hybrid equivalent - approximation based on datasheet

- (2) remodel-actual operating conditions.

- (3) hybrid pi model-feedback effect.

- The ac equivalent of a transistor network

- (1) setting all de sources to zero

- (2) Replacing all capacitors by a short circuit.

- (3) Redraw the network

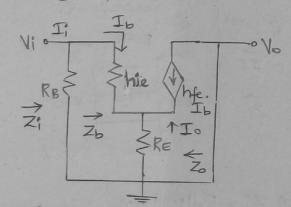

- 4) Emitter-Follower configuration using h-parameters

Input impedance, Zi=RB||Zb Zb=hie+hfe.RE

Zb=hfe. RE

Output impedance, Zo = RE | hie/hfe

Current Gain, Ai = Io = h.fe. RB

RB+Zb