| USN |  |  |  |  |  |

|-----|--|--|--|--|--|

## Internal Assessment Test 1 – Sept. 2017

| S                                                                                                          | ub: DSP Algorith   | nm and Arch   | itecture   |                  |               | Sub Code:      | 10TE74/10EC751       | Bran | ch: T | CE/EC | EΕ  |

|------------------------------------------------------------------------------------------------------------|--------------------|---------------|------------|------------------|---------------|----------------|----------------------|------|-------|-------|-----|

| Da                                                                                                         | ite: 21/09/2017    | Duration:     | 90 mins    | Max Marks:       | 50            | Sem / Sec:     | 7/A,B,C,D            |      |       | OI    | ВE  |

|                                                                                                            |                    | <u>An</u> :   | swer any l | FIVE FULL Qu     | <u>iestio</u> | <u>ons</u>     |                      |      | MAR   | CO    | RBT |

|                                                                                                            |                    |               |            |                  |               |                |                      |      | KS    |       |     |

| 1 (a)                                                                                                      | An analog signal   | l is sampled  | at the ra  | te of 8khz. If   | 512           | samples of     | this signal are used | l to | [04]  | CO1   | L3  |

|                                                                                                            | compute DFT X(     | k). Calculate | the analo  | g and digital f  | reque         | ency spacing   | between adjacent 2   | K(k) |       |       |     |

|                                                                                                            | elements. Also, c  | alculate anal | og and dig | gital frequencie | es cor        | responding     | to k=64.             |      |       |       |     |

| (b)                                                                                                        | With a neat diag   | ram explain 1 | the schem  | e of a DSP syst  | tem.          |                |                      |      | [06]  | CO1   | L1  |

| 2 (a)                                                                                                      | Explain the two    | methods of    | sampling   | rate conversi    | ons 1         | used in DSF    | system, with suita   | able | [06]  | CO1   | L1  |

| _ ()                                                                                                       | block diagrams.    |               | F          | ,                |               |                | - ,                  |      | []    |       |     |

| (b) Let $x(n)=[0,3,6,9,12]$ be interpolated with L=3. If the filter coefficients of the filters are $b_k=$ |                    |               |            |                  |               | <sub>1</sub> = | [04]                 | CO1  | L3    |       |     |

| ( )                                                                                                        | [1/3, 2/3, 1,2/3,1 | =             | -          |                  |               |                |                      | r.   |       |       |     |

| 3 (a)                                                                                                      |                    |               |            |                  |               |                | nine i) System Func  | tion | [05]  | CO1   | L3  |

| ( )                                                                                                        | ii) Magnitude and  |               |            |                  | •             |                | •                    |      |       |       |     |

| (b)                                                                                                        | Explain the purp   | -             | •          |                  |               |                |                      |      | [05]  | CO2   | L1  |

| ( )                                                                                                        | 1 1 1              | 1 0           | 1          |                  | 0             |                |                      |      |       |       |     |

|                                                                                                            |                    |               |            |                  |               |                |                      |      |       |       |     |

|                                                                                                            |                    |               |            |                  |               |                |                      |      |       |       |     |

| 4 (a) | Give the structure of a 4X4 Braun multiplier, Explain its concept. What modification is required to carry out multiplication of signed numbers? Comment on the speed of the multiplier.  | [07] | CO1 | L1 |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|----|

| (b)   | multiplier.  Compute the sequence in which the input data should be ordered for a 16 point DIT FFT                                                                                       | [03] | CO2 | L3 |

|       | using bit reversed addressing mode.                                                                                                                                                      |      |     |    |

| 5(a)  | What is the role of a shifter in DSP? Explain the implementation of 4-bit shift right barrel                                                                                             | [6]  | CO2 | L1 |

|       | shifter, with a diagram.                                                                                                                                                                 |      |     |    |

| (b)   | Draw the schematic diagram of the saturation logic and explain the same                                                                                                                  | [4]  | CO2 | L1 |

| 6(a)  | Explain the pointer updating algorithm for circular addressing mode.                                                                                                                     | [06] | CO2 | L1 |

| (b)   | Calculate the memory addresses of the operands in each of the following cases of indirect addressing modes? In each case, what will be the content of the <i>addreg</i> after the memory | [04] | CO2 | L3 |

access? Assume that the initial contents of the *addreg* and the *offsetreg* are 0200h and 0010h, respectively. i) ADD \*addreg ii).ADD +\*addreg iii)ADD offsetreg+,\*addreg iv) ADD

\*addreg,offsetreg-

| Give the structure of a 4X4 Braun multiplier, Explain its concept. What modification is                     | [07]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | CO1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | L1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| required to carry out multiplication of signed numbers? Comment on the speed of the                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| multiplier.                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Compute the sequence in which the input data should be ordered for a 16 point DIT FFT                       | [03]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | CO2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | L3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| using bit reversed addressing mode.                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| What is the role of a shifter in DSP? Explain the implementation of 4-bit shift right barrel                | [6]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | CO2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | L1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| shifter, with a diagram.                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Draw the schematic diagram of the saturation logic and explain the same                                     | [4]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | CO2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | L1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| E alabada a sinda a la circa a la crista a Caracianal a a lla crista a manda.                               | [06]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | CO2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | т 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Explain the pointer updating algorithm for circular addressing mode.                                        | [06]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | COZ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | L1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Calculate the memory addresses of the operands in each of the following cases of indirect                   | [04]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | CO2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | L3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| addressing modes? In each case, what will be the content of the <i>addreg</i> after the memory              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| access? Assume that the initial contents of the <i>addreg</i> and the <i>offsetreg</i> are 0200h and 0010h, |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| respectively. i) ADD *addreg ii).ADD +*addreg iii)ADD offsetreg+,*addreg iv) ADD                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| *addreg offsetreg-                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                             | multiplier.  Compute the sequence in which the input data should be ordered for a 16 point DIT FFT using bit reversed addressing mode.  What is the role of a shifter in DSP? Explain the implementation of 4-bit shift right barrel shifter, with a diagram.  Draw the schematic diagram of the saturation logic and explain the same  Explain the pointer updating algorithm for circular addressing mode.  Calculate the memory addresses of the operands in each of the following cases of indirect addressing modes? In each case, what will be the content of the addreg after the memory access? Assume that the initial contents of the addreg and the offsetreg are 0200h and 0010h, | required to carry out multiplication of signed numbers? Comment on the speed of the multiplier.  Compute the sequence in which the input data should be ordered for a 16 point DIT FFT [03] using bit reversed addressing mode.  What is the role of a shifter in DSP? Explain the implementation of 4-bit shift right barrel [6] shifter, with a diagram.  Draw the schematic diagram of the saturation logic and explain the same [4]  Explain the pointer updating algorithm for circular addressing mode. [06]  Calculate the memory addresses of the operands in each of the following cases of indirect addressing modes? In each case, what will be the content of the addreg after the memory access? Assume that the initial contents of the addreg and the offsetreg are 0200h and 0010h, respectively. i) ADD *addreg ii).ADD +*addreg iii)ADD offsetreg+,*addreg iv) ADD | required to carry out multiplication of signed numbers? Comment on the speed of the multiplier.  Compute the sequence in which the input data should be ordered for a 16 point DIT FFT [03] CO2 using bit reversed addressing mode.  What is the role of a shifter in DSP? Explain the implementation of 4-bit shift right barrel shifter, with a diagram.  Draw the schematic diagram of the saturation logic and explain the same [4] CO2  Explain the pointer updating algorithm for circular addressing mode. [06] CO2  Calculate the memory addresses of the operands in each of the following cases of indirect addressing modes? In each case, what will be the content of the addreg after the memory access? Assume that the initial contents of the addreg and the offsetreg are 0200h and 0010h, respectively. i) ADD **addreg iii)ADD **addreg iii)ADD offsetreg+, **addreg iv) ADD |

\_..\_..

USN

## Internal Assessment Test 1 – Sept. 2017 Sub Code: 10TE74/10EC751 Sub: DSP Algorithm and Architecture Branch: TCE/ECE Duration: 90 mins Date: 21/09/2017 Max Marks: 50 Sem / Sec: 7/A,B,C,DOBE Answer any FIVE FULL Questions MAR **RBT** KS 1 (a) An analog signal is sampled at the rate of 8khz. If 512 samples of this signal are used to [04] CO1 L3 compute DFT X(k). Calculate the analog and digital frequency spacing between adjacent X(k) elements. Also, calculate analog and digital frequencies corresponding to k=64. (b) With a neat diagram explain the scheme of a DSP system. [06] CO1 L1 2 (a) Explain the two methods of sampling rate conversions used in DSP system, with suitable [06] CO<sub>1</sub> L1 block diagrams. (b) Let x(n)=[0,3,6,9,12] be interpolated with L=3. If the filter coefficients of the filters [04] CO1 L3 are $b_k = [1/3, 2/3, 1, 2/3, 1/3]$ , Determine the interpolated sequence. 3 (a) For the FIR filter y(n) = (1/3)[x(n) + x(n-1) + x(n-2)]. Determine i) System [05] CO1 L3 Function ii) Magnitude and phase function iii) impulse response iv) group Delay. (b) Explain the purpose of program sequencer with block diagram. [05] CO2 L1

## Internal Assessment Test 1 Key answers-Sept. 2017

Sub: DSP Algorithm and Architecture Sub Code: 10TE74/10EC751 Branch: TCE/ECE

CI: Prof. Pappa M, Mrs. Rashmi K V, Mrs. Reshma P G

1 (a) An analog signal is sampled at the rate of 8khz. If 512 samples of this signal are used to compute DFT X(k). Calculate the analog and digital frequency spacing between adjacent X(k) elements. Also, calculate analog and digital frequencies corresponding to k=64.

Ans: Frequency Spacing  $\Delta f = \frac{F_s}{N} = \frac{8khz}{512} = 15.625$  [2M] Analog Frequency Corresponding to k = 64 is  $\Delta f \times k = 15.625 * 64 = 1000HZ$  [2M]

(b) With a neat diagram explain the scheme of a DSP system.

Ans: DSP is a technique of performing the mathematical operations on the signals in digital domain. As real time signals are analog in nature we need first convert the analog signal to digital, then we have to process the signal in digital domain and again converting back to analog domain. Thus ADC is required at the input side whereas a DAC is required at the output end. A typical DSP system is as shown in figure 1.1

Fig 1.1: A Typical DSP System

A computer or a processor is used for digital signal processing. Antialiasing filter is a LPF which passes signal with frequency less than or equal to half the sampling frequency in order to avoid Aliasing effect. Similarly at the other end, reconstruction filter is used to reconstruct the samples from the staircase output of the DAC (Figure 1.2). [3 M]

Fig 1.2 The Block Diagram of a DSP System

[3M]

Signals that occur in a typical DSP are as shown in figure 1.3.

Fig 1.3: (a) Continuous time signal (b) Sampled Signal (c) Sampled Data Signal (d) Quantized Signal (e) DAC Output

2 (a) Explain the two methods of sampling rate conversions used in DSP system, with suitable block diagrams.

Ans: Decimation is a process of dropping the samples without violating sampling theorem. The factor by which the signal is decimated is called as decimation factor and it is denoted by M. It is given by,

$$y(m) = w(mM) = \sum_{k=-\infty}^{\infty} b_k x(mM - k)$$

where  $w(n) = \sum_{k=-\infty}^{\infty} b_k x(n - k)$  [2 M]

$$\frac{x(n)}{\text{Pass Filter}} \text{Digital Low} \text{w(n)} \text{Sampler} \text{Sampler}$$

[1M]

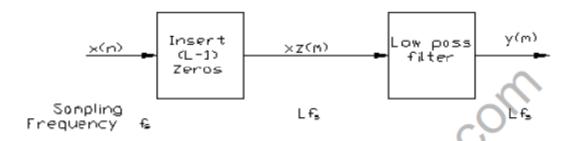

Interpolation is a process of increasing the sampling rate by inserting new samples in between. The input output relation for the interpolation, where the sampling rate is increased by a factor L, is given as, y(m) =

$$\sum_{k=-\infty}^{\infty} b_k w(m-k) \quad \text{where } w(n) = \begin{cases} x\left(\frac{m}{L}\right), m = 0, \pm 1L, \pm 2L, \pm 3L \dots \\ 0, otherwise \end{cases}$$

[2M]

Fig 1.13 Interpolation Process

[1M]

(b) Let x(n)=[0,3,6,9,12] be interpolated with L=3. If the filter coefficients of the filters are  $b_k=[1/3,2/3,1,2/3,1/3]$ , Determine the interpolated sequence.

Ans:

$$x(m) = \{0, 3, 6, 9, 12\}$$

$$L = 3$$

$$bic = \{1/3, 2/3, 1, 2/3, 1/3\}$$

$$lmsm + L - 1 = 3 - 1 = 2 zevos = 2$$

$$w(m) = \{0, 0, 0, 3, 0, 0, 6, 0, 0, 9, 0, 0, 12, 0, 0\}$$

$$y(m) = w(m) + bk$$

$$= \{0, 0, 0, 0.99, 2.01, 3, 3.99, 5.01$$

$$6, 6.99, 8.01, 9, 9.99, 11.01, 12, 9.04, 3.96, 0, 0, 0\}$$

[2M for convolution]

[2M for y(n)]

3 (a) For the FIR filter y(n) = (1/3)[x(n) + x(n-1) + x(n-2)]. Determine i) System Function ii) Magnitude and phase function iii) impulse response iv) group Delay.

Ans:

and phase function iii) impulse response iv) group Delay.

(a) System function

$$H(z) = \frac{y(z)}{x(z)}$$

$y(n) = \frac{1}{3} \left[ x(n) + x(n-1) + x(n-2) \right].$

Taking  $z$ -transform,

$y(z) = \frac{1}{3} \left[ x(z) + z^{-1}x(z) + z^{-2}x(z) \right].$

$y(z) = \frac{1}{3} \left[ x(z) + z^{-1}x(z) + z^{-2}x(z) \right].$

$y(z) = \frac{1}{3} \left[ x(z) + z^{-1}x(z) + z^{-2}x(z) \right].$

$y(z) = \frac{1}{3} \left[ x(z) + z^{-1}x(z) + z^{-2}x(z) \right].$

$y(z) = \frac{1}{3} \left[ x(z) + z^{-1}x(z) + z^{-2}x(z) \right].$

Magnitude Leeponse function

Put

$$z = e^{jn}$$

in  $H(z)$

$$H(z) = \frac{1+z^{2}+z^{2}}{1+e^{-jn}+e^{-jn}}$$

$$H(e^{jn}) = \frac{1}{3} \begin{bmatrix} \frac{z}{2}(e^{-jn}) \\ \frac{z}{2}(e^{-jn}) \end{bmatrix} \longrightarrow (1)$$

weing finite geometric leaves formula

$$\int_{1-e^{-jn}}^{2} a = \frac{1-a}{2} \quad \text{in ean } (1),$$

$$H(e^{jn}) = \underbrace{1-e^{-jn}}_{2} \underbrace{-e^{jn}}_{2} \underbrace{-e^{jn}}_{2}$$

$$= \frac{1}{3} \begin{bmatrix} e^{jn} & e^{jn} \\ e^{jn} & e^{jn} \end{bmatrix} \begin{bmatrix} e^{jn} & e^{jn} \\ e^{jn} & e^{jn} \end{bmatrix}$$

$$= \frac{1}{3} \begin{bmatrix} e^{jn} & e^{jn} \\ e^{jn} & e^{jn} \end{bmatrix}$$

$$= \frac{1}{3} \begin{bmatrix} e^{jn} & e^{jn} \\ e^{jn} & e^{jn} \end{bmatrix}$$

$$= \frac{1}{3} \begin{bmatrix} e^{jn} & e^{jn} \\ e^{jn} & e^{jn} \end{bmatrix}$$

$$= \frac{1}{3} \begin{bmatrix} e^{jn} & e^{jn} \\ e^{jn} & e^{jn} \end{bmatrix}$$

$$= \frac{1}{3} \begin{bmatrix} e^{jn} & e^{jn} \\ e^{jn} & e^{jn} \end{bmatrix}$$

$$= \frac{1}{3} \begin{bmatrix} e^{jn} & e^{jn} \\ e^{jn} & e^{jn} \end{bmatrix}$$

$$= \frac{1}{3} \begin{bmatrix} e^{jn} & e^{jn} \\ e^{jn} & e^{jn} \end{bmatrix}$$

$$= \frac{1}{3} \begin{bmatrix} e^{jn} & e^{jn} \\ e^{jn} & e^{jn} \end{bmatrix}$$

$$= \frac{1}{3} \begin{bmatrix} e^{jn} & e^{jn} \\ e^{jn} & e^{jn} \end{bmatrix}$$

$$= \frac{1}{3} \begin{bmatrix} e^{jn} & e^{jn} \\ e^{jn} & e^{jn} \end{bmatrix}$$

$$= \frac{1}{3} \begin{bmatrix} e^{jn} & e^{jn} \\ e^{jn} & e^{jn} \end{bmatrix}$$

$$= \frac{1}{3} \begin{bmatrix} e^{jn} & e^{jn} \\ e^{jn} & e^{jn} \end{bmatrix}$$

$$= \frac{1}{3} \begin{bmatrix} e^{jn} & e^{jn} \\ e^{jn} & e^{jn} \end{bmatrix}$$

$$= \frac{1}{3} \begin{bmatrix} e^{jn} & e^{jn} \\ e^{jn} & e^{jn} \end{bmatrix}$$

$$= \frac{1}{3} \begin{bmatrix} e^{jn} & e^{jn} \\ e^{jn} & e^{jn} \end{bmatrix}$$

$$= \frac{1}{3} \begin{bmatrix} e^{jn} & e^{jn} \\ e^{jn} & e^{jn} \end{bmatrix}$$

$$= \frac{1}{3} \begin{bmatrix} e^{jn} & e^{jn} \\ e^{jn} & e^{jn} \end{bmatrix}$$

$$= \frac{1}{3} \begin{bmatrix} e^{jn} & e^{jn} \\ e^{jn} & e^{jn} \end{bmatrix}$$

$$= \frac{1}{3} \begin{bmatrix} e^{jn} & e^{jn} \\ e^{jn} & e^{jn} \end{bmatrix}$$

$$= \frac{1}{3} \begin{bmatrix} e^{jn} & e^{jn} \\ e^{jn} & e^{jn} \end{bmatrix}$$

$$= \frac{1}{3} \begin{bmatrix} e^{jn} & e^{jn} \\ e^{jn} & e^{jn} \end{bmatrix}$$

$$= \frac{1}{3} \begin{bmatrix} e^{jn} & e^{jn} \\ e^{jn} & e^{jn} \end{bmatrix}$$

$$= \frac{1}{3} \begin{bmatrix} e^{jn} & e^{jn} \\ e^{jn} & e^{jn} \end{bmatrix}$$

$$= \frac{1}{3} \begin{bmatrix} e^{jn} & e^{jn} \\ e^{jn} & e^{jn} \end{bmatrix}$$

$$= \frac{1}{3} \begin{bmatrix} e^{jn} & e^{jn} \\ e^{jn} & e^{jn} \end{bmatrix}$$

(d) Impulse herponse

$$h(n)$$

is obtained by taking inverse  $2$  transform of  $H(2)$

...  $H(2) = \frac{1}{3} + \frac{1}{3} = \frac{1}{3} + \frac{1}{3} = \frac{1}{3}$

...  $h(n) = \frac{1}{3} + \frac{1}{3} = \frac{1}{3} + \frac{1}{3} = \frac{1}{3}$

...  $h(n) = \frac{1}{3} + \frac{1}{3} = \frac{1}{3} + \frac{1}{3} = \frac{1}{3}$

(f) gloup delay is obtained by differentiating regaling the Phase response.

Cacup delay =

$$-\frac{d}{d\omega} \left( \frac{1}{1} + \frac{1}{1} e^{i\omega} \right)$$

$$= -\frac{d}{d\omega} \left( -\omega \right) = +1$$

[1M for

each]

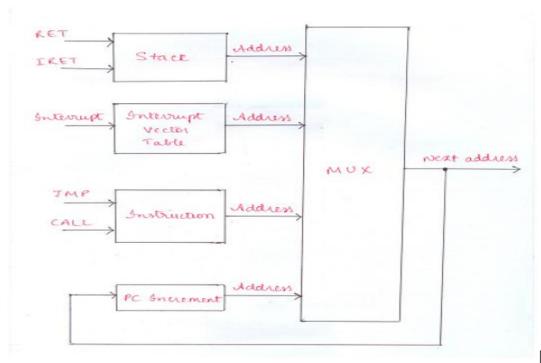

- (b) Explain the purpose of program sequencer with block diagram.

- Ans: It is a part of the control unit used to generate instruction addresses in sequence needed to access instructions. It calculates the address of the next instruction to be fetched. The next address can be from one of the following sources.

- a. Program Counter

- b. Instruction register in case of branching, looping and subroutine calls

- c. Interrupt Vector table

- d. Stack which holds the return address

The block diagram of a program sequencer is as shown [2M]

[2M]

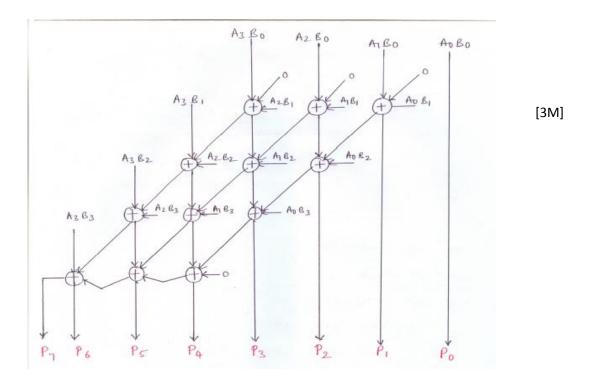

4 (a) Give the structure of a 4X4 Braun multiplier, Explain its concept. What modification is required to carry out multiplication of signed numbers? Comment on the speed of the multiplier.

Ans: The advent of single chip multipliers paved the way for implementing DSP functions on a VLSI chip. Parallel multipliers replaced the traditional shift and add multipliers now a days. Parallel multipliers take a single processor cycle to fetch and execute the instruction and to store the result. They are also called as Array multipliers.

The key features to be considered for a multiplier are:

- a. Accuracy

- b. Dynamic range

- c. Speed

The number of bits used to represent the operands decide the accuracy and the dynamic range of the multiplier. Whereas speed is decided by the architecture employed. If the multipliers are implemented using hardware, the speed of execution will be very high but the circuit complexity will also increases considerably. Thus there should be a tradeoff between the speed of execution and the circuit complexity. Hence the choice of the architecture normally depends on the application.

## Parallel Multipliers

Consider the multiplication of two unsigned numbers A and B. Let A be represented using m bits as (Am-1 Am-2 ....... A1 A0) and B be represented using n bits as (Bn-1 Bn-2 ....... B1 B0). Then the product of these two numbers is given by, [2M]

|            |            |            |          |                   | $A_3$          | $A_2$ $A_1$                   | _                 |

|------------|------------|------------|----------|-------------------|----------------|-------------------------------|-------------------|

|            |            |            |          |                   | $\mathbf{B_3}$ | $\mathbf{B_2}$ $\mathbf{B_1}$ | $\mathbf{B_0}$    |

|            |            |            |          | $\mathbf{A_3B_0}$ | $A_2B_0$       | $A_1B_0$                      | $\mathbf{A_0B_0}$ |

|            |            |            | $A_3B_1$ | $A_2B_1$          | $A_1B_1$       | $A_0B_1$                      |                   |

|            |            | $A_3B_2$   | $A_2B_2$ | $A_1B_2$          | $A_0B_2$       |                               |                   |

|            | $A_3B_3$   | $A_2B_3$   | $A_1B_3$ | $A_0B_3$          |                |                               |                   |

| <b>P</b> 7 | <b>P</b> 6 | <b>P</b> 5 | P4       | Р3                | P2             | P1                            | Р0                |

This operation can be implemented paralleling using Braun multiplier whose hardware structure is as shown in the figure

Multipliers for Signed Numbers

In the Braun multiplier the sign of the numbers are not considered into account. In order to implement a multiplier for signed numbers, additional hardware is required to modify the Braun multiplier. The modified multiplier is called as Baugh-Wooley multiplier.

Consider two signed numbers A and B,

$$\mathbf{A} = -\mathbf{A}_{m-1} 2^{m-1} + \sum_{j=0}^{m-2} \mathbf{A}_{i} 2^{i}$$

$$\mathbf{B} = -\mathbf{B}_{n-1} 2^{n-1} + \sum_{j=0}^{n-2} \mathbf{B}_{j} 2^{j}$$

[2M]

Product  $P = P_{m+n-1} \dots P_1 P_0$

$$P = A_{m-1}B_{n-1}2^{m+n-2} + \sum_{i=0}^{m-2} \sum_{j=0}^{m-2} A_iB_j2^{i+j} - \sum_{i=0}^{m-2} A_iB_{n-1}2^{n-1+i} - \sum_{j=0}^{m-2} A_{m-1}B_j2^{m-1+j}$$

Speed: Conventional Shift and Add technique of multiplication requires n cycles to perform the multiplication of two n bit numbers. Whereas in parallel multipliers the time required will be the longest path delay in the combinational circuit used. As DSP applications generally require very high speed, it is desirable to have multipliers operating at the highest possible speed by having parallel implementation.

(b) Compute the sequence in which the input data should be ordered for a 16 point DIT FFT using bit reversed addressing mode.

Ans:

$$N=16-\frac{10}{20} \text{ FFT length} = 8 \Rightarrow 1000$$

$$0000 \Rightarrow 1000 \Rightarrow 1000$$

$$1000 \Rightarrow 1000 \Rightarrow 1000$$

| Index in Binary | BCD Value | Bit reversed Index | Value in h |

|-----------------|-----------|--------------------|------------|

| 0000            | 0         | 0000               | 0          |

| 0001            | 1         | 1000               | 8          |

| 0010            | 2         | 0100               | 4          |

| 0011            | 3         | 1100               | С          |

| 0100            | 4         | 0010               | 2          |

| 0101            | 5         | 1010               | A          |

| 0110            | 6         | 0110               | 6          |

| 0111            | 7         | 1110               | E          |

| 1000            | 8         | 0001               | 1          |

| 1001            | 9         | 1001               | 9          |

| 1010            | 10        | 0101               | 5          |

| 1011            | 11        | 1101               | D          |

| 1100            | 12        | 0011               | 3          |

| 1101            | 13        | 1011               | В          |

| 1110            | 14        | 0111               | 7          |

| 1111            | 15        | 1111               | F          |

[3M]

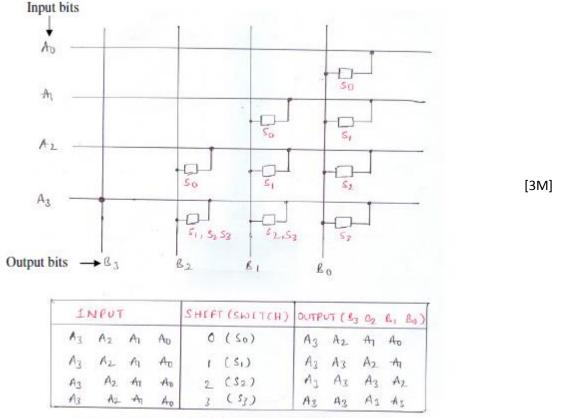

5(a) What is the role of a shifter in DSP? Explain the implementation of 4-bit shift right barrel shifter, with a diagram.

In conventional microprocessors, normal shift registers are used for shift operation. As it requires one clock cycle for each shift, it is not desirable for DSP applications, which generally involves more shifts. In other words, for DSP applications as speed is the crucial issue, several shifts are to be accomplished in a single execution cycle. This can be accomplished using a barrel shifter, which connects the input lines representing a word to a group of output lines with the required shifts determined by its control inputs. For an input of length n,  $\log_2 n$  control lines are required. And an additional control line is required to indicate the direction of the shift. The block diagram of a typical barrel shifter is as shown in figure [3M]

Fig 2.4 Implementation of a 4 bit Shift Right Barrel Shifter

Figure 2.4 depicts the implementation of a 4 bit shift right barrel shifter. Shift to right by 0, 1, 2 or 3 bit positions can be controlled by setting the control inputs appropriately.

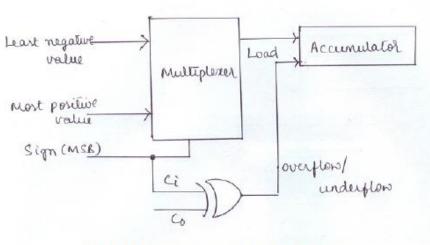

(b) Draw the schematic diagram of the saturation logic and explain the same

Ans: Overflow/ underflow will occur if the result goes beyond the most positive number or below the least negative number the accumulator can handle. Thus the overflow/underflow error can be resolved by loading the accumulator with the most positive number which it can handle at the time of overflow and the least negative number that it can handle at the time of underflow. This method is called as saturation logic. A schematic diagram of saturation logic is as shown in figure 2.7. In saturation logic, as soon as an overflow or underflow condition is satisfied the accumulator will be loaded with the most positive or least negative number overriding the result computed by the MAC unit.[2M]

Fig 2.7 A Schematic Diagram of the Saturation Logic

6(a) Explain the pointer updating algorithm for circular addressing mode.

Ans: While processing the data samples coming continuously in a sequential manner, circular buffers are used. In a circular buffer the data samples are stored sequentially from the initial location till the buffer gets filled up. Once the buffer gets filled up, the next data samples will get stored once again from the initial location. This process can go forever as long as the data samples are processed in a rate faster than the incoming data rate. Circular Addressing mode requires three registers viz

- a. Pointer register to hold the current location (PNTR)

- b. Start Address Register to hold the starting address of the buffer (SAR)

- c. End Address Register to hold the ending address of the buffer (EAR)

There are four special cases in this addressing mode. They are

- a. SAR < EAR & updated PNTR > EAR

- b. SAR < EAR & updated PNTR < SAR

- c. SAR >EAR & updated PNTR > SAR

- d. SAR > EAR & updated PNTR < EAR

; Pointer Updating Algorithm

The buffer length in the first two case will be (EAR-SAR+1) whereas for the next tow cases (SAR-EAR+1) The pointer updating algorithm for the circular addressing mode is as shown below.

Updated PNTR → PNTR ± increment If SAR < EAR. And if Updated PNTR > EAR then New PNTR → Updated PNTR - Buffer size And if Updated PNTR < SAR, then [2M] New PNTR Updated PNTR + Buffer size If SAR > EAR And if Updated PNTR > SAR then New PNTR ◀ Updated PNTR – Buffer size And if Updated PNTR < EAR then New PNTR Updated PNTR + Buffer size Else

(b) Calculate the memory addresses of the operands in each of the following cases of indirect addressing modes? In each case, what will be the content of the *addreg* after the memory access? Assume that the initial contents of the *addreg* and the *offsetreg* are 0200h and 0010h, respectively. i) ADD \*addreg ii).ADD +\*addreg iii)ADD offsetreg+, \*addreg iv) ADD \*addreg, offsetreg-

| Instruction             | Addressing<br>Mode | Operand Address | addreg Content<br>after Access |

|-------------------------|--------------------|-----------------|--------------------------------|

| ADD *addreg-            | Post Decrement     | 0200h           | 0200-01=01FFh                  |

| ADD +*addreg            | Pre Increment      | 0200+01=0201h   | 0201h                          |

| ADD offsetreg+,*addreg  | Pre_Add_Offset     | 0200+0010=0210h | 0210h                          |

| ADD *addreg, offsetreg- | Post_Sub_Offset    | 0200h           | 0200-0010=01F0h                |

[1M for each]