## CMR INSTITUTE OF TECHNOLOGY

|  | USN |  |  |  |  |  |  |  |  |  |  |

|--|-----|--|--|--|--|--|--|--|--|--|--|

|--|-----|--|--|--|--|--|--|--|--|--|--|

|       |                       | Interna   | l Asses    | ssment T      | est Il | [ –Nov. | 201   | <u>6</u> |                             |

|-------|-----------------------|-----------|------------|---------------|--------|---------|-------|----------|-----------------------------|

| Sub:  | Computer Organization |           |            |               |        |         | Code: | 15CS34   |                             |

| Date: | 03/<br>11/2016        | Duration: | 90<br>mins | Max<br>Marks: | 50     | Sem:    | III   | Branch:  | 3A&B-<br>ISE,<br>3C-<br>CSE |

Note: Answer any five questions:

- Explain Sequential multiplication algorithm? Perform sequential multiplication for M=1001 and Q=1111. (5M+5M=10M)

- Perform the operation of division using Restoring and Non Restoring method on the following pairs of numbers where X is the divisor and Y is the dividend X=0101, Y=11111. (5M+5M=10M)

- Perform the operation of multiplication using Booth algorithm and bit pair recording on following pair of numbers where M=01001 and Q=01111. (5M+5M=10M)

- 4. Represent the following floating point number in single and double precision format (5M+5M=10M)

a)1.725 b)-25.125

5a. A computer has L1 and L2 caches. The cache block consists of 8 words. The hit rate is 0.95 for both

Caches. the time required to access an 8 words block in L1 cache is 1 cycle and in L2 cache is 10

cycles. Time needed to access L1 cache is 1 cycle, L2 cache is 10 cycles and main memory is 50

cycles. Calculate the average access time experienced by the processor. (6M)

5b. Bring out the comparison between different mapping function techniques (4M)

6. Write a short note on a) PCI Bus b) SCSI Bus (5M+5M=10M)

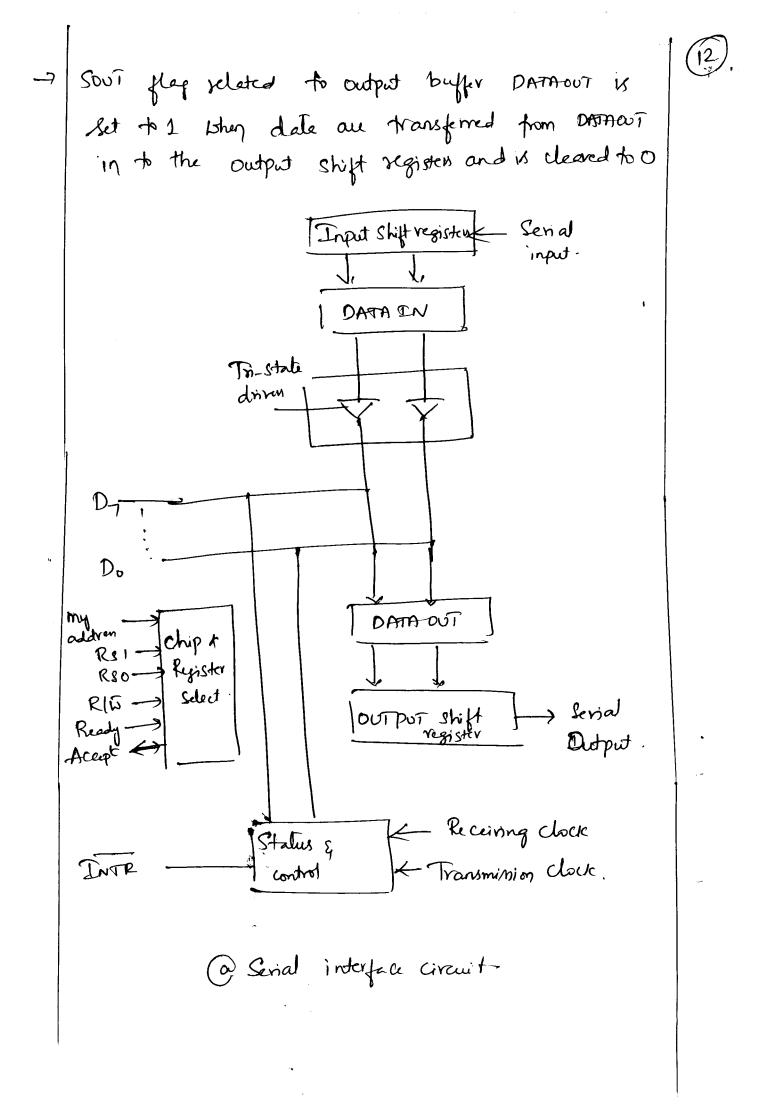

7. With a neat diagram explain serial interface Device. (10M)

$$I = \frac{1}{100} \frac{1}{100}$$

1111 1111 0 D てして 0111 0000 (()) 1 1000 0111  $\bigcirc$ Product. Perform the operation of division using Restoring 2) and non restoring method on the following pair of numbers Using, where X is the divises and Y is the dividend X = 0101, Y = 111115x1-5m Restoring R A [[]]] 000000 00000 | LS 111011 Add 20 9 111100 11110 ALLA 000101 00000 ( 1110 2] 000011 1110]] 111011 Add 23 9 M 11110 11100 Ad M 000101 11100 000011 LS 11 001 000 111  $\left( \left( 10^{\prime}\right) \right)$ 110011 0,000,0

00010) 000011 111000 0 00 010 And M2 1001 1, ls 000000) quetient feminder

3) Perform the operation q multiplication using

Booth algorithm and bit pour viewsching m the

following pair q numbers where M=01001 and

$$Q = 01111$$

$M = 0 + 00 + (+9) = 0 = 01111 (+15)$

Recaded Multiplier +1 0 0 0 -1

$0 + 0 = 0 -1$

$1 + 1 + 1 + 1 + 1 + 2$ 's complement ?

$0 = 0 = 0 = 0 = 1$

$1 + 1 + 1 + 1 + 1 + 1 = 2$ 's complement ?

$0 = 0 = 0 = 0 = 0 = 1$

$1 + 1 + 1 + 1 + 1 = 2$ 's complement ?

$0 = 0 = 0 = 0 = 0 = 1$

$0 + 0 = 0 = 1 + 1 = 2$ 's complement ?

$0 = 1 = 0 = 0 = 1 + 1 = 2$ 's complement ?

$0 = 1 = 0 = 0 = 1 + 1 = 2$ 's complement ?

Multiplier  $0 = 1 + 1 = 0 = 0 - 1$

$0 + 0 = 0 + 1 = 0 = 0 - 1$

$0 + 0 = 0 + 1 = 0 = 0 - 1$

$0 + 0 = 0 + 1 = 0 = 0 - 1$

$0 + 0 = 0 + 1 = 0 = 0 - 1$

$0 + 0 = 0 + 1 = 0 = 0 - 1$

$0 + 0 = 0 + 1 = 2$ 's complement ?

$0 + 0 = 0 + 1 = 0 = 0 - 1$

$0 + 0 = 0 + 1 = 2$ 's complement ?

$0 + 0 = 0 + 1 = 0 = 0 - 1$

$0 + 0 = 0 + 1 = 0 = 0 - 1$

$0 + 0 = 0 + 1 = 0 = 0 - 1$

$0 + 0 = 0 + 1 = 0 = 0 - 1$

$0 + 0 = 0 + 1 = 0 = 0 - 1$

$0 + 0 = 0 + 1 = 0 = 0 - 1$

$0 + 0 = 0 + 1 = 0 = 0 - 1$

$0 + 0 = 0 + 1 = 0 = 0 - 1$

$0 + 0 = 0 + 1 = 0 = 0 - 1$

$0 + 0 = 0 + 1 = 0 = 0 - 1$

$0 + 0 = 0 + 1 = 0 - 1$

$0 + 0 = 0 + 1 = 0 - 1$

$0 + 0 = 0 + 1 = 0 - 1$

$0 + 0 = 0 + 1 = 0 - 1$

$0 + 0 = 0 + 1 = 0 - 1$

$0 + 0 = 0 + 1 = 0 - 1$

$0 + 0 = 0 + 1 = 0 - 1$

$0 + 0 = 0 + 1 = 0 - 1$

$0 + 0 = 0 + 1 = 0 - 1$

$0 + 0 = 0 + 1 = 0 - 1$

$0 + 0 = 0 + 1 = 0 - 1$

$0 + 0 = 0 + 1 = 0 - 1$

$0 + 0 = 0 + 1 = 0 - 1$

$0 + 0 = 0 + 1 = 0 - 1$

$0 + 0 = 0 + 1 = 0 - 1$

$0 + 0 = 0 + 1 = 0 - 1$

$0 + 0 = 0 + 1 = 0 - 1$

$0 + 0 = 0 + 1 = 0 - 1$

$0 + 0 = 0 + 1 = 0 - 1$

$0 + 0 = 0 + 1 = 0 - 1$

$0 + 0 = 0 + 1 = 0 - 1$

$0 + 0 = 0 + 1 = 0 - 1$

$0 + 0 = 0 + 1 = 0 - 1$

$0 + 0 = 0 + 1 = 0 - 1$

$0 + 0 = 0 + 1 = 0 - 1$

$0 + 0 = 0 + 1 = 0 - 1$

$0 + 0 = 0 + 1 = 0 - 1$

$0 + 0 = 0 + 1 = 0 - 1$

$0 + 0 = 0 + 1 = 0 - 1$

$0 + 0 = 0 + 1 = 0 - 1$

$0 + 0 = 0 + 1 = 0 - 1$

$0 + 0 = 0 + 1 = 0 - 1$

$0 + 0 = 0 + 1 = 0 - 1$

$0 + 0 = 0 + 1 = 0 - 1$

$0 + 0 = 0 + 1 = 0 - 1$

$0 + 0 = 0 + 1 = 0 - 1$

$0 + 0 = 0$

4) Reprosed the following floading point numbers in

Single and double precision format.

(a)

$$1.72.5$$

.

$1.101110 \times 2^{\circ}$

$S=0$   $M = 10111001820$ ,  $E=0$

Single preusion).

$E^{1} = E + 127$

$0 + 127 = 127 = 111111$

$S = 0$ ,  $E \circ$ ,  $M = 10111001$

$E^{1} = E + 127$

$0 + 127 = 127 = 111111$

$S = C = M$

$double precision$

$E^{1} = E + 1023$

$= 0 + 1023 \Rightarrow 111111111$

$[0] 111111111 | 10111001$

(b)  $-2.5.125$

$25 = 11001$

$.125 = 001$

$ds.125 = 11001.001$

Normalized form  $\Rightarrow 1.1001001 \times 10^{9}$

$Single precision  $\frac{1}{2} 10000011 | 1001001$$

•

| 52)  | Bring out the<br>Junction technic                                                                          | companision between<br>juis                                                                                 | different mapping (8)                                                                                                                                         | )<br>) |

|------|------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| (ª)  | Direct Mapping<br>Each: block from<br>the main memory<br>has only one<br>Possible location<br>in the cache | Associative mepping<br>A block of date<br>from memory can<br>be placed in to<br>any cache block<br>Position | Set associative<br><u>Mapping</u> .<br>A block of date<br>from main<br>memoly can go<br>into a particuler<br>block location of<br>any direct-mapped<br>Cache. |        |

| (*)  | Aleeds only one<br>Companision                                                                             | Needs companision<br>with all tay bits                                                                      | Needs number<br>of Comparisions<br>equal to number<br>g blocks per<br>set.                                                                                    |        |

| (د ) | Main memory address<br>is divided in to<br>3 fields.<br>TAG, Block & WORD                                  | Main memoly address<br>is divided in to<br>two fields<br>TAG & WORD                                         | Main memory<br>addren is<br>divided in to<br>3 fields<br>TAG, SET KWORD.                                                                                      |        |

| (d)  | ) Scarching time is<br>les                                                                                 | Searching time is<br>mole                                                                                   | Searching time<br>increases with<br>number 9<br>blocks per Set.                                                                                               |        |

|      |                                                                                                            |                                                                                                             |                                                                                                                                                               |        |

6. Write a short note of a PCI BUS 6) SesI bus. PCI BUS 5x1=5M Peripheral component Inter conject Bus PCI BUS Supports the functions in a standardi format independently of any procend. 3ed It is a low cost 32/64-bit bus having plug and play feature for conjecting Ilo denus PCI BUS is defined for operation with either 5V or 3.3V power supply. PCI BUS is basically designed to support this burst mode of operation PG BUS Supports three independent address spaces: memory, I/o and configuration. Here A Master ( procenos or DMA controller) is called an Initiator in PCI terminology, The addressed device which responds to read and write commands is called target A complete transfer operation on the bus, involving an address and busit of date is called a transaction,

\_ \_\_ \_\_ \_\_

----

- ----

SCSI standard provides a mechanism meded to (n) $\rightarrow$ establish a logical conjection and exchange menages between two controller. SCSI Standard depyes the structure and contents  $\rightarrow$ of Various types of packets that the controller exchange to handle different situations, The initiator uses the packets to send the commands it receives (from the procens) to the target. The target responds with status information and data transfer operations. with a neat diagram explain serial interface 4) 10x1=10 Device Senial port is used to conject the procend to  $\rightarrow$ Ilo derives that require transmission of data one bit at a time. Serial Interface circuit is communicating -> The in bit senal way of the device side and in bit parallel format on the bus side When all S-bits of date are received, the contents of the shift register are transferred to DATAIN register, in parallel. The status flag SIN is set to I liken new date are loaded in DATAIN; it is cleared to O When the procend reads the contents of DATAEN