#### CMR INSTITUTE OF TECHNOLOGY

#### Internal Assessment Test 1 – Sept. 2016

| Sub:  | Fundamentals  | of CMOS VL | SI      |            |    |      |                 | Code:   | 10EC56                      |

|-------|---------------|------------|---------|------------|----|------|-----------------|---------|-----------------------------|

| Date: | 08/ 09 / 2016 | Duration:  | 90 mins | Max Marks: | 50 | Sem: | 5 <sup>th</sup> | Branch: | ECE (A,B, C<br>D) TCE (A,B) |

**Note:** Answer any five questions.

- 1 With neat sketches explain the behaviour of n-channel MOSFET enhancement mode device under [10M] the influence of different terminal voltages.

- 2 a) List the expression for threshold voltage of an NMOS transistor and narrate the significance [4M+6M] of each term in this equation.

- b) Calculate the threshold voltage with  $\epsilon_{si}=11.7\epsilon_o$ ,  $\epsilon_{ox}=3.9\epsilon_o$  for an nMOS transistor with  $N_A=2\times\frac{10^{17}}{cm^3}$ ,  $t_{ox}=190^\circ A$ . Assume  $\phi_{ms}=-0.85$ ,  $Q_{fc}=0$  C,  $N_i=1.45\times\frac{10^{10}}{cm^3}$ .

- 3 a) What is noise margin? Obtain the values of V<sub>IL</sub>, V<sub>IH</sub>, V<sub>OL</sub> and V<sub>OH</sub> from transfer [4M+6M] characteristics of a typical inverter.

- b) In a 0.5 $\mu$ m process  $\mu_n = 44.69 \times \frac{10^{-3}m^2}{V-sec}$ ,  $t_{ox} = 14.1nm$  and the  $\left(\frac{W}{L}\right) = \frac{30}{5}$ . The nMOS has  $V_t = 0.71V$  and  $V_{gs} = 1.5V$ . At what levels of  $V_{ds}$  and  $I_d$ , will the MOSFET reach pinch-off mode? Hint:  $(\epsilon_{ox} = 3.9\epsilon_o)$

- 4 Derive MOSFET current equation in different regions of operation.

[10M]

| 5 | Write a short notes on i) Differential inverter, ii) saturated load inverters.                                                                                                                                                                                                                  | [5M+5M] |

|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| 6 | Explain the NMOS fabrication process with neat sketches? Write the steps involved in production of E-beam masks.                                                                                                                                                                                | [7M+3M] |

| 7 | Explain the CMOS inverter transfer characteristics highlighting the region of operation of the MOS transistor. Derive the relationship between $V_{in}$ and $V_{out}$ for Region C? Explain the effects of $\beta_B/\beta_B$ ratio variations on the transfer characteristics of CMOS inverter. | [6M+4M] |

[5M+5M]

Write a short notes on i) Body Effect, ii) Channel length modulation.

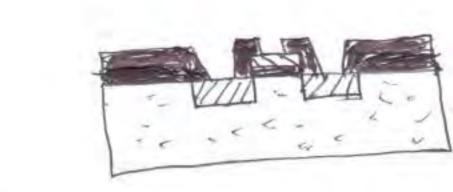

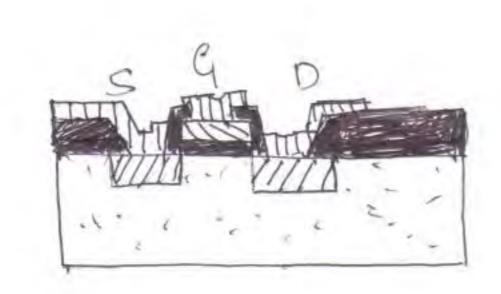

① With much sketches explain the behaviores of on-channel MosfeT enhancement mode device under the influence of different terminal voltages. — 10 marles — Source. Gale polysilicon. — Sioz. (Gale onide).

Substrate

Figure (1) shows the cross sectional structure of n-MOSFET. Starbing material p-type semiconductor called substrate in which too nt-regions are formed using diffusion process called source and drain. Source and drain are separated by small distance called channel. This channel is covered by a thin layer of silicon dioxide. On top of which a layer of poly expalling silicon is deposited.

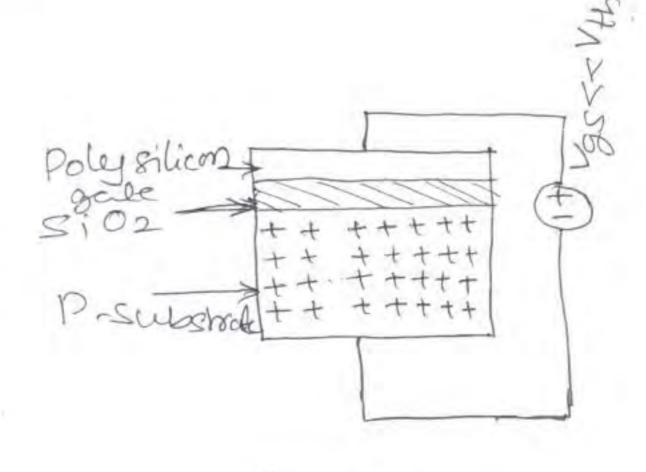

when gate to sonace voltage is very much smaller than theadold voltage i.e., Vers KVH, mobile positive holes in are distributed throughout the p-type silicon substrate. This is shown in figure (2). This is termed as accumulation mode.

fig (2). Accusorula

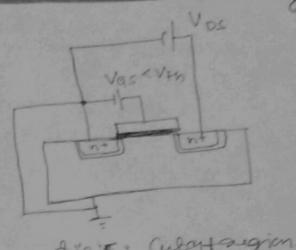

As Vgs is aresed above 4th in EVES= VE Potential, the holes are sepelled causing a deplilion region under + ++++ + + + + + the gate. Now the structure is +++++ ++++ in depletion mode as shown in Dig (3): Depublion mode Dignal 3. Raising Ver above Vin results E Vas >Vth in electrons being attracted invasion to the oregion of the substrate under the gate. A conduction guegion-Depletion +++++ bredion layer of the electrons in the p-substrate gives size to the name invession made Dig(4): Inversion Shown in big (A). 05 males In an inversion layer substrale junction the n-type layer is indeced by the electric field to applied to the gale. This junction, instead of being metallurgical. Junction 11 a dield effect junction

less than theeshold voltage.

i.e., Vas < Vth, there is

no channel formation. Hence no

these areand blows believes source

and deain. The Mosfet 18 Raid

to be operated in another aregion.

The Mosfet structure is as

shown in Dignae. 5.

Avith gale to sonace voltage.

greater than theeshold voltage.

and deain to sonece voltage.

i.e., Vas > Vth , Vos > 0

such that Vas - Vth > Vos

too electrical fields are arealed.

within the device. They are

Vertical component deer to Vas

and how responsible for carelisms

enhancement g ble channel

enhancement of the chainnest and horizontal component of the field deep to Vos responsible for sweeping the electrons in the channel town the source towards the electrons in the channel town. The structurae is deain results in flow of charent. The structurae is as show in figure 6. The device is said to be operated

En linear or noncalnaaled acquer. Joelenoageaegion ale source end

In linear oregion, the voltage within the channel is,

Vers - Vth > VDS Vers - Vth > VDS Vers > Vth

depetion n type chand layer (inversion layer)

dig 6 : Lineaa segion

But at deain end decine vettegreite fattgreffective only difference between decine gale and drain voltage is effective flure Vas -Vth > Vos - Vs Vs - Vth > Vos - Vs Vs - Vth > Vos - Vs Vs - Vth > Vos - Vs Vth

· Vap > Vto

Huna in linear monsaharated algion channel will acach from source to drain algion. Increased drain to source voltage changes the shape of channel due to VDS>0 also street drop along the channel.

with Vers > Vth and Vos>0.

Such that Vers-VHX VDS

the device is said to be operated in solannaled oregion.

At the drawn and the effective veoldage is

Vas -Vth < VDS Va- Vs -Vth < VD- /s

Vg-VD < VH

VGOK V+10

Gale to deain voltage is less than the theeshold voltage. There channel will no longer neach. The deain diffusion negion. Flure channel is said to be penched of. awarent will no longer increases with Increase in the deain to source voltage. Conduction is brough about by drift mechanism 3 electrons cender the influence 3 positive deavin voltage.

depletion Pinchat layer

big of: Saburation

As the electrons leave the channel they are injected 3 into the dyain depletion region and set are subsequently accelerated toward the drain.

Voltage across the pinched off sugion channel timed at ug vas-V+n. auraene is independent y vos boil dépendent on Vgs-44. The strachuse in saluation is elsown in dignal 7.

- 05 masks

List the expression boar threshold voltage with Copes of an NMOS transistor and narrale the. 2 igniticance of each term in this equalion.

Threshold voltage is defined as the voltage. applied below the gate and source gan.

Mos device below which the danin to source. current drops to zero.

Sty-Voth-mos & Sto.

V+h= \$ms - Afc + ab + 2\$b.

of ms = metal to semiconductor woork bundton difference dons = -0.9 don nt gate oncen p-substrate. Oms=-0.2 dos nt gale over n-Substrale.

Orb= \12965iNA245 called bulk charge. Q= charge qan electron = 106x104c. Esi=11. Feo= Pornittivity & chedesilicon NA = Acceptor bopanes density.

- 62 mades

\$ = bulk potential = KT ln (NA) or. involts k=1.38×10-23 J/K= Bollgmann Constant T = Temperaleure in °k.

Ni = Intrinsic carrier concentration = 1.05 × 10°/cm³ al 300° k. Go = Absolute premitivity = 8.854x1014 Plan. Con = for = gale oxide capacitance pur unit area. Cox=3.9 co= premitivity of silicondioxide. tox= thickness of the gale oxide. 02 marles Calculade the threshold voltage with Esi = 11.760, Gox = 3.960 for an nMos transista with NA = 2×1017 cm² tox=190Å. Assume frns=-0.85, 94c=0c, Ni=1.usxido/cm3 V+h=200+ ab - afc + 0ms >0 Since af 20 Wth= 200 + ab + pms ton= 190×10-10 m = 190 X10 10 X102 cm

tox = 190 x 108 cm

26

dms=-0.85 Ofc=OC. N; = 1. US x 10 0 (cm3 NA = 2 × 1017/cm3 GDX=3.9 GD E8 = 11-7 60 60=8.854 x 10 14 flory tox=190A=190x1010m le proposition

At T=200°K

$$\phi_{b} = \frac{kT}{qy} \ln \left( \frac{NA}{Ni} \right)$$

$$\phi_{b} = \frac{1.38 \times 10^{23} \times 200}{1.6 \times 10^{19}} \ln \left( \frac{2 \times 10^{17}}{1.45 \times 10^{10}} \right)$$

$$\frac{1}{1.6 \times 10^{19}} \ln \left( \frac{2 \times 10^{17}}{1.45 \times 10^{10}} \right)$$

$$\frac{1}{1.6 \times 10^{19}} \ln \left( \frac{2 \times 10^{17}}{1.45 \times 10^{10}} \right)$$

$$\frac{1}{1.6 \times 10^{19}} \ln \left( \frac{2 \times 10^{17}}{1.45 \times 10^{10}} \right)$$

$$\frac{1}{1.6 \times 10^{19}} \ln \left( \frac{2 \times 10^{17}}{1.45 \times 10^{10}} \right)$$

$$\frac{1}{1.6 \times 10^{19}} \ln \left( \frac{2 \times 10^{17}}{1.45 \times 10^{10}} \right)$$

$$\frac{1}{1.6 \times 10^{19}} \ln \left( \frac{2 \times 10^{17}}{1.45 \times 10^{10}} \right)$$

$$\frac{1}{1.6 \times 10^{19}} \ln \left( \frac{2 \times 10^{17}}{1.45 \times 10^{10}} \right)$$

$$\frac{1}{1.6 \times 10^{19}} \ln \left( \frac{2 \times 10^{17}}{1.45 \times 10^{10}} \right)$$

$$\frac{1}{1.6 \times 10^{19}} \ln \left( \frac{2 \times 10^{17}}{1.45 \times 10^{10}} \right)$$

$$\frac{1}{1.6 \times 10^{19}} \ln \left( \frac{2 \times 10^{17}}{1.45 \times 10^{10}} \right)$$

$$\frac{1}{1.6 \times 10^{19}} \ln \left( \frac{2 \times 10^{17}}{1.45 \times 10^{10}} \right)$$

$$\frac{1}{1.6 \times 10^{19}} \ln \left( \frac{2 \times 10^{17}}{1.45 \times 10^{10}} \right)$$

$$\frac{1}{1.6 \times 10^{19}} \ln \left( \frac{2 \times 10^{17}}{1.45 \times 10^{10}} \right)$$

$$\frac{1}{1.6 \times 10^{19}} \ln \left( \frac{2 \times 10^{17}}{1.45 \times 10^{10}} \right)$$

$$\frac{1}{1.6 \times 10^{19}} \ln \left( \frac{2 \times 10^{17}}{1.45 \times 10^{10}} \right)$$

$$\frac{1}{1.6 \times 10^{19}} \ln \left( \frac{2 \times 10^{17}}{1.45 \times 10^{10}} \right)$$

$$\frac{1}{1.6 \times 10^{19}} \ln \left( \frac{2 \times 10^{17}}{1.45 \times 10^{17}} \right)$$

$$\frac{1}{1.6 \times 10^{19}} \ln \left( \frac{2 \times 10^{17}}{1.45 \times 10^{17}} \right)$$

$$\frac{1}{1.6 \times 10^{17}} \ln \left( \frac{2 \times 10^{17}}{1.45 \times 10^{17}} \right)$$

$$\frac{1}{1.6 \times 10^{17}} \ln \left( \frac{2 \times 10^{17}}{1.45 \times 10^{17}} \right)$$

$$\frac{1}{1.6 \times 10^{17}} \ln \left( \frac{2 \times 10^{17}}{1.45 \times 10^{17}} \right)$$

$$\frac{1}{1.6 \times 10^{17}} \ln \left( \frac{2 \times 10^{17}}{1.45 \times 10^{17}} \right)$$

$$\frac{1}{1.6 \times 10^{17}} \ln \left( \frac{2 \times 10^{17}}{1.45 \times 10^{17}} \right)$$

$$\frac{1}{1.6 \times 10^{17}} \ln \left( \frac{2 \times 10^{17}}{1.45 \times 10^{17}} \right)$$

$$\frac{1}{1.6 \times 10^{17}} \ln \left( \frac{2 \times 10^{17}}{1.45 \times 10^{17}} \right)$$

$$\frac{1}{1.6 \times 10^{17}} \ln \left( \frac{2 \times 10^{17}}{1.45 \times 10^{17}} \right)$$

$$\frac{1}{1.6 \times 10^{17}} \ln \left( \frac{2 \times 10^{17}}{1.45 \times 10^{17}} \right)$$

$$\frac{1}{1.6 \times 10^{17}} \ln \left( \frac{2 \times 10^{17}}{1.45 \times 10^{17}} \right)$$

$$\frac{1}{1.6 \times 10^{17}} \ln \left( \frac{2 \times 10^{17}}{1.45 \times 10^{17}} \right)$$

$$\frac{1}{1.6 \times 10^{17}} \ln \left( \frac{2 \times 10^{17}}{1.45 \times 10^{17}} \right)$$

$$\frac{1}{1.6 \times$$

Vth = 1.306 Volts

1/2 magles

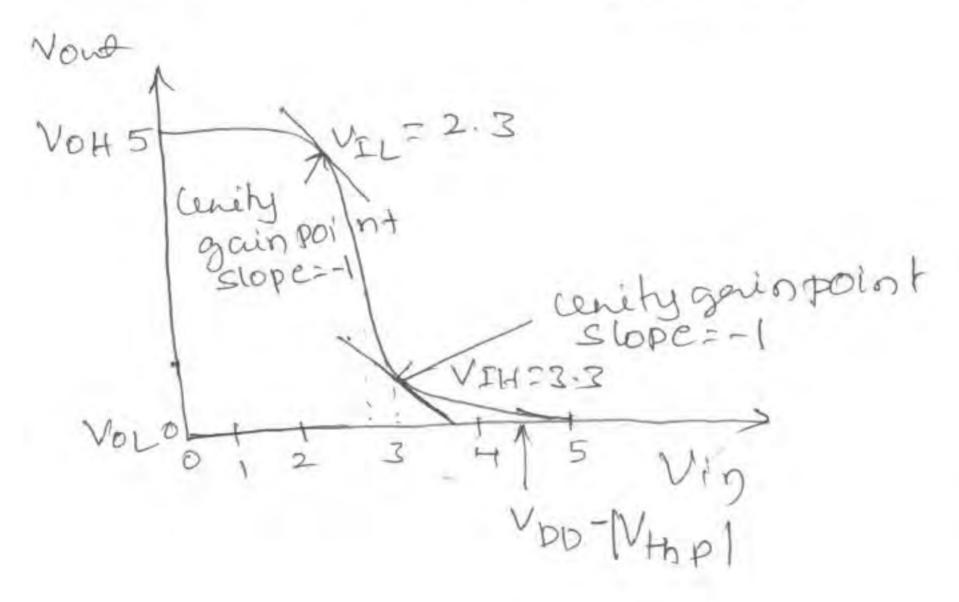

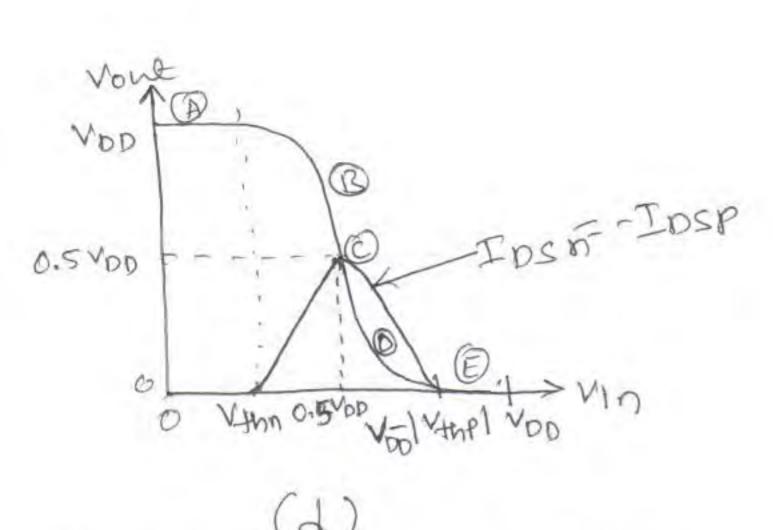

- 30 what is noise margin? Obtain the values of VIL, VIH, VOL and VOH Drown transfer characheristice of a typical inverter.

- -> Noise margin is a parameter that allows to determine the allowable noise vollage on the infinit g a gate. So that the onlyne will not be all affected.

Low noise meagin NML is debined as the difference in the magnitude of between the maximum low output voltage of the driving gate and the maximum input low voltage necognized by the daiven gate

i.e., NML= | VILOMAN - VOLMAN |

High moise menagin NMH is defined as the different in bragnitude between minimum high oneput voltage of the driving gate and the minimum input high voltage arecognized by the driven gate.

i.e., NMH = | VIHmin - VOHmin].

VIHMIN = oninimum high loopul voltage

VILMAN = maximum Low loopul voltage

Voltage

Voltage

Voltage

Voltage

Voltage

Voltage

VIH = VIL is decircable means transfer characheristic (5) should switch aborephty acquires high gain in the transition origin.

VIL is found de by debarmining the unity gain point in the inventor transfer characteristic.

VIL is in suggion 13 of inventor suggestion operation

Similarity VIH is found using unity gain point.

History and is in suggion 18 0 of inventor operation.

Found that VIL = 2.3, VIH = 3.3

2 marles

36 In a 0.5 pers process per= uu.69×10-3 m2, lox 21 h.1 nm and the 10 = 30. The omos has Vto= 0.7 Ivand Vas=1.5V. At what levels of vos and Ios, will the Mosfet greach pinch go mode? (Hint: Gox= 3.960) - 06 masles ton= 14.1 nm -> Jen= 44.62×103 m2 = 16.1 × 109 m = 1 (4.1 × 10 -9 × 102 cm) tox= luolnon tox = 10.1 × 10-7 cm) 2 = 30 Vth = 0.71 V for pinch of to occur Vas=1.5V-VDS = VDSSal = VGS-VHb = 1.5-0.71 60x=3.960. Vpscat = 0.79V The ansent in pinchat mode is given by Tos. = Men Cox 10 (Vas - V4h)2  $Cox = \frac{Gox}{tox} = \frac{3.960}{14.1 \times 10^{-7}} = \frac{3.9 \times 8.85 \times 10^{-14}}{14.1 \times 10^{-7}}$ Cox = 2. uu x 10 7 F/cm2. 1000 0 100 100 300 100 300 VESC Terres Carellebaxio 3x 10 2x 10 cmx.

pln = 44.63 × 10 -3 m2/V-sec. m2= mxm pln = uu. 63 x 153 x 104 cm² / V-sec = 102 cm × 102 cm = 100 cm2 len = uu. 63 X10 cm/V-sec :. IDS = UU.63 × 10 × 2. UUX 10 7 × 30 [1.5 - 0.7] 2. IDI= 2.038x10-4=0.207mAmp.

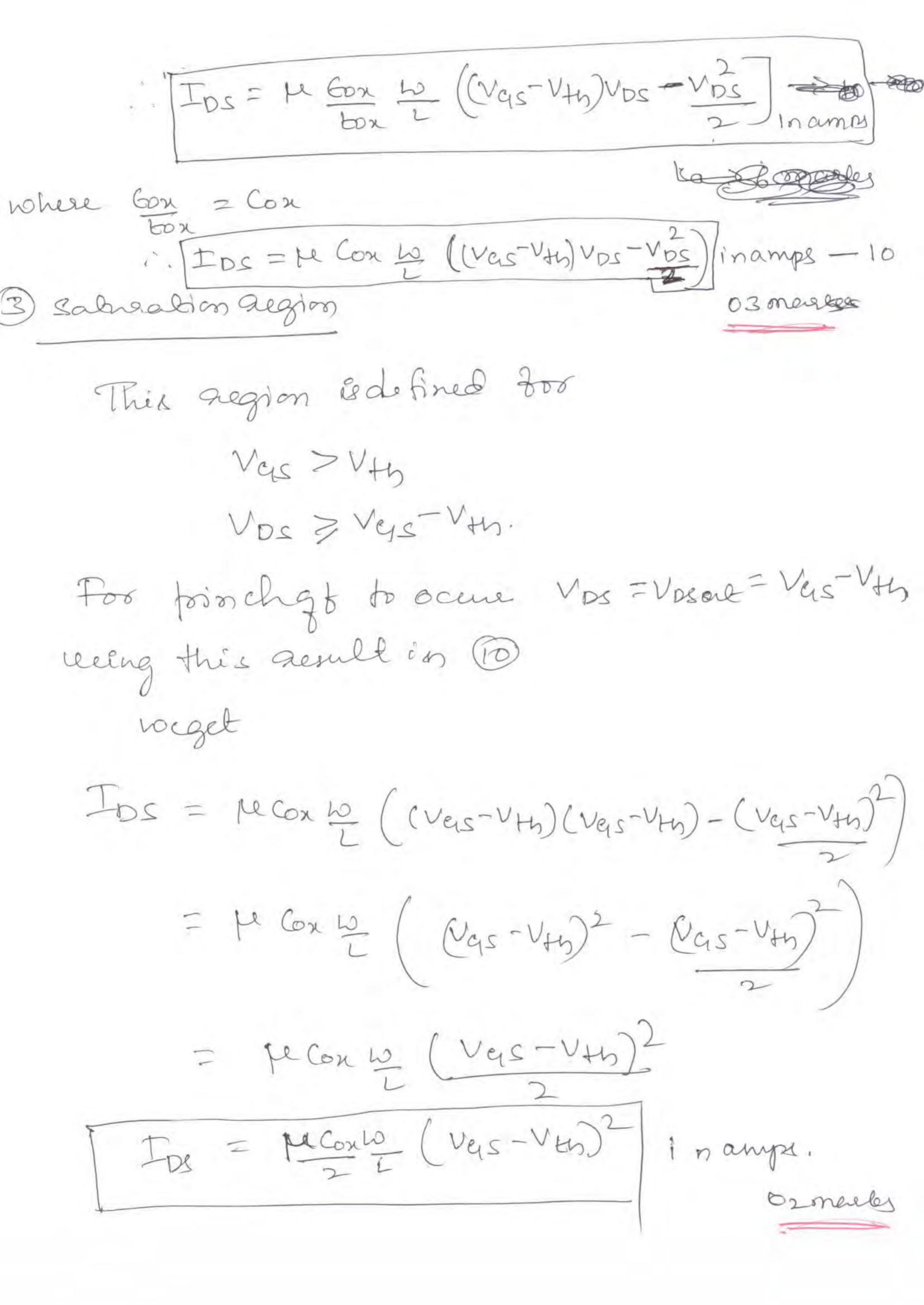

- (4) Derive Mosfet current equation in different programs a operation.

- There are three negions of operations bor MOSFET. They are

- 1 cut of bregion.

- D Linear non calmation unsalvaled origion.

- (3) Sabralion sugion-

this aegion is defined by Verskyth 1. d., Sale to soughe voltage its less tylan threehold to Hage. Due to this chambelies not extablished/hence/current blow belooks source and deain is zero. i.e., IDS = 0. Los mades

#### 1) cut q j'oregion:

This sugion is defined box gale to source Voltages less than theeshold voltage i.e., Vas < Vth.

In this again there is no channel enhancement betoreen sonace to deain. Hunce there is no current blow brom drain to cource.

Flence IDS =0.

> 02 masks

De lange negion from salked francolod francolod

The anglos is defined Ediona foronsal and formsal and anyon

As Vas > Vth and VDS > 0.

i.e., Gale la source vollage greater than threshold voltage Vth and Leain to source vollage greater than Tero, thannel is cetablished and econicas Starts moving blowing from sonace to drawn hence conventional current blows from drawn to sonece

:. IDS = - ISD = Charge induced in channel (Ac) Electron transit time(2)

fe -> mobility à carriers

EDS -> Electric bill betocen danin to source.

VDS = Voltage between drain to source

Substitule @ in 3.

Substitule (5) in (2)

. 63 males

## Linear mon sabrealed region

Charge induced in the channel deer to gate to source voltage greater than threshold voltage i.e., Vous >V+h

Voltage in the channel varies linearly with distance from source due to IR drop in the channel

In Linear gregion Vgs-V+b>Vps.

At source end the voltage with in the channel is vas-Vth. As That is deain effect due to. deain to source voltage at source end is completely

As the distance from source increases towards deain negron the deain to source vollage effects become significant.

So the average voltage within the channelis

Leving

$$\oplus$$

in  $\otimes$

$Eq = \frac{Vq}{box}$

$Eq = (Vqs - Vth - Vos)$

$Eq = (Vqs - Vth - Vos)$

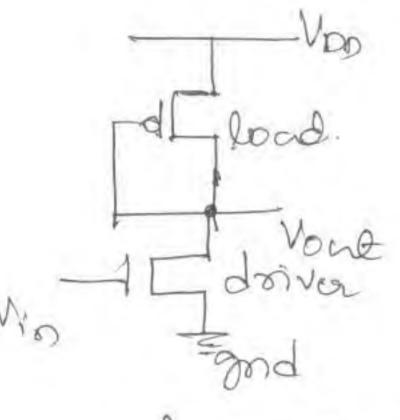

5) Write a short notes on

(1) Diffraential inverter

(ii) Sabnaded load inverturs.

- 5 marly

- 5 marles

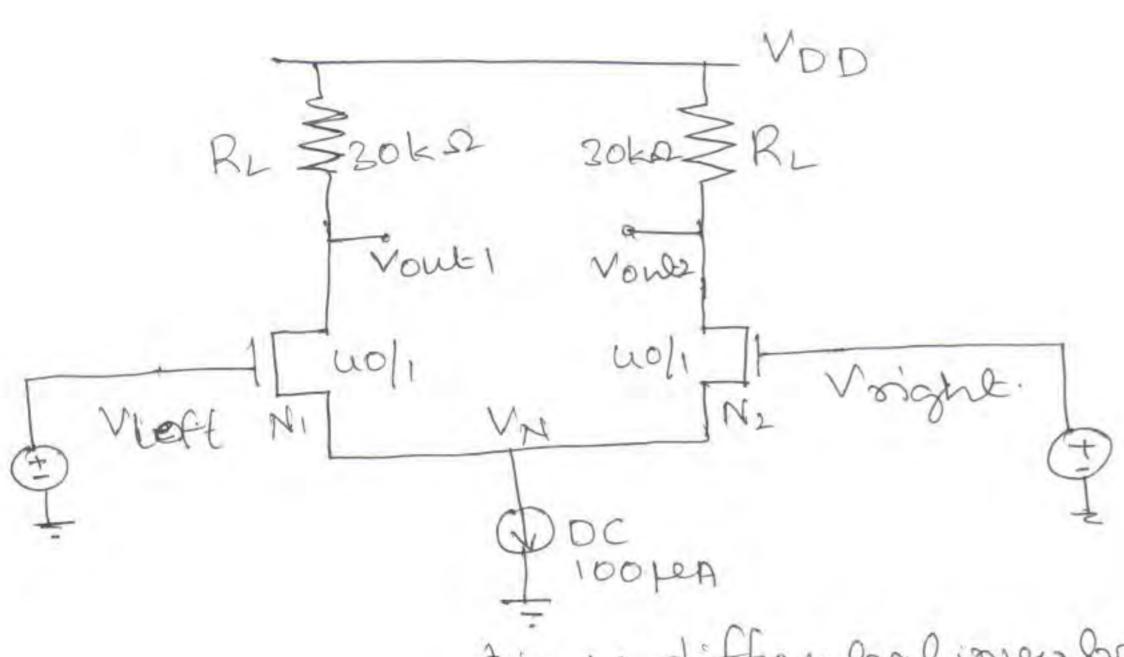

(i) Differential inverter

Dig 1: diffrantalionenter circuit

An inverter that uses two differential inputs and produce two differential operates is called differential inventor. The circuit diagram is shown in tignas i. whichevers two verieties load, two most transistors whose source is commoned and connected to curaent source that is in their connected to ground. Drains of two mass transistors.

> (Dos)

..

When Vieft, Vright once set la same vollage Vquiscent then each brancisto hers a Vas of Vaciscent - VN.

VN is the voltage across current sonace

Ips in each toansistor is equal and Vone = Vonez. . Applying common signale to both inputs therefore. queulle in no gain. This gain is called common mode opios

Diffrential modegain: If Vseft is maised by BV and Voight is lowered by &v, then current in N, increased by SI and current in N2 will decrease by SI. Vone, Edecrease by SIRS Vonez increase by SIR.

. Differential gain from Vlegt to Vone, is Adiff = 2 SIR = SIR

Adiff = -SmR.

Differential gain nexulted broom applying a differential signals to the impuls.

Common mode rejection autimo: It is the autility Common mode gain and differential gain.

CMRR = Diffreenbial gain Common modegain.

- 3 marle

digner 2; Josphe onlyne chara driches of diffundal

Figure 2 shows the imput onlynt characteristics of differential invester for different values of total charmed widths of MMOSPET.

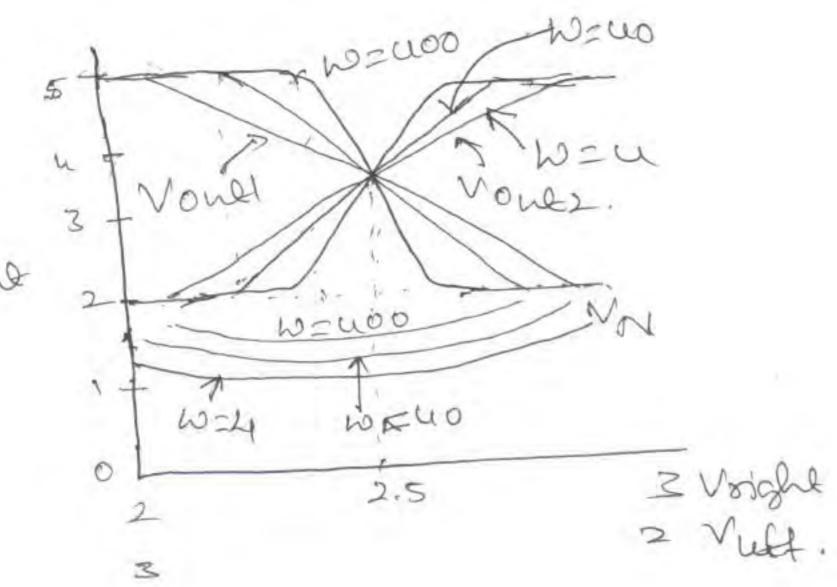

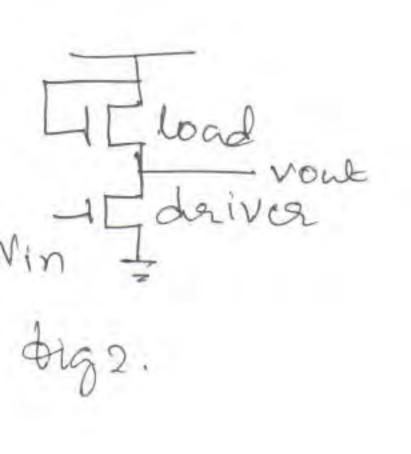

## Saturated load invalues.

Vin I

Dig 1. Generic circuit g salvaled load invalaSalvanted load inventor consists of an nmos deiver transistro whose gate is did with input lignal. The load is a constant current so wase as show in bigure O.

Figure 2 Shows a sabraadion load inverted in which current source in figure a most inverter whose gate is permanently connected to Drain. Hence load toansistor operates in sabraadion pregion because Vostoad > Vastoad - Vthroad.

Output its always looked by one threshold by VDD. when Vink Vthaliver.

The input onepul characteristice are as shown in together tigure (2).

It has small low noise margin makes this inverte nonophimal as a conventional logic circuit.

are forefraged.

fg 2: Transfer chaeachristics

Fig3: @ PMOS based sabrealed load inventor

Here pros transistor gate is connected to the original burninal. Output arcises to a pthreehold trom down from MDD. PMOS is in salveation, too townsmalt vin deriver toanvietor is in salveation.

I DS deiver = Boloiver (Vin-Vohn)

I osloed == Rhoad ( Vone - VDD- Ytp)

Vow Ipsload = - Inchairer

Vone = Voo + Kp + Tx (Vin-Vm).

k= Bdeiren - 02 males Rload

One more reasions of consented loved innearly 18 big & vohich used dipletion had nonosas as ellions in lood bohose gale is connected to theoutput Erminal. L'ana Streehold vo Hageis load ougaine hence output sièses to complife Upp and close to Zero- when Vinis

Turo and Upp nespectively althown in bignere 4 (b).

Vont Vin Lavier

155 VID Dight: Dypletion load ionewher

\_ > 2 malley

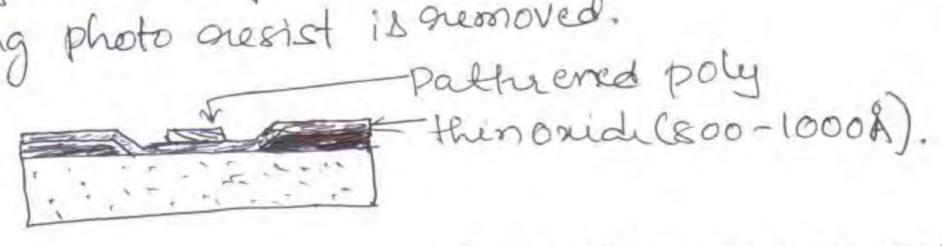

Explain the nMos baboication process with near sketches? wonite the steps involved in production (7m+3m)

-> NMOS buboication steps are outlined as bollones

· P-substable

Then wafer cut broom single carystal a silicon a high puaity 10 to which ptype impnaities are introduced. Thickness a the wafer is 0. 4 mm & a diameter of 75 to 150 mm.

Sion (19em)

A layer of Silicon dionide ofhickness them is grown to protect surface, acte as bassics to dopants during processing & provide insulating substrate onto which other layers to be deposited and pathaned.

3 The Alayer of photo resist is deposited onto the water and spun to achieve an even distribution of required thickness

Photo resist

Work Mask.

(4)

Photo resist layer & is then exposed to cultodight ultra violet light through a mask to define region into which diffusion take place, along with channel. Exposed areas of photo recid is polymerized. Areas required for diffusion are shielded by the mask.

if subsequently the areas not exposed to UV light are etched cuoayalong with the undulying silicon dioxide so that a voindow wafer surface is exposed in the window defined by the mails. Remerining photo aresist is nemoved.

A thin layer of silicon dioxide (0.1pm) is grown over untire chip and polysiticon is diposited on top to foom gate etructure. Polysilicon layer consists & heavily doped polysilicon deposited by chemical vapor deposition (CVD). Precise control of dopant concentra.

- Hon and thickness is necessary.

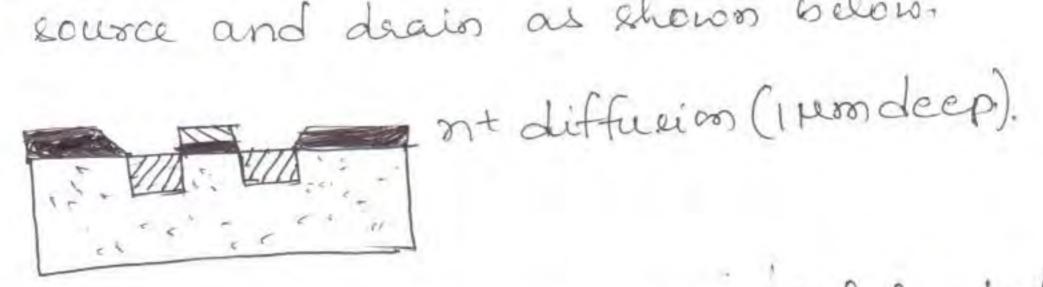

Further photorested and marking allows the polysiticon to be. paltured as shown above. then thin oxide is remove to expose. are so be differend. to form the source and drain as shown below.

Diffucion is a process in which wafer is healed, toakigh to a high temperature and paring a gas containing the designed n-type imposity over the surface, as Polyailiceonoith underlying thin oxide act as masks during diffusion process. This process is called self aligning.

Thick oxide grown allover again, then marked with photoseriet and etched to expose selected ageas of

the source and drain origions where Polysiticon gale and connections are to be made.

Metal is then deposited over the seveface to a thickness of I tem, this layer is then marked and clothed to boom the origined interconnection pattern.

- Of marles

### Production & E-beam marles

- 1) Stocking material is chrome plated glace places coated with E-beam sensitive nesit.

- 3 Et beam machine le loaded with mask description data (MEBES).

- 3 Plates are loaded Ento the E-beam machine where they are exposed with patterns specified by the cultomiss mark chaler

- (he) After exposure to the man E-beam, the plantes are Entroduced Ento the developer to bring out the the patterns left by the E-beam in the resist coaling.

- (5) Eyele This cycle followed by bake cycles and plasma descurring. which gremoves the Dicsist gresidue.

- The chrome is then etched and the plate is stripped of the gumaining, related and the plate is stripped of the gumaining, related and the plate is stripped.

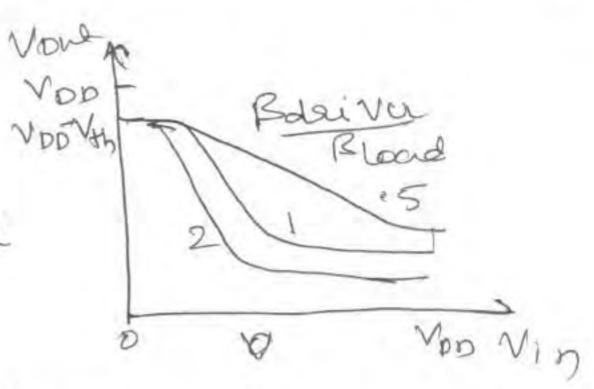

The segion of operation of the Mos transistor. Derive the selationship between Vin and Vone for segion C? Explain the effects of Bn Bp stabio versions on the transfer characteristics of cmos investor.

[6M+HM]

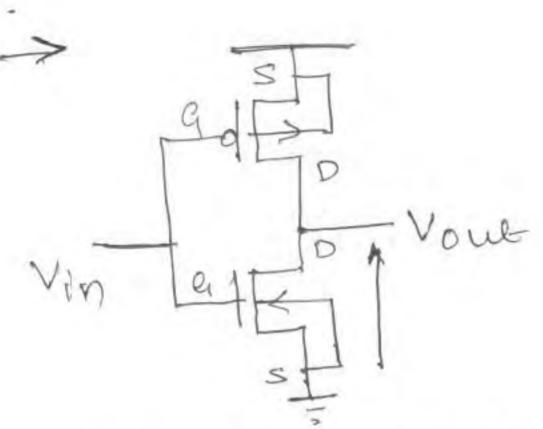

dig1. Cmos inventer.

The circuit diagram of cmos inventor is as shown in tignal 1.

fig 2: Derivation of cMos inventa characteristics

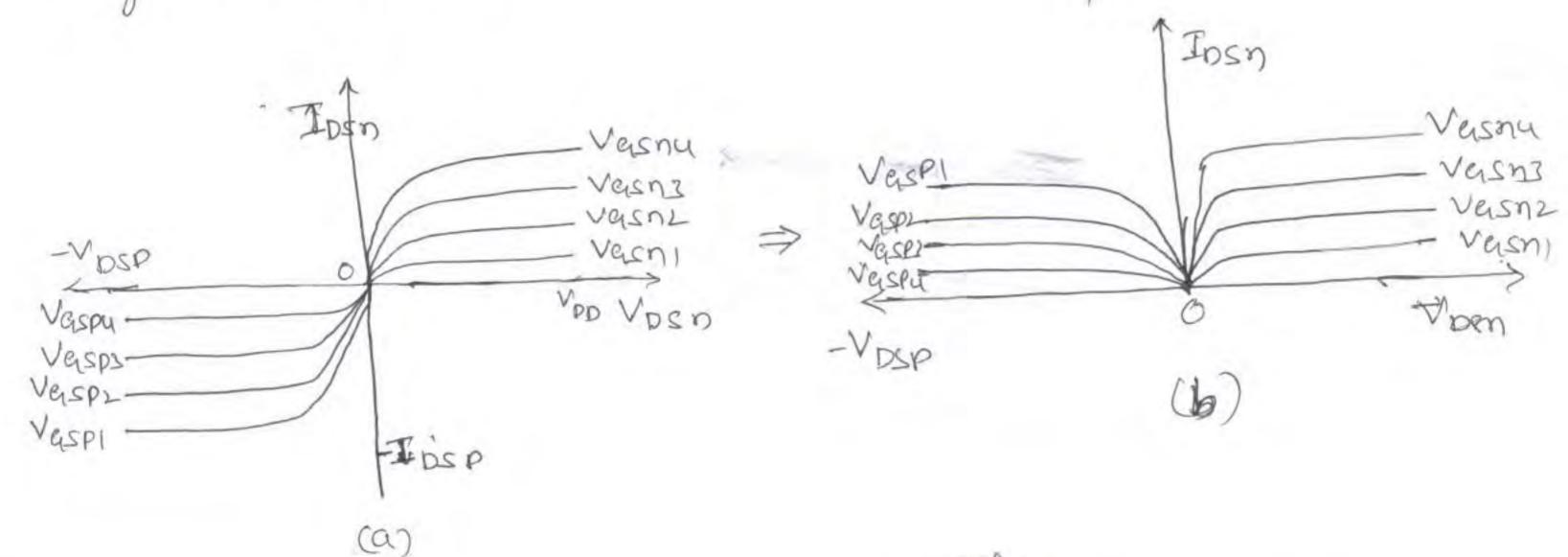

fig 2 a shows the comput graphical representations of the simple algebraic equations described below.

In linear auguson Pencox W (Verson-Venn) Vosn - Vosn )

IDSD = - PEDCOX W (Verson - Venn) Vosp - Vosp)

IDSD = - PEDCOX W (Verson - Venn) Vosp - Vosp)

In saluaction oregion

Tosn = Mencox 12 (Vasn-Vthon)<sup>2</sup>

Insp = sep Con 10 (Vasp Vtho)<sup>2</sup>

In Culgy oregion

IDSn=0; IDSp=0.

Fig 26 shows absolute value q the p-transistor drain current Ips hade to inverting 2 p-device charachoristics.

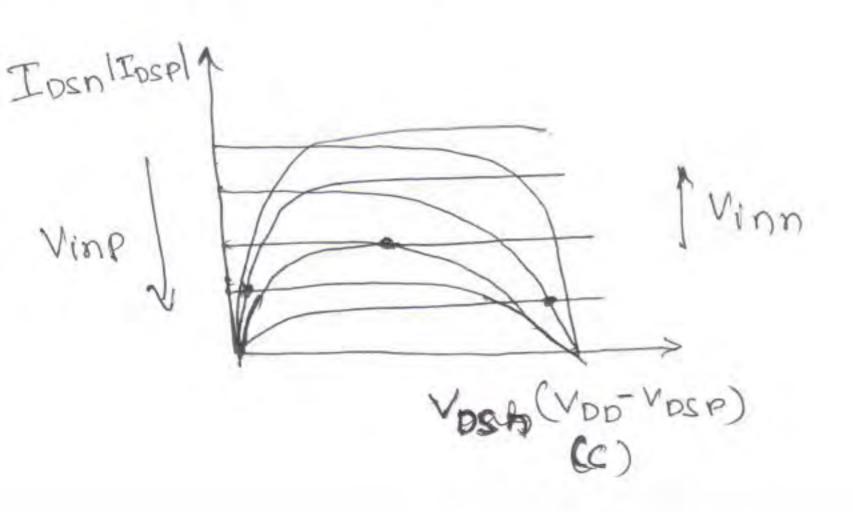

Fig 2 c shows the scepa imposed aurues of too transistor characteristics.

The input oneput chartoanster characteristics is determinted by the common vers intersection.

The intersection points in fig 2c for common vers gives the magnitude of current thowing in the circuit.

Replace optobling office imput a

Figure 2 D shows the greentant input enoput transfer. charachaistic q cmos inverter.

Opcobion of cmos Invala is devided into 5 origions. The stable of these pmos and nmos in the origions is given below

| Legion 8 | 20Mm      | PMOS      |

|----------|-----------|-----------|

| A        | cut gf    | linear.   |

| 13       | Salmalion | lineag.   |

| C        | Sahaalian | Salmalday |

| D        | linear    | sabralton |

|          | linear    | culast    |

- OH marles.

### Region C

we know that

By selling Bn= Bp and V4hn = -V4hp

Vin = Vop + V+1/p + (VB/n · - V4hp)

1 + VB/n

By

By

Selling Bn= Bp and V4hn = -V4hp

Region c exists only for one point.

Possible enange q Vont Dor nMOSFET:

Veson - Venn < Vosn Veg - Ne - Venn < Vo-Xs Vin - Venn < Voul - 3

200 PMOSPET

Vasp - Vthp > VDSP Va-ys - Vthp > VD-ys Vin - Vthp > Vont -3

cleing @ and 3

Vin-Ythn < Vone < Vin-Vthp

Region @ point is also ealled as inverter threehold denoted by Vinv

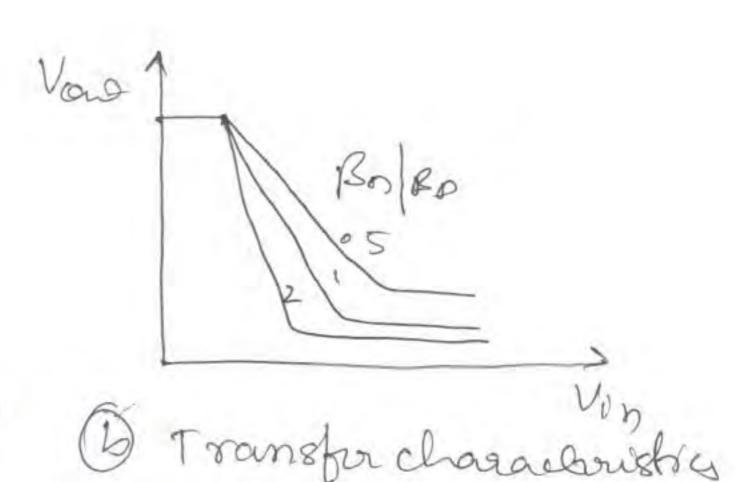

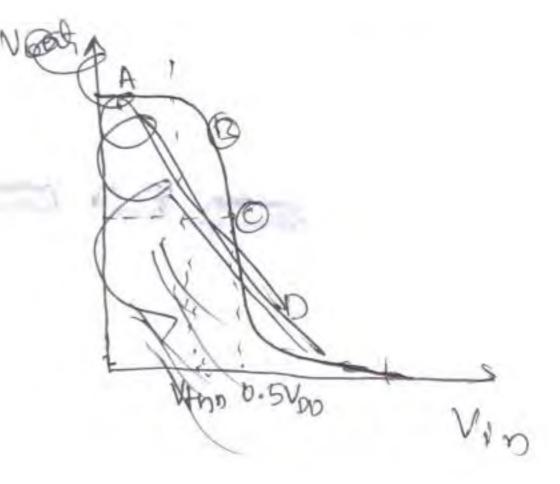

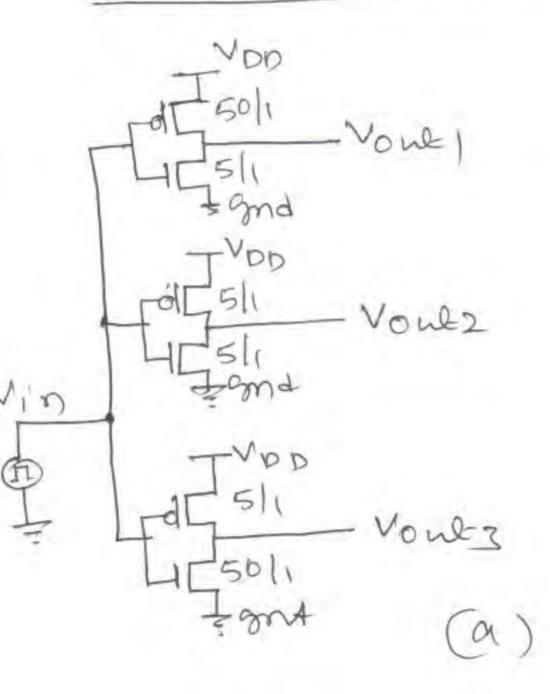

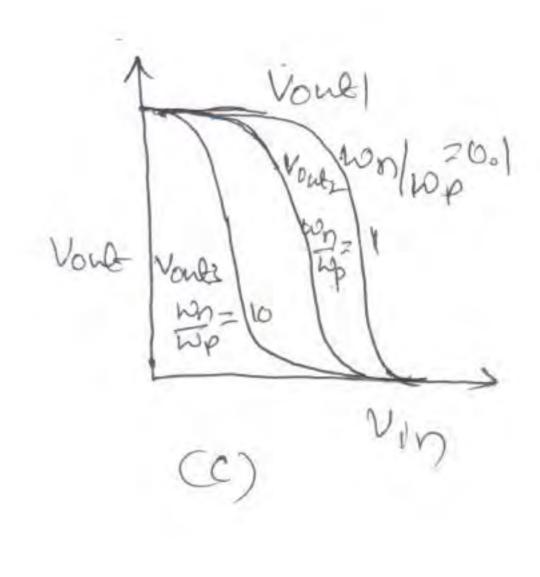

Bo/Bp Variations

Vous Vous 13n/Bp=0.1

Vous Vous 13n/Bp=0.1

Vin (b)

D2 marles

figure 3: circuit diagram & influence of Bn/Bp on Dc Transfer charachristic.

Gate threshold voltag vinv depends on Bn/Bp (5)

This is eveident from figure 3(6)4(C).

As Brigg Mceaux Vinval which Vin=Vout decreases.

Bon can be changed by changing the divice dimensions

Variations in DC transfir characturistics dece to leasialing in Rn/Rp and hence due to variation in top is shown in figure 3(b) and ic).

capacitive local to charge and descharge in egical times by providing equal current-squire and current-sink capabailities.

when Bn =1, allows the invester to charge and discharge the capacitive load in equal times by providing. the capacitive load in equal times by providing. equal current-sink capabilities.

when Bn >1 allows the invested to have more current spring capability sinking capability then current sourcing capability when Bn x1 invested will have high current sourcing when Bn x1 invested will have high current sourcing capability.

Capability than causene sinking capability.

As the temperature increases of the mos device increases the effective carrier mobility pe decreases. This results in a decrease in R. They are gulated as BOTTOS per T-1.5

01 marle

Mobility & both holes and electrons are similarly affected this gatio is independent à temperature to a good approximation.

Both Vtho and Vthp decrease slightly as temperature. Increases, and the extent of region A is reduced while the extent of Region Eincreases.

- 01 marles

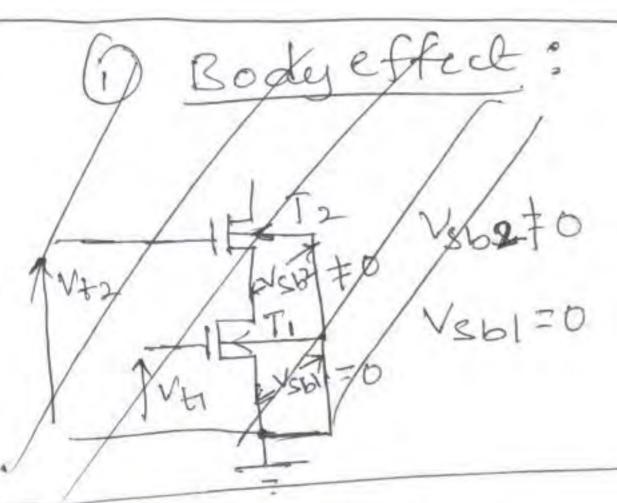

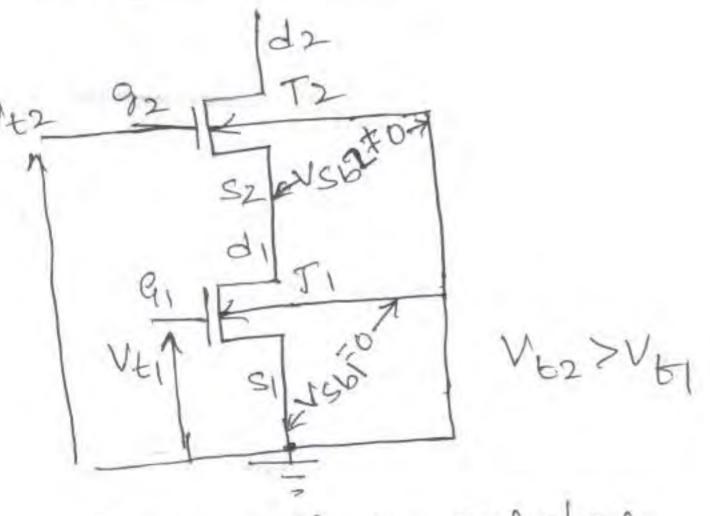

(8) Write a shoat notes on (1) Body effect, (6) - (SM+SM)

Bodyeffect.

Dig!: Effect à substrate bias on series connected n transictors.

All the devices are formed on asingle substrate. Therefore substrate voltage is nomally equal.

In some cases while arranging the transistors to tooma gerbing trundrons it migh be necessary to connect

Several devices in series as shown in Digner () (6)

Here source to substrate voltage for Ti transistr

i.e., VSb1=0 for T1

& VSb1=0 for T2.

Due to the non zero Vsb, as Vsb increases the width of the channel-substrate depletion layer also increases. Resulting in an increase in the done in the trapped coarical in depletion layer. For cheage newtrality to hold, channel charge must decrease. Results in increase in the gate-channel voltage drop lead & to increase in the schold voltage vince Vsb adds to the channel substrate junction potential.

i. The modified threshold voltage expression is

V46 = V46 + 266 + V2EsiQUNA(206+1V661)

Vt = Vtho + ~ ( \( \square 2\phi\_b + | \vec{1}{2} - \square 2\phi\_b \).

Vtho = thresheld voltage with some tosubstrate Voltage Vsb=0.

V= constant describes substrate bias effect.

Y= tox V29/EsiNA = Lox V29/EsiNA

Cox

\_\_\_osmales

Jaco

# (i) channel length modulation.

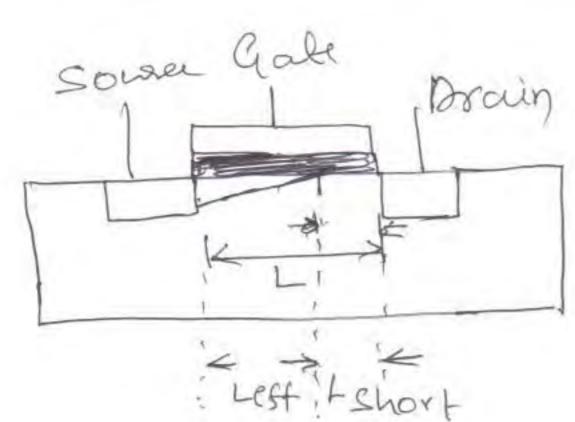

As devices are scaled down, Darialions in deain to source vollage leads to versialion & in of the effective length of the channel. This is called as channel length modulation.

Ideally the drain to somece angrent Ips in Salvadion on whould be independent of. Salvadion are scaled down Ips Vps. But as deviced are scaled down Ips depends on Vps. variations in Vps as given by

IDS = 1/2 1/2 (Vas-Vth) (1+2 VDS)

λ = channel length modulation factor

reasies has value in the gange 0.02 v to

0.005 v !

k = proces gain Dador = 128 tox

Effective channel length is

Leff = L-Lsnort

Lshort = \frac{2Esi}{QVNA} (VDS-(VQS-V4h))

Since

(7)

Thus nother than appearing as a constant current source with infinite output impedance, Mos device has binite output impedance.

- 05 marles